提供一站式 FPGA&嵌入式解决方案

# 盘古 100K MINI 开发板

## FPGA 通用实验指导手册

小眼睛科技 盘古 676 系列

盘古 100K MINI (MES2L676-100HP-MINI-MINI-MINI) 开发板实验教程

紫光同创 Logos2 系列 PG2L100H 开发平台

## 文档版本修订记录

| 版本号  | 发布日期       | 修订记录 |

|------|------------|------|

| V1.0 | 2025/10/20 | 初始版本 |

公司名称: 深圳市小眼睛科技有限公司

地址: 深圳市宝安区西乡街道 F518 时尚创意园

官方网址: [www.meyesemi.com](http://www.meyesemi.com)

官方淘宝店铺: 小眼睛半导体

B 站: 小眼睛半导体 (视频教程免费学)

\* 加入 FPGA 开发者技术交流与 5000+ FPGA 开发者实时沟通

QQ2 群: 442106123 QQ3 群: 882634519)

\* 配套资料下载、技术答疑请登录逻辑矩阵技术论坛

逻辑矩阵技术论坛欢迎各位发烧友加入

让我们共建开源生态, 持续赋能行业发展

<https://www.szlogicmatrix.com/>

\* 扫码注册开源技术论坛

\* 扫一扫关注官微

\* 淘宝官方旗舰店

# 目录

|        |                              |        |

|--------|------------------------------|--------|

| 1.     | FPGA 开发工具使用 .....            | - 1 -  |

| 1.1.   | 实验简介 .....                   | - 1 -  |

| 1.2.   | 实验原理 .....                   | - 1 -  |

| 1.2.1. | PDS 软件的安装 .....              | - 1 -  |

| 1.2.2. | PDS 工具的使用 .....              | - 20 - |

| 2.     | Modelsim 的使用和 do 文件编写 .....  | - 21 - |

| 2.1.   | 实验简介 .....                   | - 21 - |

| 2.2.   | 实验原理 .....                   | - 21 - |

| 2.3.   | 接口列表 .....                   | - 21 - |

| 2.4.   | Testbench 文件的编写 .....        | - 21 - |

| 2.5.   | Modelsim 的使用 .....           | - 23 - |

| 2.6.   | 文件的编写 .....                  | - 34 - |

| 2.6.1. | 基本命令介绍 .....                 | - 34 - |

| 2.6.2. | 文件示例 .....                   | - 35 - |

| 3.     | Pango 与 Modelsim 的联合仿真 ..... | - 39 - |

| 3.1.   | 实验简介 .....                   | - 39 - |

| 3.2.   | 实验原理 .....                   | - 39 - |

| 3.2.1. | 编译仿真库 .....                  | - 39 - |

| 3.2.2. | 设置仿真路径 .....                 | - 41 - |

| 3.2.3. | 启动联合仿真 .....                 | - 43 - |

| 4.     | 紫光同创 IP core 的使用及添加 .....    | - 45 - |

| 4.1.   | 实验简介 .....                   | - 45 - |

| 4.2.   | 实验原理 .....                   | - 45 - |

| 4.2.1. | IP 的安装 .....                 | - 45 - |

| 4.2.2. | 例化 IP 及查看 IP 手册 .....        | - 49 - |

| 5.     | Pango 的时钟资源--锁相环 .....       | - 54 - |

| 5.1.   | 实验目的 .....                   | - 54 - |

| 5.2.   | 实验原理 .....                   | - 54 - |

| 5.2.1. | PLL 介绍 .....                 | - 54 - |

| 5.2.2. | IP 配置 .....                  | - 54 - |

| 5.3.   | 代码设计 .....                   | - 57 - |

| 5.4.   | PDS 与 Modelsim 联合仿真 .....    | - 60 - |

---

|         |                                |         |

|---------|--------------------------------|---------|

| 5.5.    | 实验现象 .....                     | - 62 -  |

| 6.      | Pango 的 ROM、RAM、FIFO 的使用 ..... | - 62 -  |

| 6.1.    | 实验简介 .....                     | - 62 -  |

| 6.2.    | 实验原理 .....                     | - 63 -  |

| 6.2.1.  | RAM 介绍 .....                   | - 63 -  |

| 6.2.2.  | FIFO 介绍 .....                  | - 70 -  |

| 6.3.    | 接口列表 .....                     | - 75 -  |

| 6.4.    | 工程说明 .....                     | - 76 -  |

| 6.5.    | 代码仿真说明 .....                   | - 76 -  |

| 6.5.1.  | RAM 仿真测试 .....                 | - 76 -  |

| 6.5.2.  | ROM 仿真测试 .....                 | - 79 -  |

| 6.5.3.  | FIFO 仿真测试 .....                | - 81 -  |

| 7.      | 基于紫光 FPGA 的键控 LED 流水灯 .....    | - 85 -  |

| 7.1.    | 实验简介 .....                     | - 85 -  |

| 7.2.    | 实验原理 .....                     | - 85 -  |

| 7.3.    | 接口列表 .....                     | - 86 -  |

| 7.4.    | 工程说明 .....                     | - 87 -  |

| 7.5.    | 代码模块说明 .....                   | - 87 -  |

| 7.6.    | 代码仿真 .....                     | - 88 -  |

| 7.7.    | 实验步骤 .....                     | - 90 -  |

| 7.7.1.  | 打开 PDS 软件, 创建工程 .....          | - 90 -  |

| 7.7.2.  | 添加设计文件 .....                   | - 96 -  |

| 7.7.3.  | 编译 .....                       | - 100 - |

| 7.7.4.  | 工程约束 .....                     | - 101 - |

| 7.7.5.  | 综合 .....                       | - 103 - |

| 7.7.6.  | Device Map .....               | - 104 - |

| 7.7.7.  | Place & Route .....            | - 104 - |

| 7.7.8.  | Generate Bitstream .....       | - 105 - |

| 7.7.9.  | 下载生成的位流文件 .....                | - 105 - |

| 7.7.10. | 上板验证 .....                     | - 112 - |

| 8.      | 基于紫光 FPGA 的 UART 串口通信 .....    | - 114 - |

| 8.1.    | 实验简介 .....                     | - 114 - |

| 8.2.    | 实验原理 .....                     | - 114 - |

| 8.2.1.  | 串口原理 .....                     | - 114 - |

|                                 |         |

|---------------------------------|---------|

| 8.2.2. 串口发送字符 .....             | - 116 - |

| 8.2.3. 串口接收数据点灯 .....           | - 116 - |

| 8.3. 接口列表 .....                 | - 116 - |

| 8.4. 工程说明 .....                 | - 118 - |

| 8.5. 代码模块说明 .....               | - 118 - |

| 8.5.1. 串口发送模块 .....             | - 119 - |

| 8.5.2. 串口接收模块 .....             | - 120 - |

| 8.5.3. 工程及现象 .....              | - 123 - |

| 8.6. 在线 Debugger 工具的使用 .....    | - 125 - |

| 8.6.1. Fabric 工具说明 .....        | - 125 - |

| 8.6.2. Fabric 工具使用 .....        | - 126 - |

| 9. DDR3 读写实验例程 .....            | - 130 - |

| 9.1. 实验简介 .....                 | - 130 - |

| 9.2. 实验原理 .....                 | - 130 - |

| 9.2.1. DDR3 控制器简介 .....         | - 130 - |

| 9.3. 工程说明 .....                 | - 130 - |

| 9.3.1. DDR3 读写 Example 工程 ..... | - 131 - |

| 9.4. 实验现象 .....                 | - 141 - |

| 10. HDMI 回环实验 .....             | - 141 - |

| 10.1. 实验简介 .....                | - 141 - |

| 10.2. 实验原理 .....                | - 141 - |

| 10.2.1. 显示原理 .....              | - 142 - |

| 10.2.2. HDMI_PHY 配置 .....       | - 143 - |

| 10.3. 接口列表 .....                | - 143 - |

| 10.4. 工程说明 .....                | - 144 - |

| 10.5. 代码模块说明 .....              | - 145 - |

| 10.6. 实验现象 .....                | - 150 - |

| 11. 基于 UDP 的以太网传输实验例程 .....     | - 151 - |

| 11.1. 实验简介 .....                | - 151 - |

| 11.2. 开发板以太网接口简介 .....          | - 151 - |

| 11.3. 实验要求 .....                | - 151 - |

| 11.4. 以太网协议简介 .....             | - 151 - |

| 11.4.1. 以太网帧格式 .....            | - 151 - |

| 11.4.2. ARP 数据报格式 .....         | - 152 - |

|         |                         |         |

|---------|-------------------------|---------|

| 11.4.3. | IP 数据包格式 .....          | - 153 - |

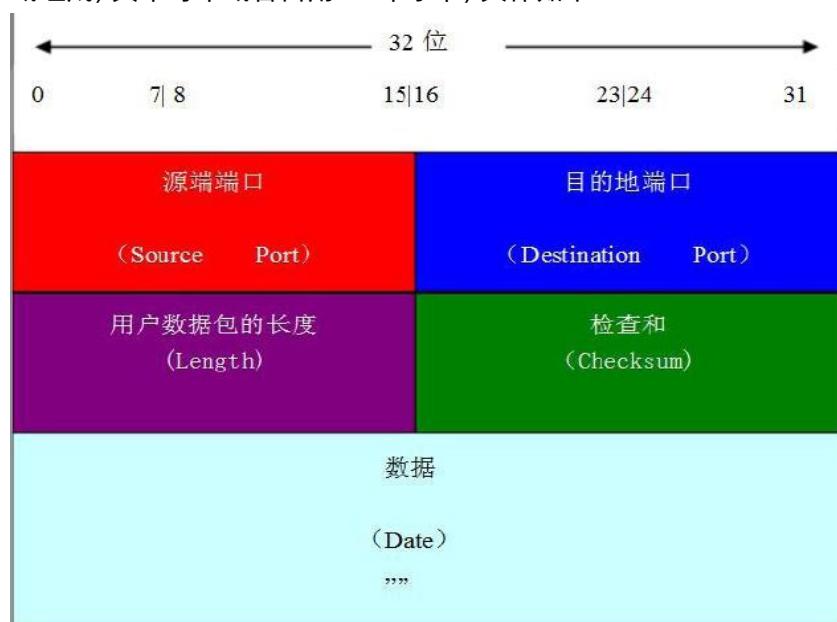

| 11.4.4. | UDP 协议 .....            | - 154 - |

| 11.4.5. | Ping 功能 .....           | - 156 - |

| 11.5.   | SMI(MDC/MDIO)总线接口 ..... | - 156 - |

| 11.5.1. | SMI 帧格式 .....           | - 156 - |

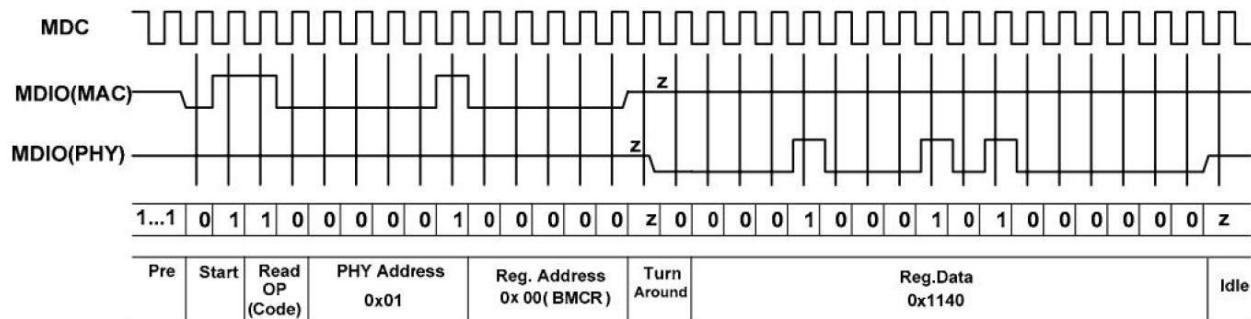

| 11.5.2. | 读时序 .....               | - 157 - |

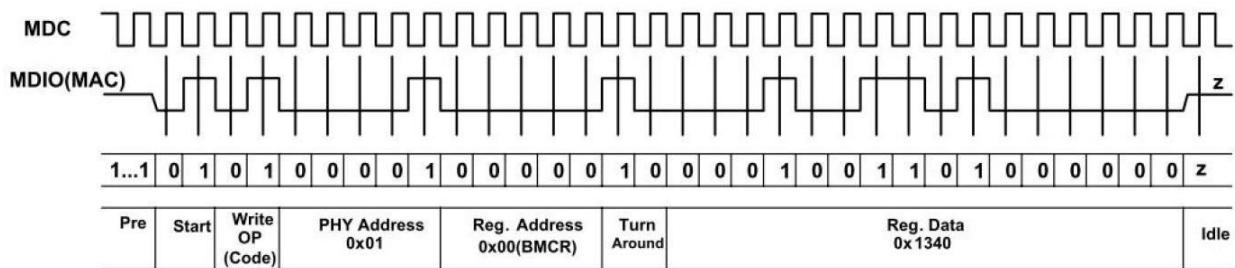

| 11.5.3. | 写时序 .....               | - 157 - |

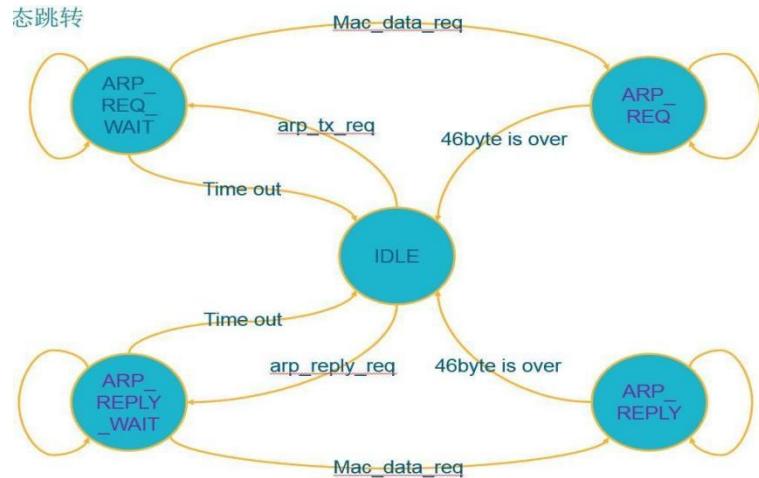

| 11.6.   | 实验设计 .....              | - 158 - |

| 11.6.1. | 发送部分 .....              | - 158 - |

| 11.6.2. | 接收部分 .....              | - 163 - |

| 11.6.3. | 其他部分 .....              | - 167 - |

| 11.6.4. | 实验现象 .....              | - 168 - |

# 1. FPGA 开发工具使用

## 1.1. 实验简介

实验目的:

了解 PDS 软件的使用, 在线 Debugger 工具的使用请看 uart 实验章节的工程说明部分章节。

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP-MINI

## 1.2. 实验原理

### 1.2.1.PDS 软件的安装

#### 1.2.1.1. 软件简介

Pango Design Suite 是紫光同创基于多年 FPGA 开发软件技术攻关与工程实践经验而研发的一款拥有国产自主知识产权的大规模 FPGA 开发软件, 可以支持千万门级 FPGA 器件的设计开发该软件支持工业界标准的开发流程, 可实现从 RTL 综合到配置数据流生成下载的全套操作。

#### 1.2.1.2. 支持平台

| 软件工具                       | Windows 操作系统     |

|----------------------------|------------------|

| ADS 综合工具、OEM 综合工具、PDS 后端工具 | Windows 7,10,11、 |

#### 1.2.1.3. 软件安装

所有版本的安装均一致, 一般地, 例如PDS\_2022.1版本可将软件安装在C:\pango\PDS\_2022.1 (软件默认安装路径), 若选择自定义安装路径需注意路径不可出现中文和特殊字符。软件安装完成后, 会在桌面以及程序菜单中添加快捷方式 PangoDesign Suite2022.1; 在程序菜单 Pango Design Suite2022.1 文件夹中包含 Pango Design Suite、软件卸载的快捷方式 Uninstall、程序附件 Accessories 以及软件文档 Documents。

本章节安装流程以 Pango Design Suite 2022.1 Windows 版本安装进行说明, 下面将详细介绍PDS安装过程。

#### 1.2.1.4. 安装程序

首先关闭电脑所有杀毒软件, 否则杀毒软件有可能会拦截一些组件, 造成安装失败或功能缺失等不确定结果;

双击安装包中的安装程序 Setup.exe, 启动安装程序:

图 1.2-1

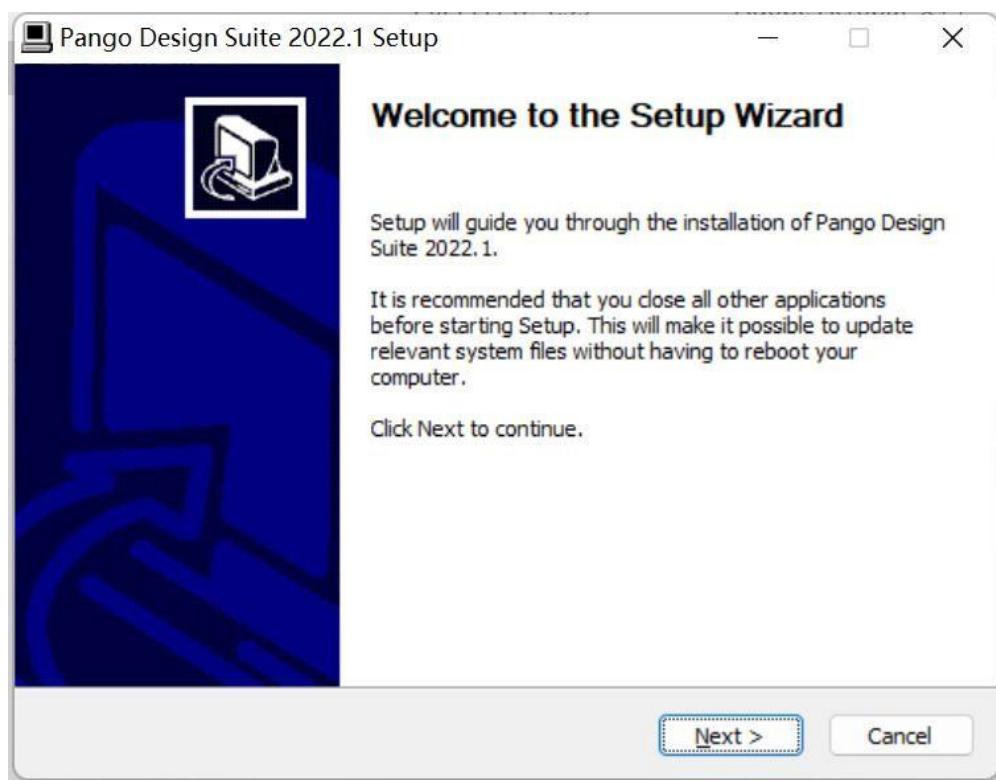

启动安装程序后的界面如下:

图 1.2-2

点击“Next”，跳转至许可协议对话框：

图 1.2-3

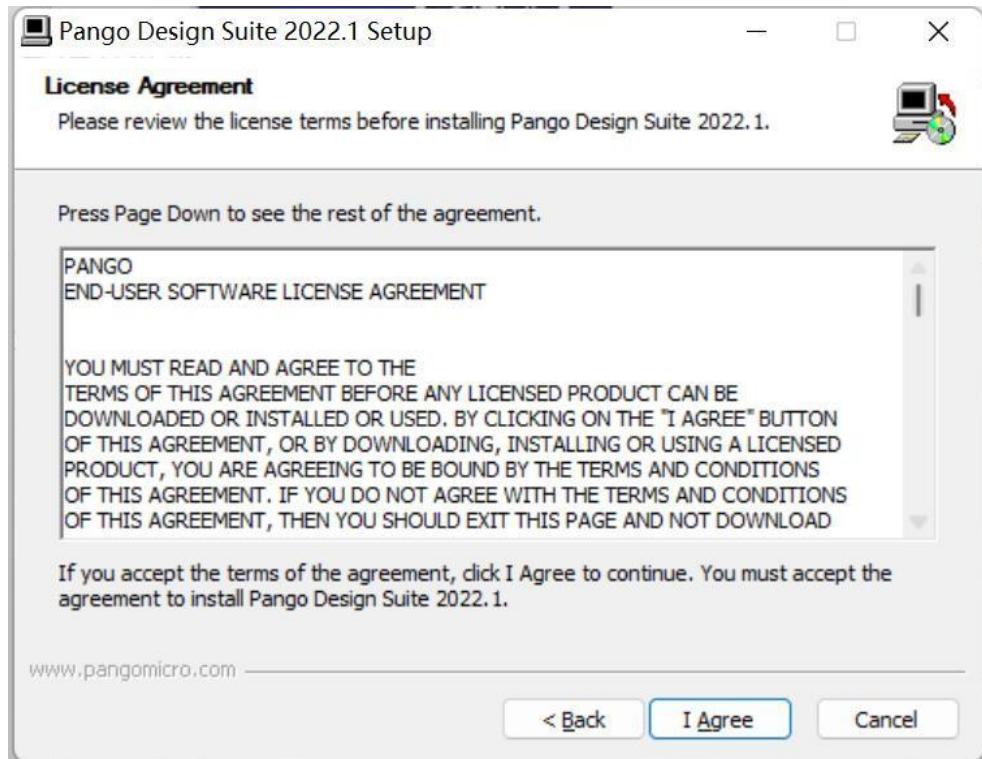

选择接受许可协议，点击“*I Agree*”按钮，进入选择安装路径选择框，如下图所示，默认安装路径为 C:\pango\PDS\_2022.1，建议采用默认路径，若使用自定义安装路径需注意路径不要出现中文和特殊字符。

图 1.2-4

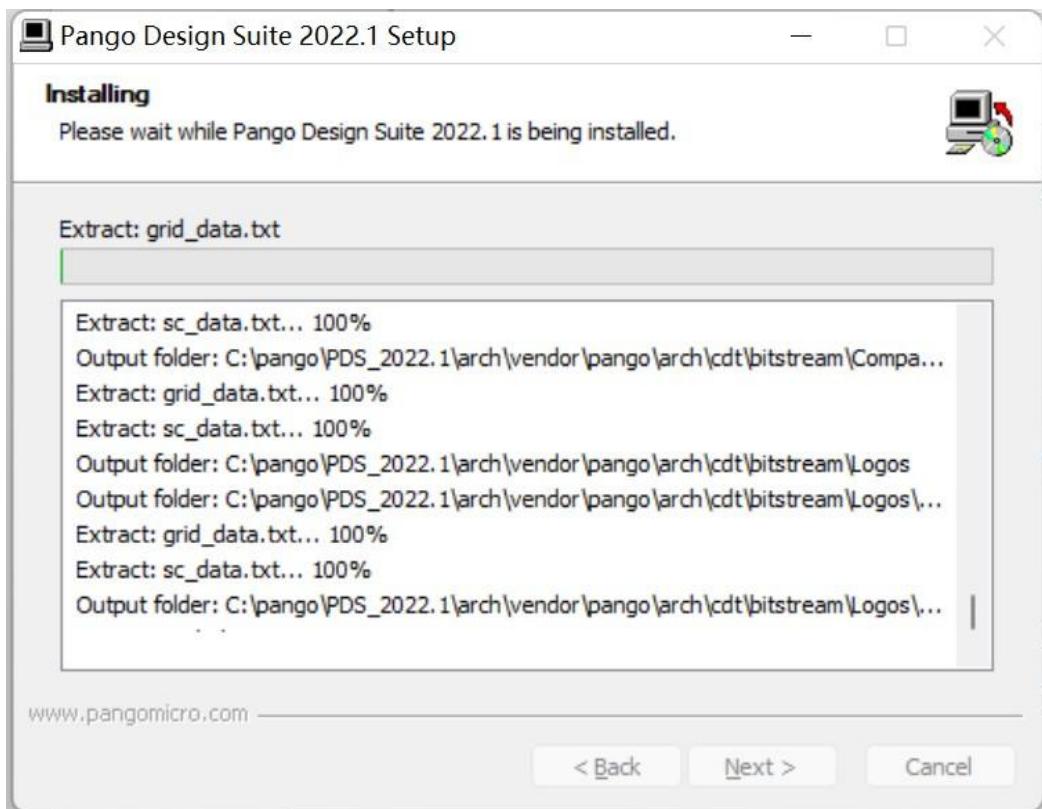

直接点击“Install”，则跳转到安装界面。

图 1.2-5

耐心等待至完成全部安装过程, 点击“Finish”, 安装完毕。

图 1.2-6

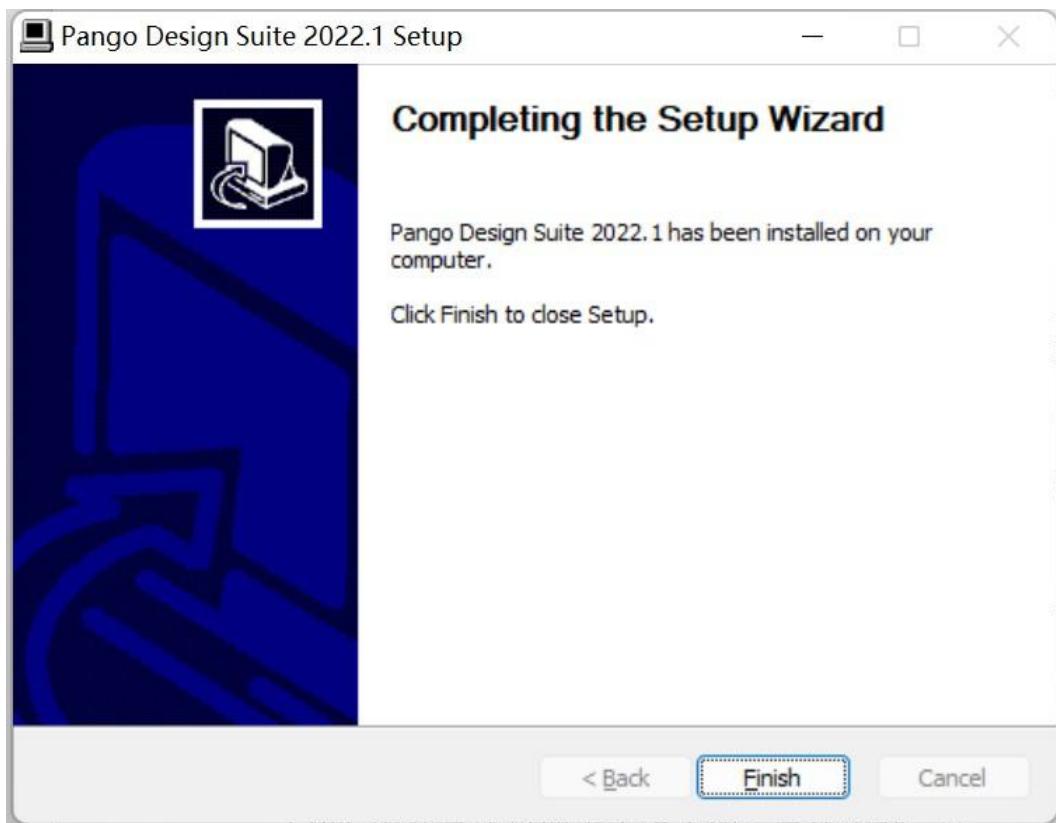

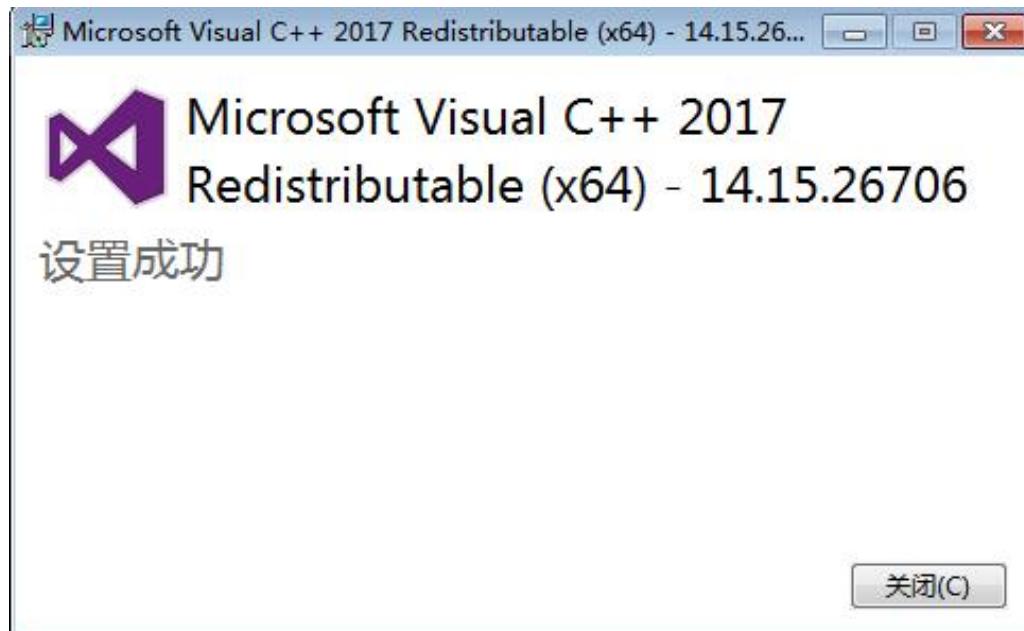

安装完成后,会提示是否需要安装运行库 vcredist\_VS2017.exe。若电脑之前未安装过则需要安装此运行库后才能运行 PDS, 点击“是”按钮进行安装; 若电脑之前已安装过此运行库则无需再次安装, 点击“否”按钮不进行安装即可。(如果没有这个提示, 可以不管)

注: 如果不确定, 建议点击“是”进行安装, 否则可能导致 PDS 无法运行。

图 1.2-7

点击“是”进入运行库安装界面, 选择同意许可条款和条件, 点击安装按钮进行安装。

图 1.2-8

安装完成界面点击“关闭”完成安装。

图 1.2-9

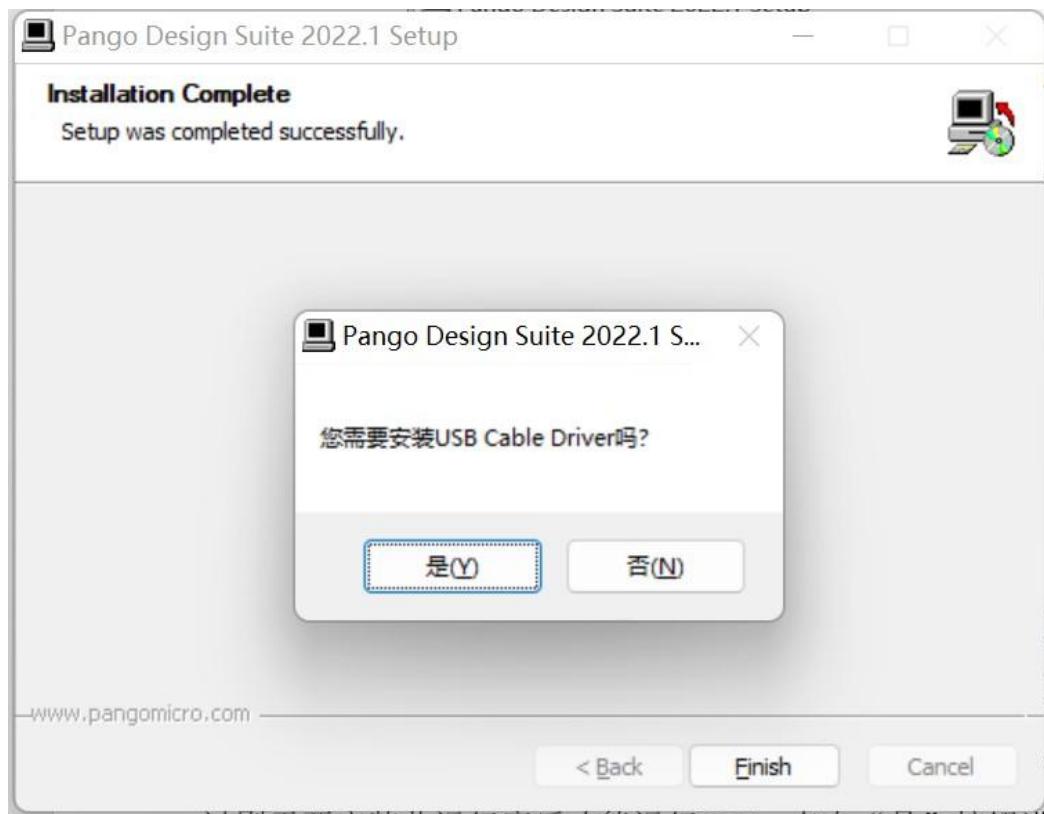

完成安装后, 会提示是否需要安装 USB Cable Driver。安装点击“是”, 否则可能导致下载器无法正常使用。

图 1.2-10

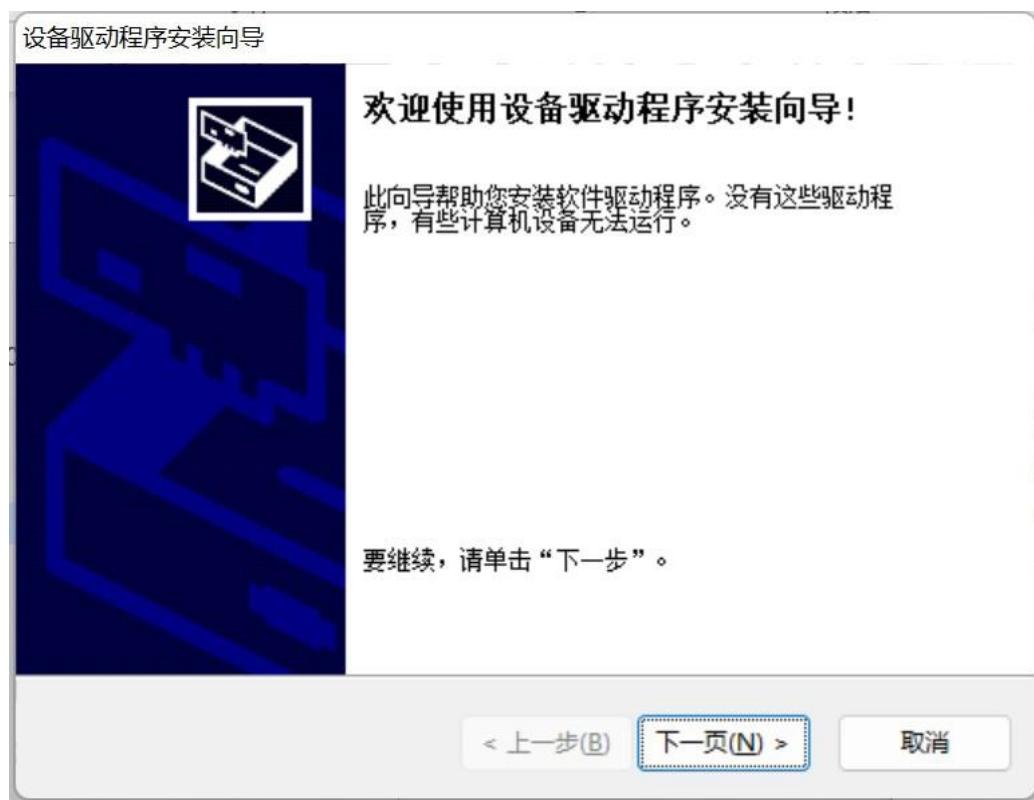

点击“是”进入驱动程序安装界面：

图 1.2-11

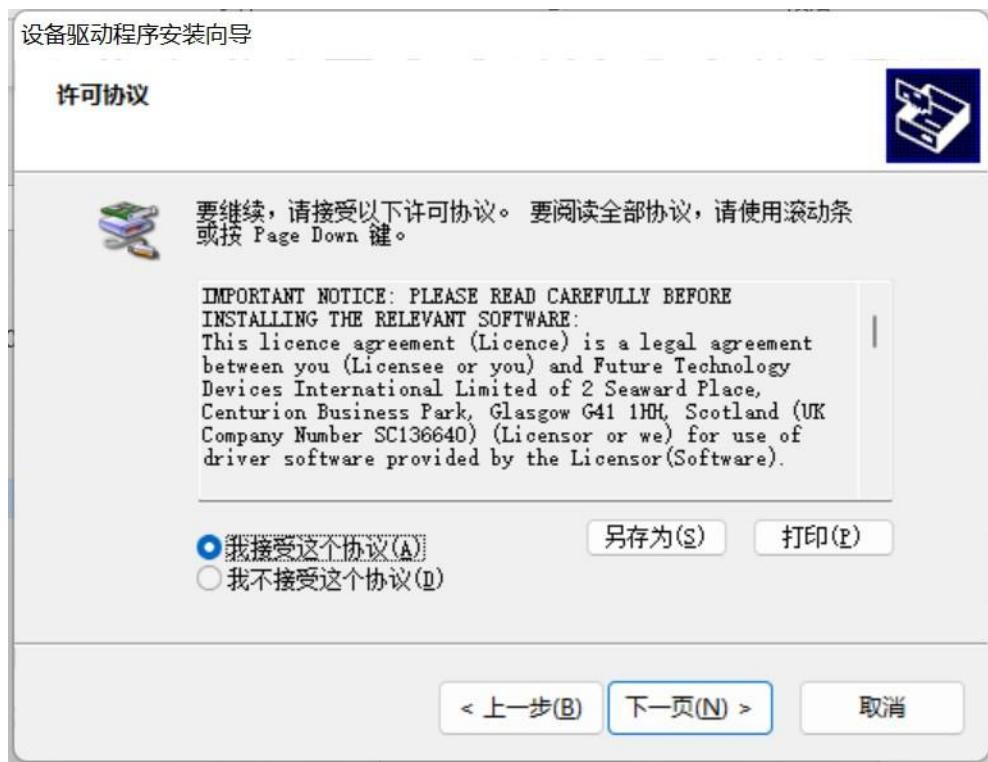

点击“下一步”进入安装驱动程序许可协议界面。点击“我接受这个协议”，然后点击“下一步”。

图 1.2-12

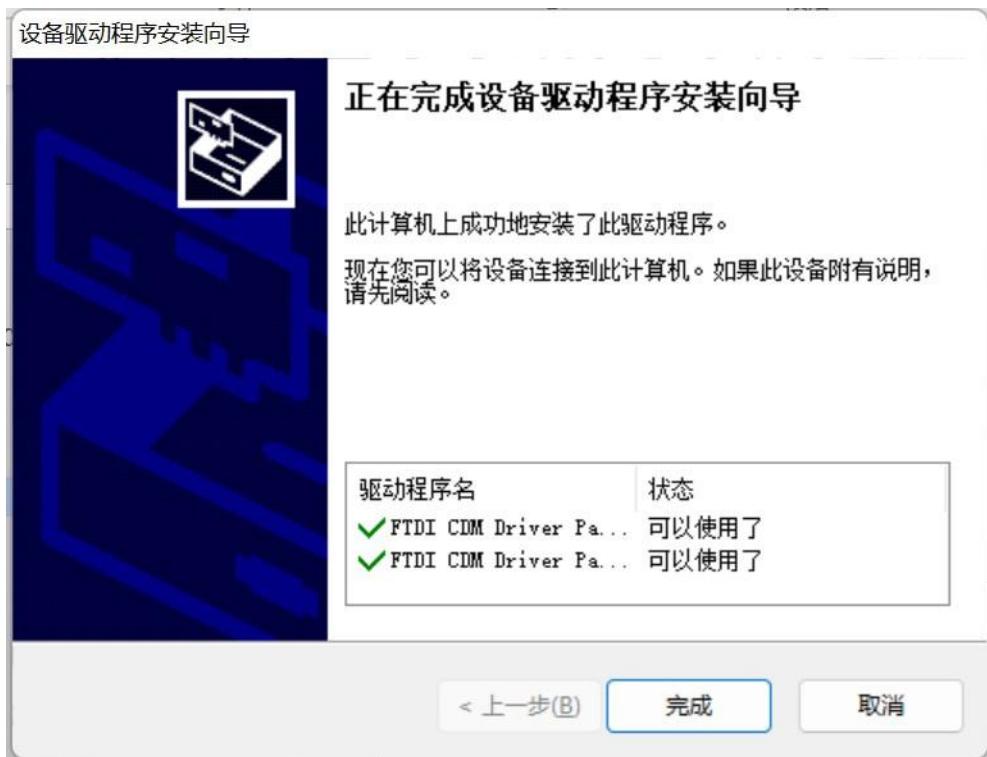

点击“完成”，完成驱动程序的安装。

图 1.2-13

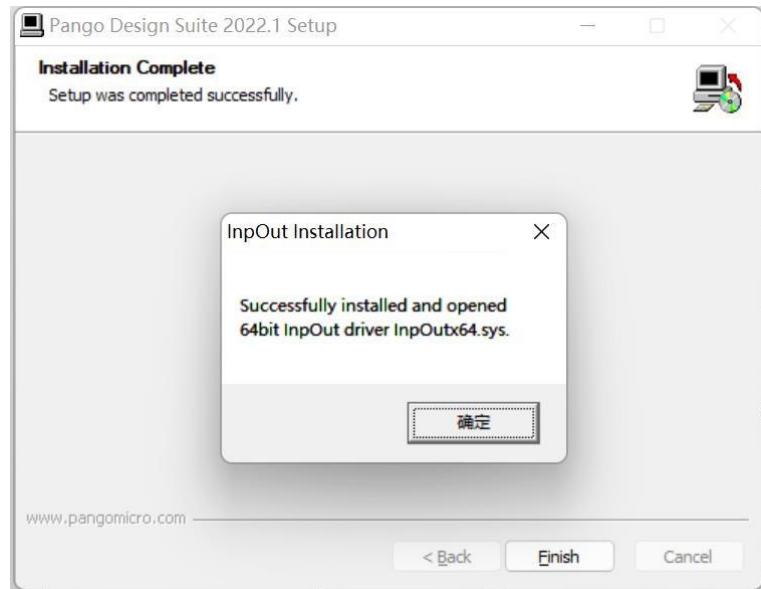

完成安装后, 会提示是否需要安装 ParallelPortDriver。安装点击“是”。

图 1.2-14

点击“是”进行并口驱动程序安装。

图 1.2-15

完成后点击“确定”，结束安装。在桌面上看到如下图标：

图 1.2-16

### 1.2.1.5. License 关联, 环境变量设置

软件完成安装后, Pango Design Suite 需要 License 文件才能正常使用, 若安装 Lite 版本软件无需 License。License 文件可联系相关供应商或客服获取。

本教程使用软件版本开发语言支持 Verilog, 若使用 VHDL 需更新支持 VHDL 的软件版本

为方便管理 license 文件, 建议在 PDS 软件安装目录下新建一个 license 文件夹存放 license 文件。

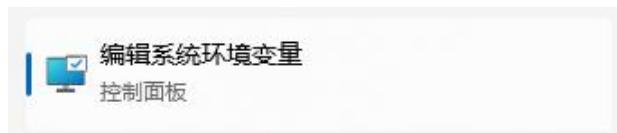

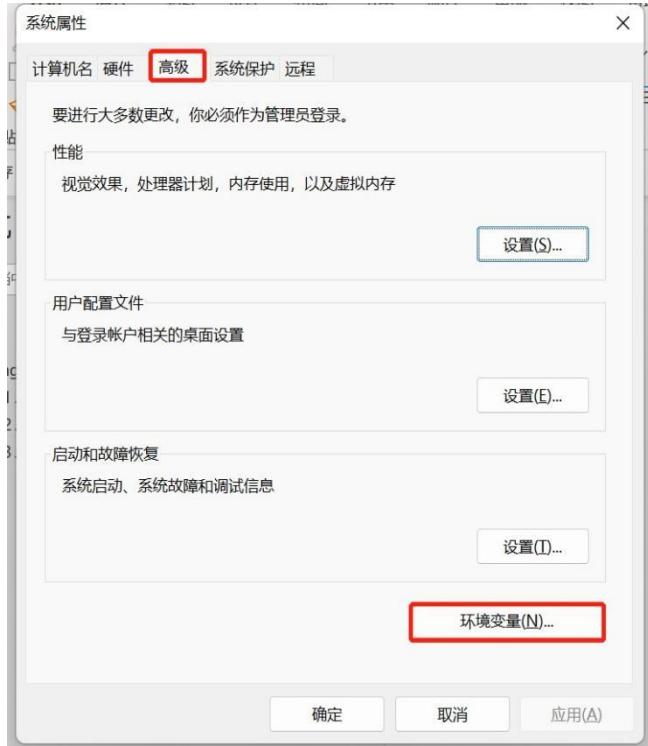

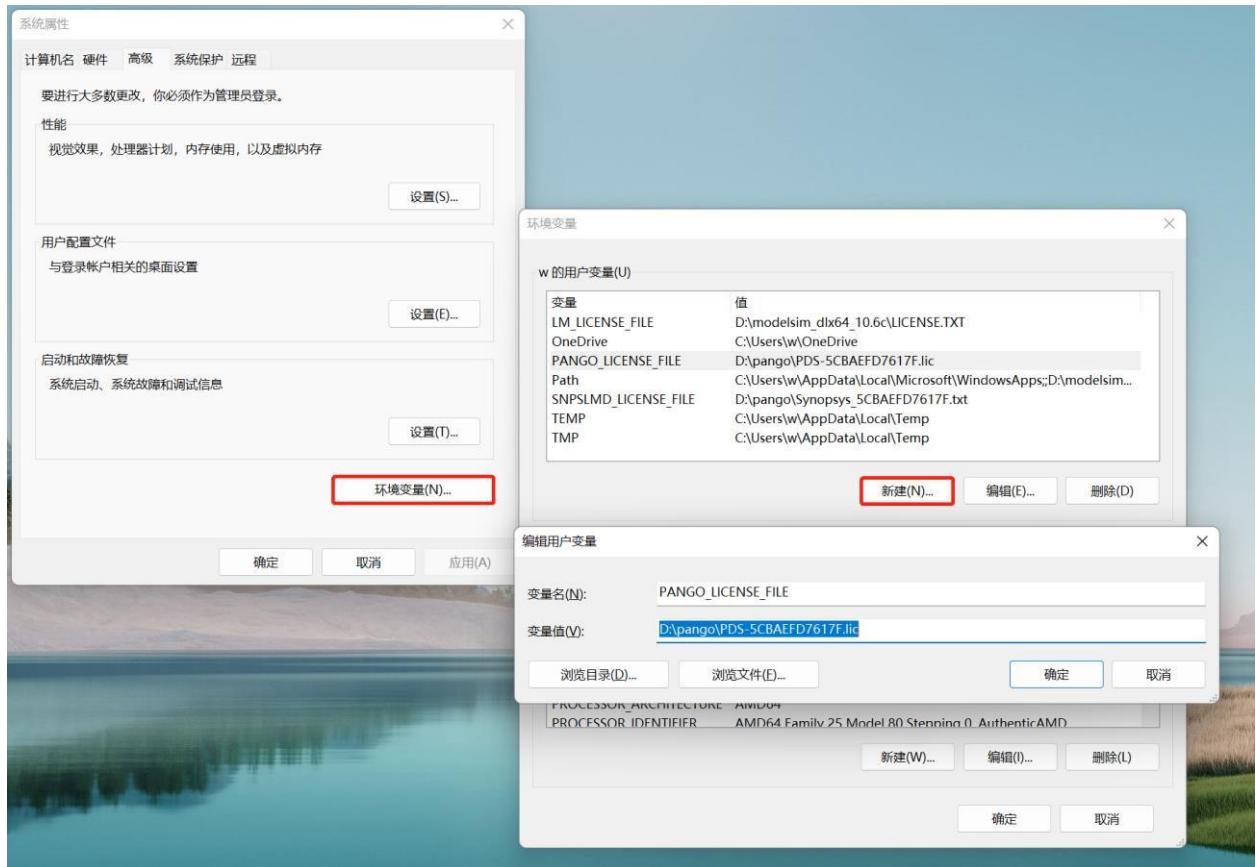

首先在电脑上打开运行窗口(win+r), 接着在窗口内输入 sysdm.cpl 然后回车。在系统属性界面内选择高级, 然后点击环境变量, 进行设置。

图 1.2-17

或者直接打开系统环境变量

图 1.2-18

### 1.2.1.6. PDS license 环境变量设置

若PDS license 文件路径为:D:\pango\license\pds\_node-locked.lic直接设置

环境变量:

变量名: PANGO\_LICENSE\_FILE

变量值: D:\pango\license\pds\_node-locked.lic

图 1.2-19

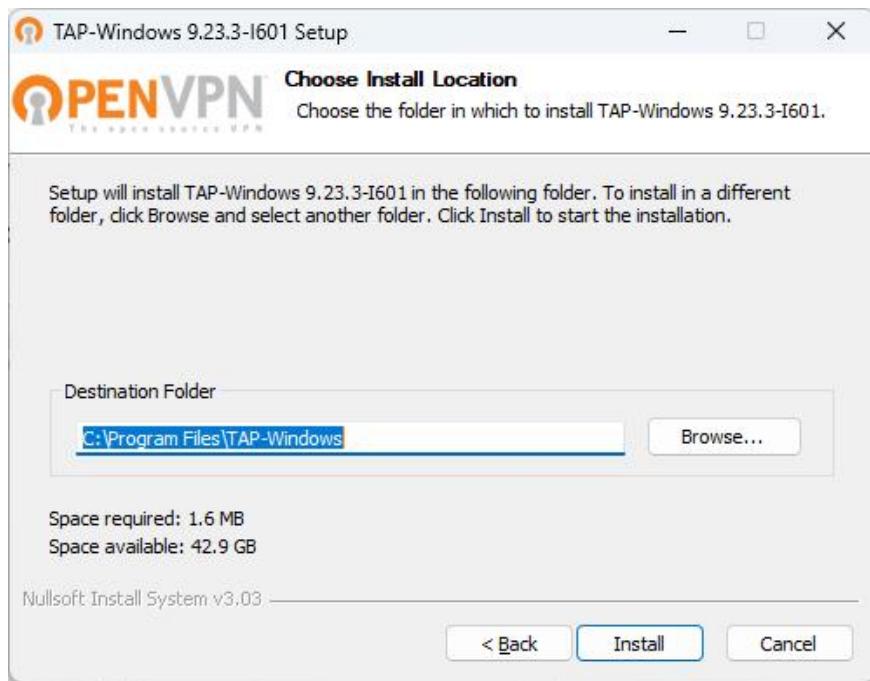

如果使用开发板资料提供的通用License,还需要安装tap-windows软件。其主要作用是用来生成虚拟网卡, 具体如下所示:

图 1.2-20

双击运行, 全部保持默认。

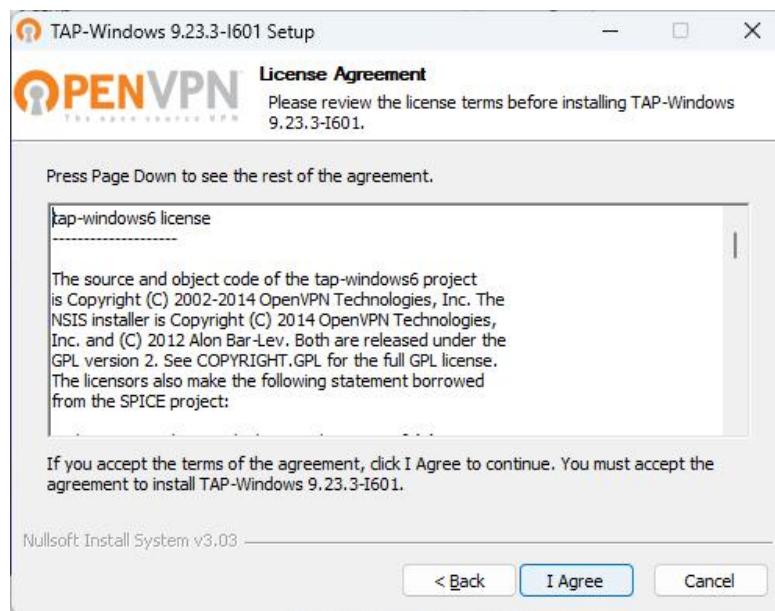

图 1.2-21

点击 Next。

图 1.2-22

点击 I Agree。

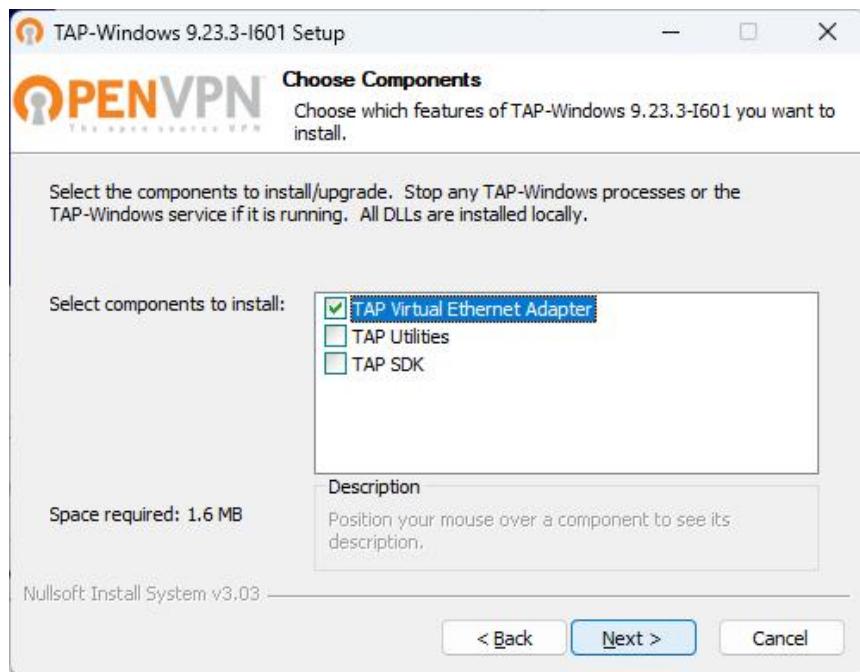

图 1.2-23

保持默认, 点击 Next。

图 1.2-24

安装路径保持默认, 点击 Install, 等待安装完成。

图 1.2-25

点击Finish, 至此, 安装完成。

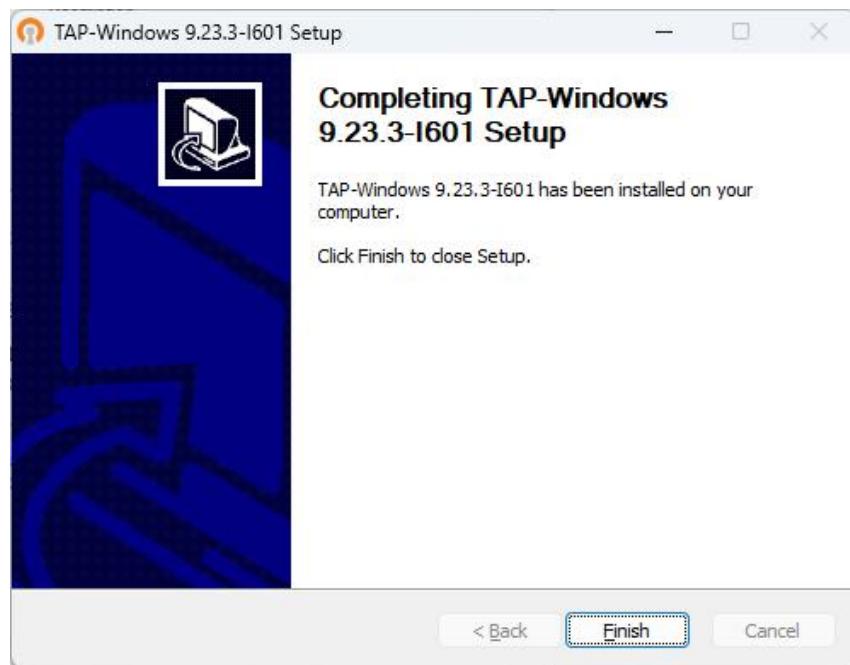

打开设备管理器, 在网络适配中找到TAP-Windows Adapter V9, 并双击。

图 1.2-26

图 1.2-27

选择属性选项卡，并将 MAC Address 的值改成 Lincese 文件名后面的字符串。

### 1.2.2.PDS 工具的使用

详见开发板配套资料《PDS 快速使用手册》文档,或软件安装目录 doc 文件夹下《Pango\_Design\_Suite\_Quick\_Start\_Tutorial.pdf》和《Pango\_Design\_Suite\_User\_Guide.pdf》。

## 2. Modelsim 的使用和 do 文件编写

### 2.1. 实验简介

实验目的:

了解 Modelsim 的基本使用方法, 完成 do 文件的编写, 提高仿真效率。

实验环境:

Window11

PDS2022.2-SP6.4

Modelsim10.6c

### 2.2. 实验原理

将 Modelsim 的命令编写到一个 do 文件中, 这样每次仿真时, 只需运行这个 do 文件脚本即可自动执行其中的所有命令, 从而显著提高重复仿真的效率。

### 2.3. 接口列表

暂无

### 2.4. Testbench 文件的编写

Testbench 文件其实就是模拟信号的生成, 给我们所设计的模块提供输入, 以便测试。因为我们上板去生成比特流, 尤其是比较复杂的算法, 往往是需要耗很多时间的。所以要快速验证我们的设计逻辑是否正常, 还得是用仿真来验证, 不管是模拟图像的生成还是信号的生成, 都可以通过 Testbench 来完成, 但是, 要注意一点, 逻辑前仿真通过了只能说明 80% 上板没问题, 剩下的可能就要看实际的时序了, 毕竟仿真只是理想状态, 实际总是不太理想。

接下来介绍 Testbench 的基本编写方法:

`timescale 1ns/1ns 该语句 第一个 1ns 表示时间单位为 1ns, 第二个 1ns 表示时间精度为 1ns。注意的是, 时间单位不能比时间精度还小。时间单位表示运行一次仿真所用的时间。时间精度表示仿真显示的最小刻度。

#10 表示延时 10 个单位时间, 比如`timescale 1ns/1ns, #10 表示延时 10ns。

initial 对信号进行初始化, 只会执行一次。

`\${random}%x, 表示随机取[0,x-1]之间的数字。x 为正整数。如果是\${random%x, 则是[-(x-1),x-1]的数。

\$display 打印信息, 会自动换行。

\$stop 暂停仿真。

\$readmemb 读取文件函数。

\$monitor 为监测任务, 用于变量的持续监测。只要变量发生了变化,\$monitor 就会打印显示出对应的信息。

输入信号一般用 reg 定义, 方便后续用 always 块生成想要模拟的值, 输出一般直接 wire 引出即可。

例如生成时钟, always#10 sys\_clk = ~sysclk; 表示每 10 个单位时间就翻转一次, 如果时间单位是 ns, 那就是每 10ns 翻转一次, 就是生成了 50MHz 的时钟。周期是 20ns。

接下来给出一个参考的 testbench, 如下所示:

```

'timescale 1ns / 1ns

`define UD #1

module tb_led_test();

reg      clk   ;

reg      rst_n ;

wire[7:0] led   ;

reg [7:0] data  ;

initial begin

rst_n <= 0;

clk  <= 0;

#20;

rst_n <= 1;

#2000

$display("I am stop"); //

$stop;

end

always#10 clk = ~clk;//20ns 50MHZ

led_test

#(

.CNT_MAX (10)

)u_led_test(

.clk      (clk  ),// input

.rstn    (rst_n ),// input

.led     (led   ) // output [7:0]

);

initial begin

$monitor("led:%b", led);

end

always@(posedge clk or negedge rst_n)  begin

if(!rst_n)

```

```

data  <=  8'd0;

else

begin

data  <=  {$random}%256;

$display("Now data is %d",data);

end

end

endmodule

```

代码第一行定义了仿真的时间单位和精度, 均为 1ns; 第二行宏定义了延时的时间 UD, 可根据个人代码习惯使用。第 10-18 行对复位和时钟进行初始化, 并且延时 2020ns 后用\$display 打印出暂停仿真的字样, 之后停止仿真。注意\$stop 仅仅是暂停仿真, 不是完全结束仿真, 还可以通过 run 指令继续运行仿真。第 19 行每 10ns 翻转一次, 完成了 50MHZ 时钟的生成。21-28 行例化了流水灯模块, 用来做仿真测试, 该代码主要完成每隔一段时间对输出的数据完成一次移位。进而实现了流水灯。30-32 行用\$monitor 监测 led 变量, 一旦改变就打印出来。第 34-42 行主要是产生测试数据并打印出来, 该数据仅仅用来观察 random 函数的测试。

## 2.5. Modelsim 的使用

该部分主要介绍 Modelsim 的基本使用方法。

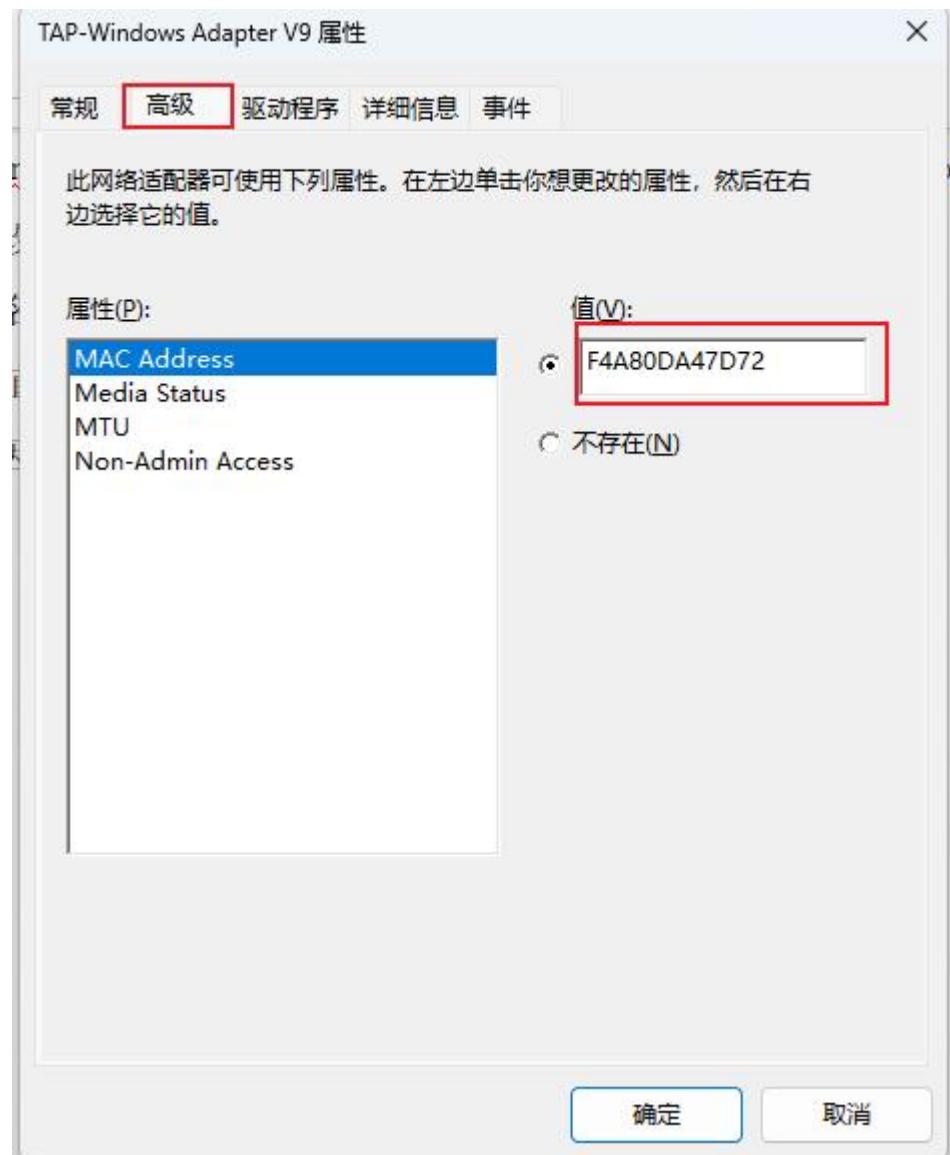

当我们的设计文件没有使用到任何平台的 IP 核时, 我们可以直接打开 Modelsim 新建工程, 然后进行仿真, 具体步骤如下所示:

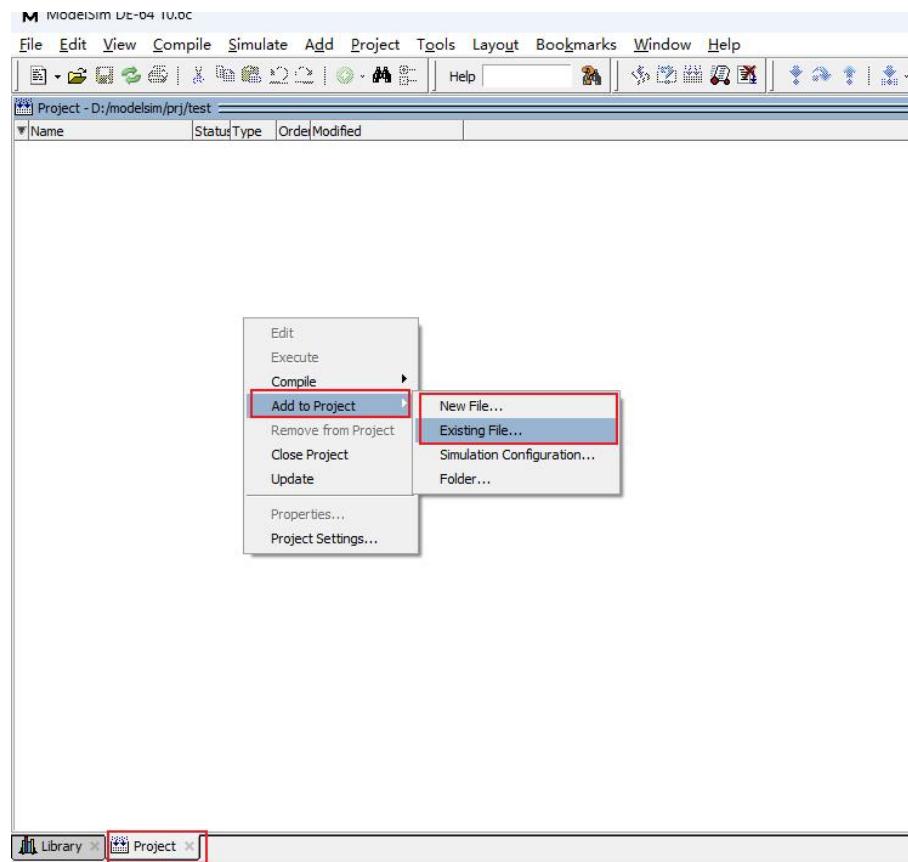

图 2.5-1

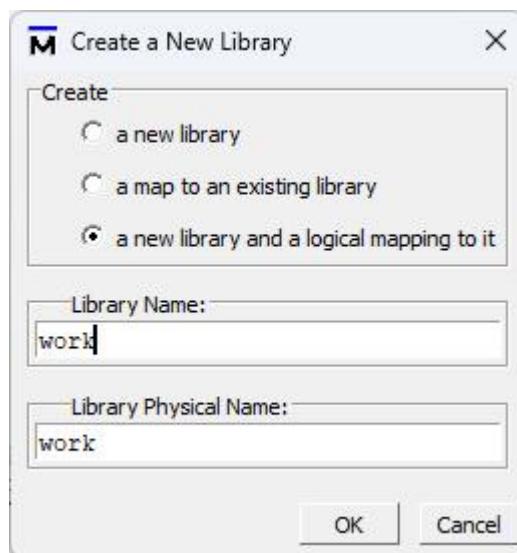

点击左上角 File->New->Library, 新建一个工作库, 一般取名为 work, 因为 Modelsim 运行时都会在这个 work 下面工作, 所以第一次运行 Modelsim 我们需要新建一个叫 work 的库, 如果打开发现已经有 work 的工作库时, 则不用新建。

图 2.5-2

输入 work, 点击 OK 即可。新建完成后就可以看到有个 work 的库在 Modelsim 里面。接下来新建工程。

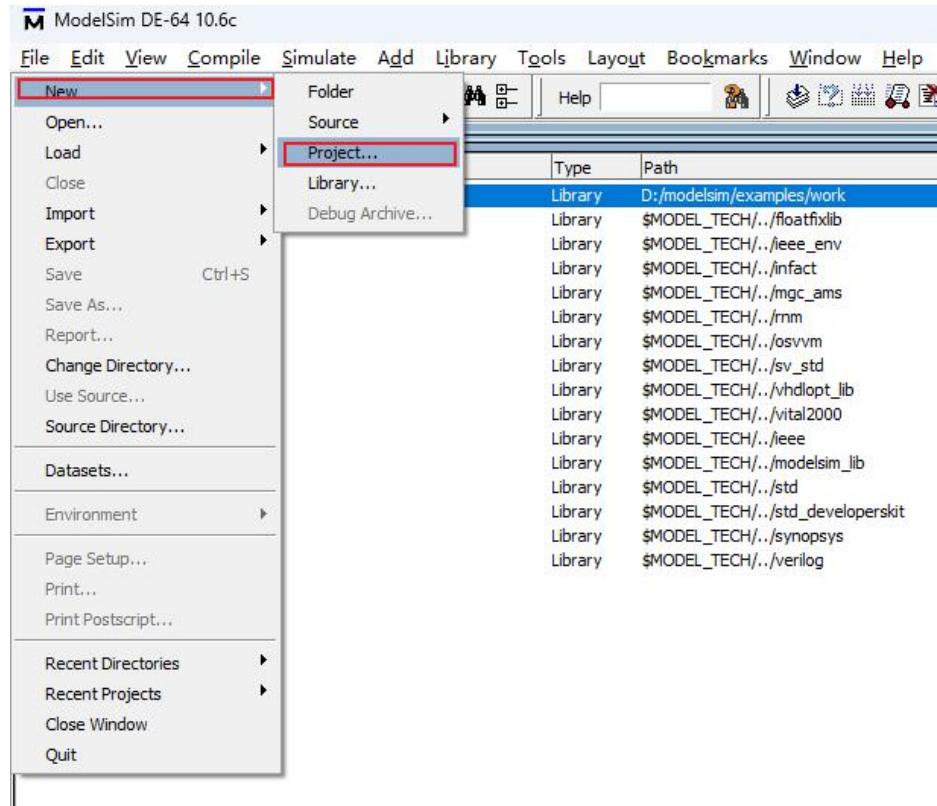

图 2.5-3

左上角 File->New->Project, 新建工程。

图 2.5-4

工程名注意不要出现中文, 其余保持默认即可, 可以看到 Default Library Name 其名字默认指向 work。

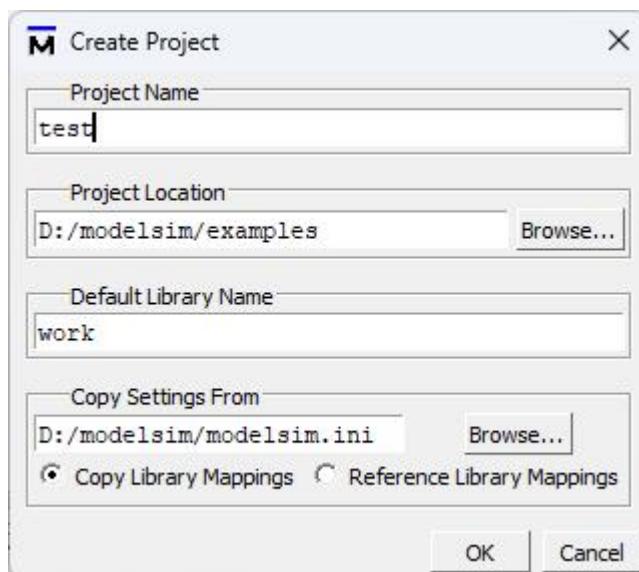

图 2.5-5

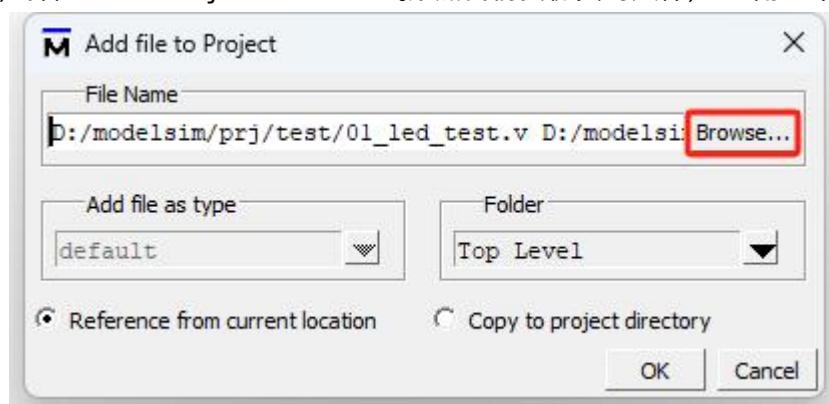

新建完后可以看到下方多了一个叫 Project 的选项卡, 鼠标右键该界面空白部分, 选择 Add to Project->Existing File, 或者 Add to Project->New File。添加我们要仿真的文件, 这里用一个比较简单的来演示。

图 2.5-6

点击 Browse, 添加要仿真的文件。

图 2.5-7

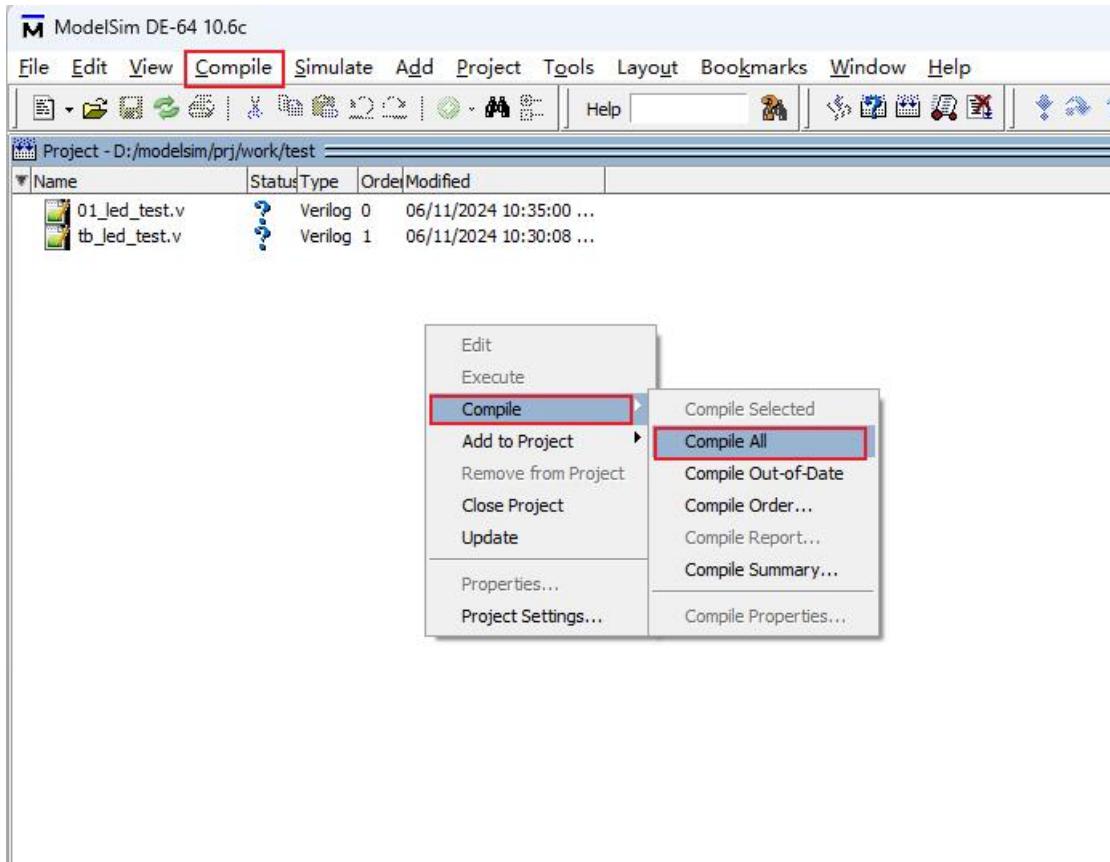

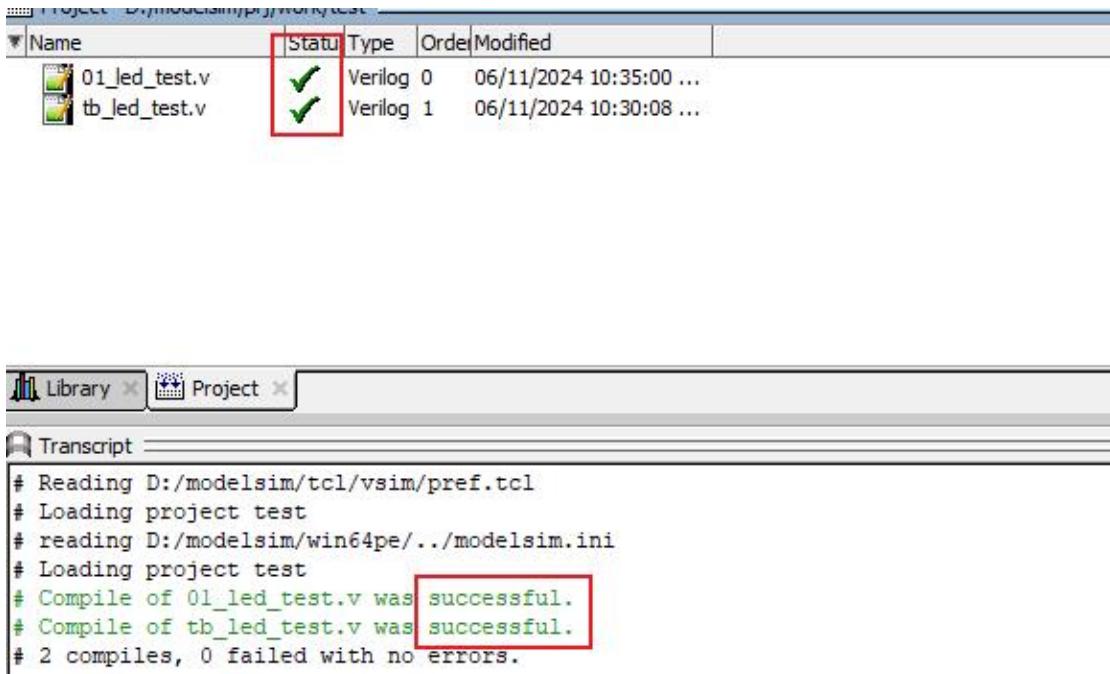

选择上方 Compile 或者鼠标右键空白部分,选择 Compile->Compile,该步骤主要对 verilog 文件进行编译,检查是否有语法错误等。

图 2.5-8

当看到 Status 是个绿色的√, 或者下方打印输出区间没有任何 errors, 显示 successful, 表示我们的文件编

译通过, 可以进行下一步操作了。

图 2.5-9

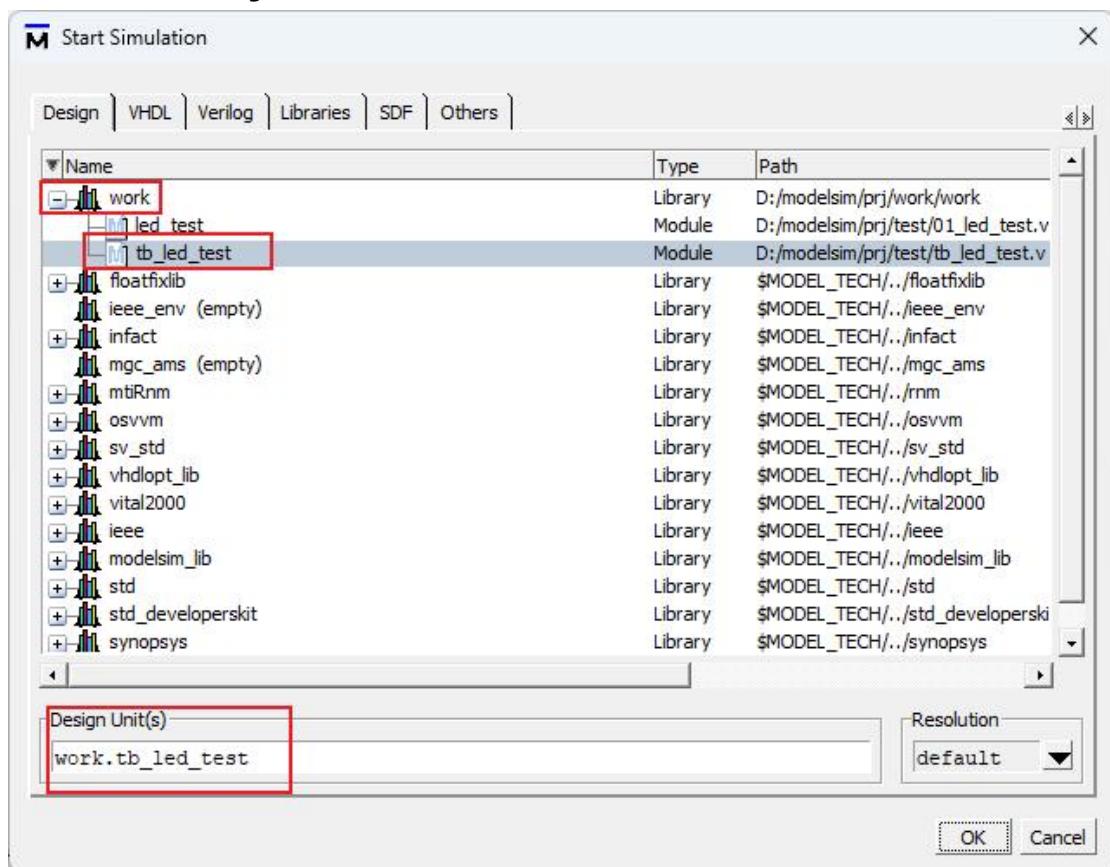

选择上方 Simulate->Start Simulation, 之后会弹出如图 2.5-10 所示的界面, 把 work 展开, 选择我们的 testbench 文件, 可以看到 Design Unit 显示的是我们的 testbench 文件就没问题了。然后点击 OK, 开始仿真。

图 2.5-10

图 2.5-11

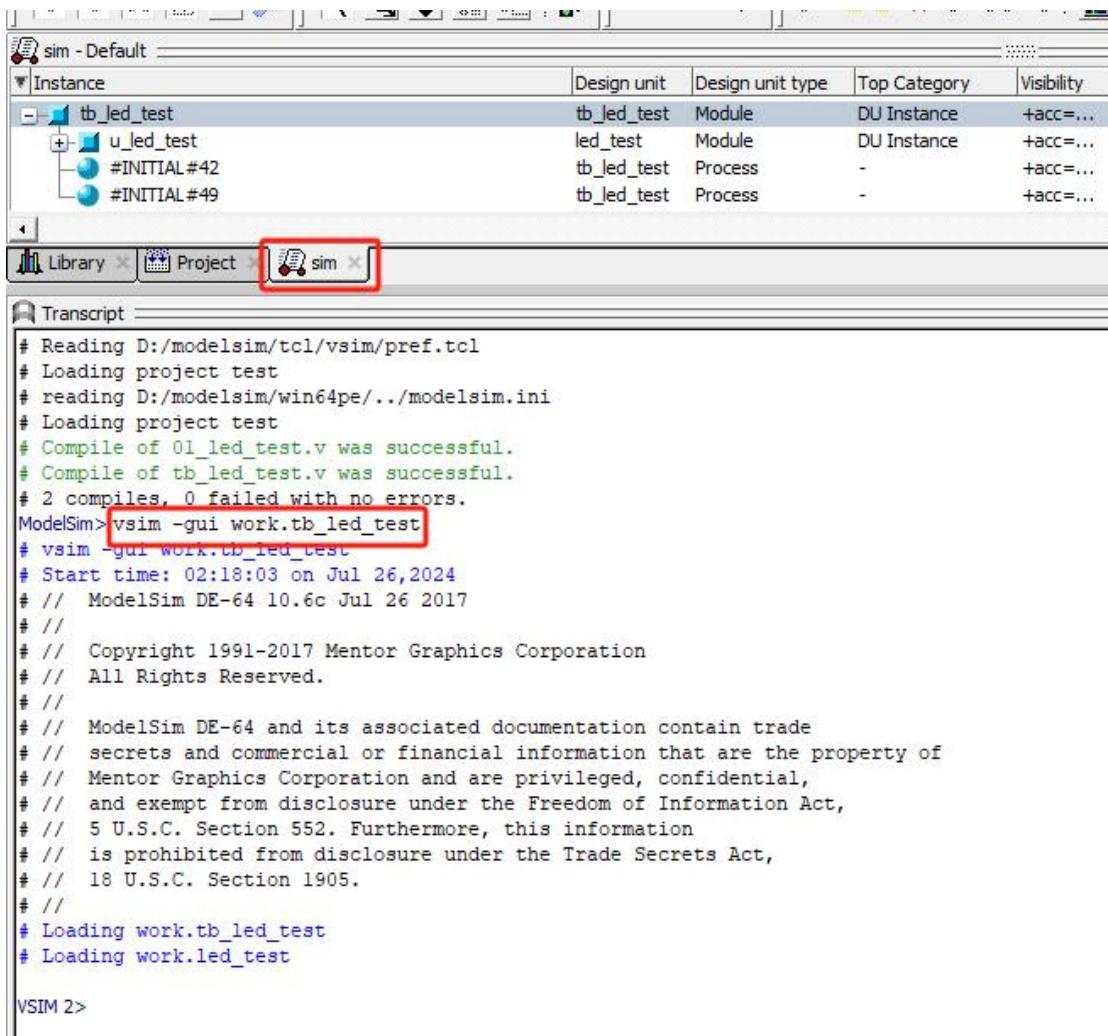

可以看到会弹出一个新的选项卡叫“sim”，然后看红框部分，当点击 OK 后，实际上 Modelsim 自动输入一句命令 vsim -gui work.tb\_led\_test。这其实和后面我们的 do 文件编写是有联系的，do 文件的编写实际上就是在写这些命令，这里我们先铺垫一下。

图 2.5-12

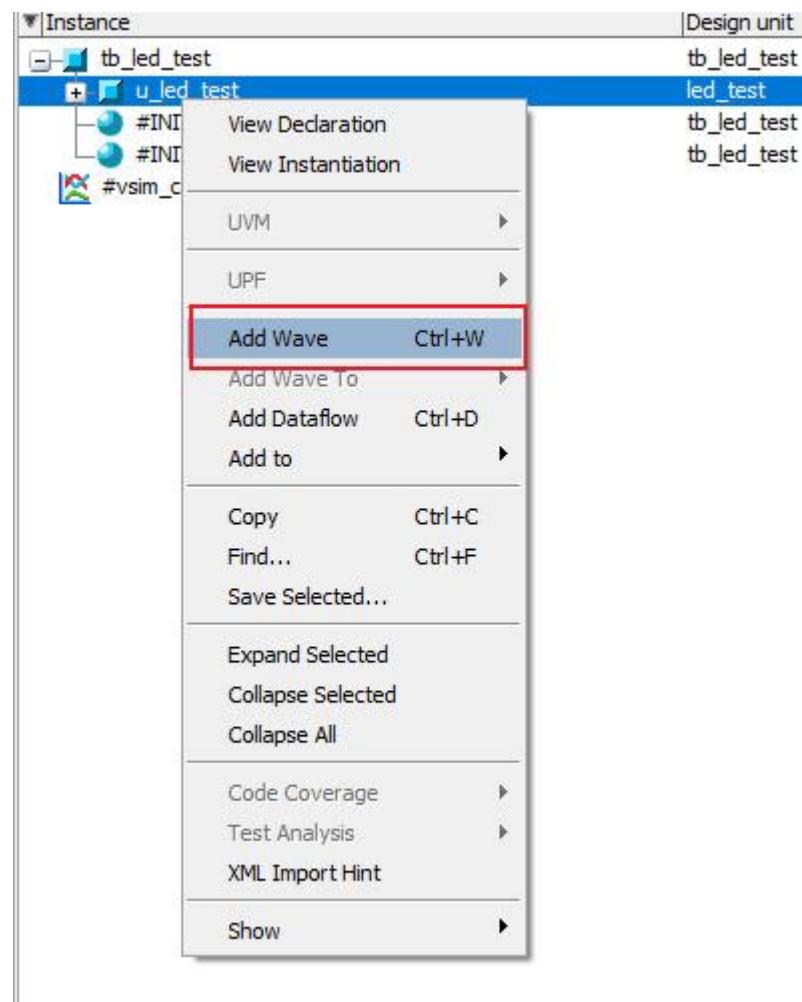

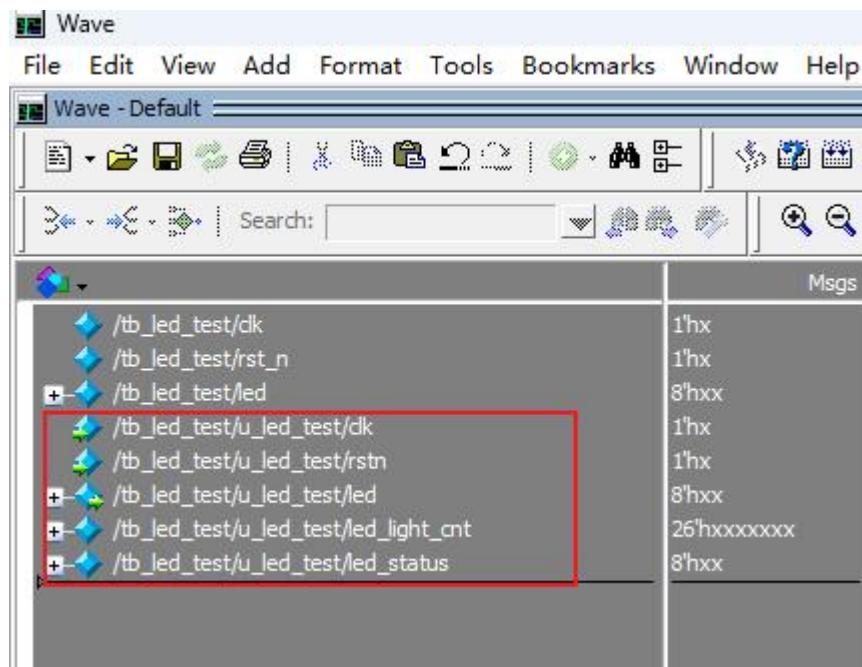

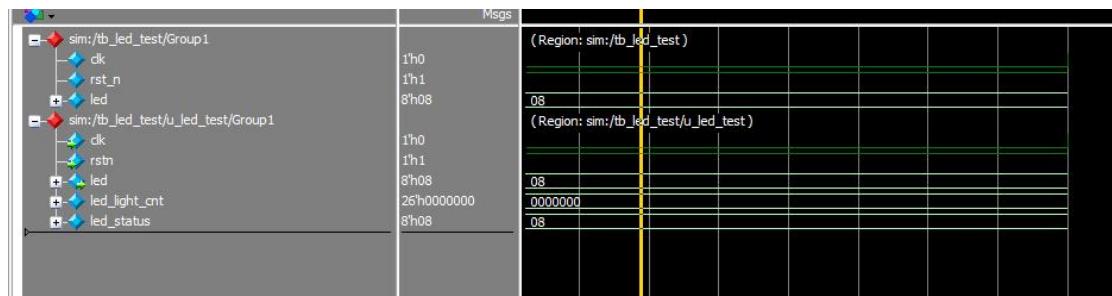

接下来添加我们要观察的信号，这里我是直接右键 u\_led\_test 这个模块，然后选择 Add Wave 或者 ctrl+w，即可将该模块的全部信号都加入到波形窗口中。

图 2.5-13

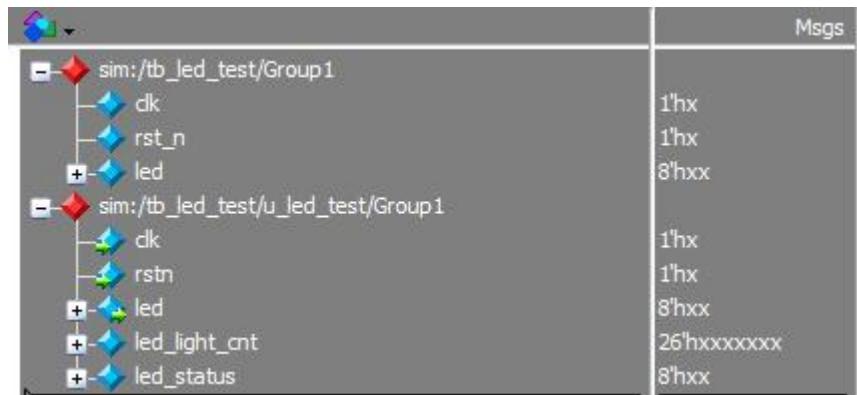

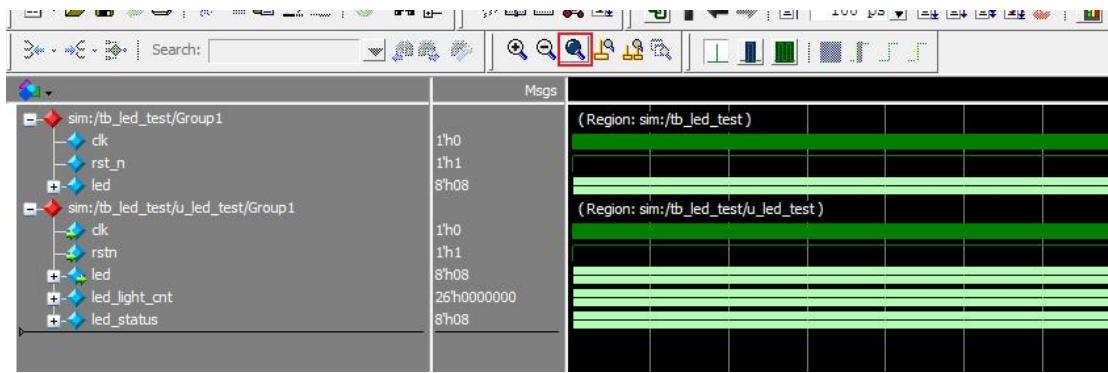

可以看到, 波形窗口已经添加该模块的全部信号, 之后我们按下快捷键, **crtl+a** 全选全部信号, **crtl+g**, 对信号进行分组, 该分组是按照不同模块进行分组, **crtl+h** 消除信号名称的前缀, 如图 2.5-14 所示:

图 2.5-14

图 2.5-15

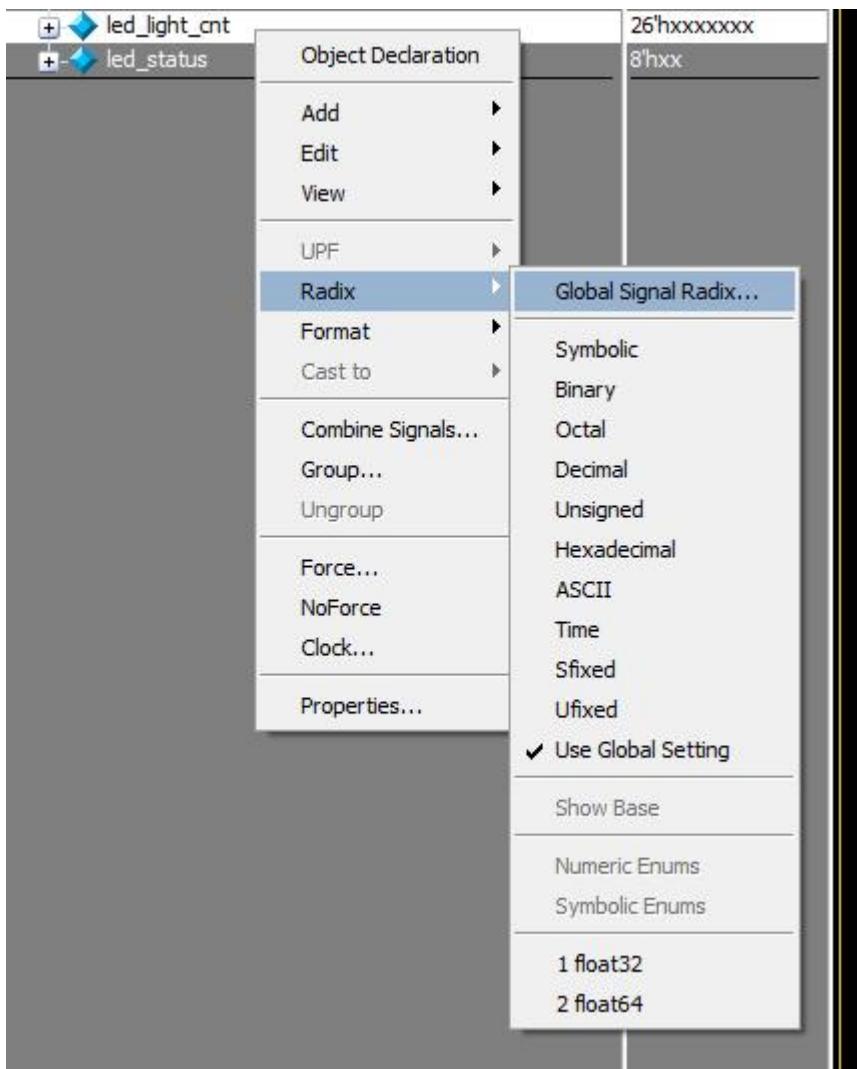

鼠标右键信号, Radix 可以修改该信号显示的格式, 比如二进制显示, 16 进制显示等。Properties 可以修改该信号波形显示的颜色, 这两个是比较常用的。接下来开始来运行我们的仿真。

图 2.5-16

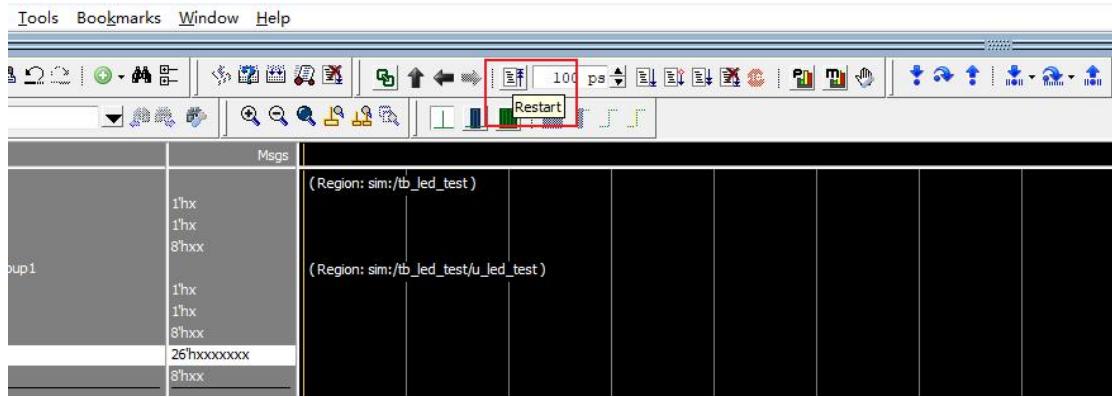

点击上方这个地方, 对信号全部进行 Restart 复位。

图 2.5-17

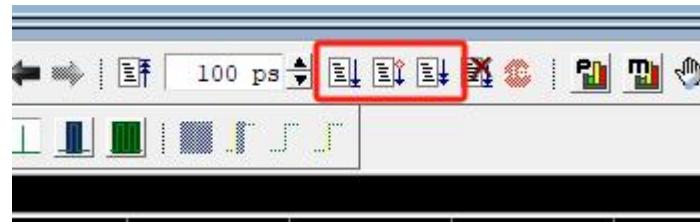

红框旁边的 100 ps 是一次仿真运行的时间, 红框内从左往右看, 第一个是表示运行一次仿真, 其时间为 100ps, 100ps 并不是固定的, 我们可以修改为 1ms, 100us 等。第二个基本比较少用。第三个是让仿真不断运行, 直到用户点击停止为止, 如图 2.5-18 所示:

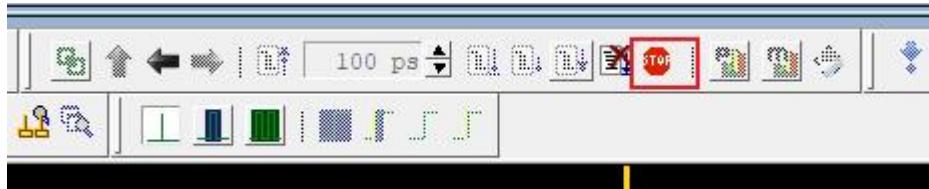

图 2.5-18

按下后, 当用户点击 stop, 仿真才会停止。

图 2.5-19

图 2.5-19 为操作后显示出来的波形。

图 2.5-20

点击红框部分那个按钮, 将缩小波形。我们也可以按住 **ctrl** 键, 然后鼠标滚轮上下, 可以对波形进行缩放。到这里, 基本的使用方法就结束了, 更多操作大家可以去看视频操作, 或者网上百度, 或者自己摸索一下。

再铺垫一下, 完成这些操作后, 我们回去打印输出区间观察一下

```

Transcript

# Compilation of tb_led_test.v was successful.

# 2 compiles, 0 failed with no errors.

ModelSim> vsim -gui work.tb_led_test

# vsim -gui work.tb_led_test

# Start time: 02:18:03 on Jul 26, 2024

# // ModelSim DE-64 10.6c Jul 26 2017

# //

# // Copyright 1991-2017 Mentor Graphics Corporation

# // All Rights Reserved.

# //

# // ModelSim DE-64 and its associated documentation contain trade

# // secrets and commercial or financial information that are the property of

# // Mentor Graphics Corporation and are privileged, confidential,

# // and exempt from disclosure under the Freedom of Information Act,

# // 5 U.S.C. Section 552. Furthermore, this information

# // is prohibited from disclosure under the Trade Secrets Act,

# // 18 U.S.C. Section 1905.

# //

# Loading work.tb_led_test

# Loading work.led_test

add wave -position insertpoint sim:/tb_led_test/u_led_test/*

add wave -position insertpoint sim:/#vsim_capacity#/*

add wave -position insertpoint sim:/tb_led_test/*

add wave -position insertpoint sim:/tb_led_test/u_led_test/*

VSIM 6> restart

VSIM 7> run

VSIM 8> run -continue

VSIM 9> run -all

VSIM 10> run -all

VSIM 10>

```

图 2.5-21

可以看当我们添加波形时, Modelsim 自动执行了一句 `add wave -position xxxxxxx` 的命令, 执行了 `restart`, 也就是复位, `run` 就是运行仿真, 这些都和后续 do 文件的编写息息相关。所以其本质就是编写这些命令, 我们就不需要用鼠标去点每个功能, 每次我们只需要运行 do 文件就可以完成全部操作, 大大提高我们的效率。

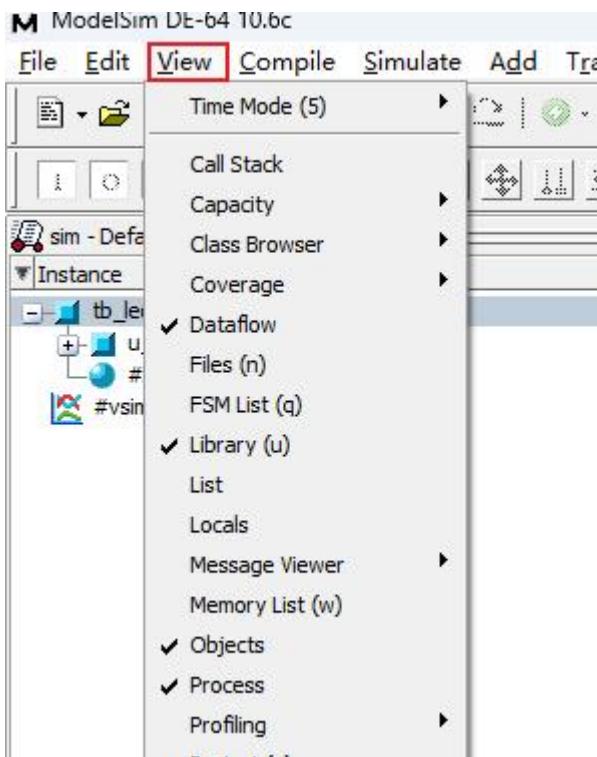

如果大家不小心把某些选项卡关了, 可以在上方 View 选择要查看的窗口, 如图 2.5-22 所示:

比如 Library 前面有个  $\checkmark$ , 就是显示 Library 选项卡的意思。大家可以在这里找找需要显示的界面。

图 2.5-22

## 2.6. 文件的编写

### 2.6.1. 基本命令介绍

前文其实也有提到, Modelsim 实际上是通过输入命令来执行相应功能的, 比如 add wave xxxxx, 就是把信号添加到波形窗口。那接下来就是教大家如何使用这些命令来提高我们的开发效率。

首先先介绍常用的命令。

vlib:该命令为创建一个目录。例如 vlib work。即在当前路径下创建一个名字叫 work 的文件夹。

vmap: 映射逻辑库到物理目录。其格式为 vmap work work 第一个 work 逻辑库名称, 第二个 work 是表示在 PC 里实际的库文件的路径。

注意: 前面所说的通过 File->New->Library 的方法建立了一个 work 的库, 其实就是运行了 vlib 和 vmap, 具体可以看教程视频讲解。本质就是 vlib work vmap work work。

vlog:该命令用来编译 verilog 源码。例如 vlog -work work ./src/test.v 第一个 work 表示文件夹的名称、第二个 work 表示 modelsim 中 library 的库的名称、第三个就是要编译的文件的路径。

vsim:表示启动仿真。

add wave:表示添加波形到波形窗口(add wave -divider 会添加分割线)。

view wave:打开波形窗口。

view structure:打开结构窗口。

view signals:打开信号窗口。

restart:重新仿真, 复位仿真时间, 并清空之前的仿真数据。(如果修改了 verilog 文件 需要重新编译再仿真才行, restart 只是在当前这个仿真下重新开始仿真而已)。

run x:运行 x 时间。例如 run 1ms run1ns run 1us run 250ms 均可。

quit -sim:退出仿真。

quit:退出 Modelsim。(关闭整个软件)

### 2.6.2.文件示例

如果从 0 开始写, 相信是比较陌生的, 其实当我们使用紫光联合仿真的时候, 他会在 sim 的文件夹下生成一个后缀为 tcl 的脚本, 每次运行联合仿真, 实际就是打开 Modelsim 然后运行该 tcl 脚本, 具体路径都在工程目录下的 sim 文件夹下, 如图 2-1 所示:

图 2-1

主要是运行 run\_behav\_compile.tcl 和 run\_behav\_simulate.tcl 这两个文件。我们可以打开来参考一下。

```

vlib work

vmap work ./work

vmap usim "D:/modelsim/pg_sim_lib/usim"

vmap adc_e2 "D:/modelsim/pg_sim_lib/adc_e2"

vmap ddc_e2 "D:/modelsim/pg_sim_lib/ddc_e2"

vmap dll_e2 "D:/modelsim/pg_sim_lib/dll_e2"

vmap hsstlp_lane "D:/modelsim/pg_sim_lib/hsstlp_lane"

vmap hsstlp_pll "D:/modelsim/pg_sim_lib/hsstlp_pll"

vmap iolhr_dft "D:/modelsim/pg_sim_lib/iolhr_dft"

vmap ipal_e1 "D:/modelsim/pg_sim_lib/ipal_e1"

vmap ipal_e2 "D:/modelsim/pg_sim_lib/ipal_e2"

vmap iserdes_e2 "D:/modelsim/pg_sim_lib/iserdes_e2"

vmap oserdes_e2 "D:/modelsim/pg_sim_lib/oserdes_e2"

vmap pciegen2 "D:/modelsim/pg_sim_lib/pciegen2"

vlog -work work \

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/01_led_test/source/Desktop/01_led_test.v" \

```

```

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/01_led_test/source/Desktop/tb_led_test.v" \

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/01_led_test/source/source/Desktop/01_led_test.v"

```

以上是 run\_behav\_compile.tcl 的内容,大家可以结合视频教程一起分析一下,该文件主要完成工作区间的建立和一些库的映射以及对代码的编译。

vlib:该命令创建一个文件夹。例如 vlib work。

vmap:映射逻辑库到物理目录。其格式为 vmap work work 第一个 work 逻辑库名称, 第二个 work 是表示在 PC 里实际的库文件的路径。

vlog:该命令用来编译 verilog 源码。例如 vlog -work work ./src/test.v

第一个 work 表示文件夹的名称。

第二个 work 表示 Modelsim 中 library 的库的名称。

第三个就是要编译的文件的路径。

所以大家其实可以参考 demo 的脚本来编写我们的 do 文件, 我们的 do 文件本质上也是写这些命令, 只不过后缀不一样, 但其运行方法是一致的, 均为 do+空格+文件名。所以到此, 大家应该都知道我们的 do 文件是怎么去编写了, 其实就是把这些 Modelsim 的运行指令, 写成一个脚本, 然后用 do 指令直接完成我们想要的所有操作, 可以大大提高我们的效率。在展示如何使用 Modelsim 的时候也介绍了, 每一步操作实际上都是软件工具自动帮我们输入命令, 现在就是把这些命令给拿出来。接下来我们看 run\_behav\_simulate.tcl 的内容。

```

vsim -novopt -L work -L usim -L adc_e2 -L ddc_e2 -L dll_e2 -L hsstlp_lane -L hsstlp_pll -L iolhr_d

ft -L ipal_e1 -L ipal_e2 -L iserdes_e2 -L oserdes_e2 -L pciegen2 tb_led_test usim.GTP_GRS

add wave *

view wave

view structure

view signals

run 1000ns

```

vsim:表示启动仿真。vsim -L +逻辑库的名字。

add wave:表示添加波形到波形窗口。(add wave -divider 会添加分割线)

view wave:打开波形窗口。

view structure:打开结构窗口。

view signals:打开信号窗口。

run x:运行 x 时间。例如 run 1ms run1ns run 1us run 1s run 250ms 均可。

再顺带介绍一下一些常用的。

restart:重新仿真, 复位仿真时间, 并清空之前的仿真数据。(如果修改了 verilog 文件 需要重新运行 do 文件才生效, restart 只是在当前这个仿真下重新开始仿真而已)

quit -sim:退出仿真。

quit:退出 Modelsim。

该脚本主要是完成仿真, 以及一些仿真完成后的操作, 比如添加波形, 观察波形, 设置运行时间。

所以, 其实我们可以把这两个文件合起来, 变成一个文件, 做成我们自己的 do 文件就行了, 如此, 以后修改代码重新仿真都不需要去 PDS 软件里面去点联合仿真, 我们直接在 Modelsim 里面直接 do 就行了。合并后的 do 文件如下所示:

```

cd D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/01_led_test/sim/behav

vlib work

vmap work ./work

vmap usim "D:/modelsim/pg_sim_lib/usim"

vmap adc_e2 "D:/modelsim/pg_sim_lib/adc_e2"

vmap ddc_e2 "D:/modelsim/pg_sim_lib/ddc_e2"

vmap dll_e2 "D:/modelsim/pg_sim_lib/dll_e2"

vmap hsstlp_lane "D:/modelsim/pg_sim_lib/hsstlp_lane"

vmap hsstlp_pll "D:/modelsim/pg_sim_lib/hsstlp_pll"

vmap iolhr_dft "D:/modelsim/pg_sim_lib/iolhr_dft"

vmap ipal_e1 "D:/modelsim/pg_sim_lib/ipal_e1"

vmap ipal_e2 "D:/modelsim/pg_sim_lib/ipal_e2"

vmap iserdes_e2 "D:/modelsim/pg_sim_lib/iserdes_e2"

vmap oserdes_e2 "D:/modelsim/pg_sim_lib/oserdes_e2"

vmap pciegen2 "D:/modelsim/pg_sim_lib/pciegen2"

vlog -work work \

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/source/Desktop/01_led_test.v" \

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/source/Desktop/tb_led_test.v" \

"D:/ziguang_demo/MES2L100Hv2/MES2L100Hv2/2_Demo/01_led_test/source/source/Desktop/01_led_test.v"

vsim -novopt -L work -L usim -L adc_e2 -L ddc_e2 -L dll_e2 -L hsstlp_lane -L hsstlp_pll -L iolhr_dft -L ipal_e1 -L ipal_e2 -L iserdes_e2 -L oserdes_e2 -L pciegen2 tb_led_test usim.GTP_GRS

add wave *

add wave -position insertpoint sim:/tb_led_test/u_led_test/*

view wave

view structure

view signals

```

```

restart

```

```

run 1000ns

```

可以看到,基本上就是把两个文件给合并起来,然后多添加了 restart 语句。至于添加波形的语句 add wave -position insertpoint sim:/tb\_led\_test/u\_led\_test/\* ,如果大家不熟悉这样的格式,可以直接在 Modelsim 里面手动添加,然后看其打印区间,输出的指令格式,复制下来就行了。一开始,大家不熟悉的话可以这么操作,等熟悉了后,就可以完全编写了,因为使用了紫光的联合仿真,所以中间会用 vmap 映射很多的紫光的仿真库。包括 vsim 也调用了很多紫光相关的库。所以,如果大家并没有用到紫光的 IP 核或者原语等,只是单纯的验证逻辑的话,其实没有这么麻烦。与紫光的仿真库有关的都可以删了,所以主要就是一个 vlib work,然后 vmap work work,然后 vlog 我们要仿真的文件的路径,注意需要写好 testbench。然后 vsim,然后添加要查看的波形,然后 restart,然后 run 即可。

### 3. Pango 与 Modelsim 的联合仿真

#### 3.1. 实验简介

实验目的: 完成 PDS 软件和 Modelsim 的联合仿真设置。

实验环境:

Window11

PDS2022.2-SP6.4

Modelsim10.6rc

硬件环境:

暂无

#### 3.2. 实验原理

编写完成 Testbench 文件后, 在 PDS 设置好 Modelsim 的路径, 即可启动联合仿真。

##### 3.2.1. 编译仿真库

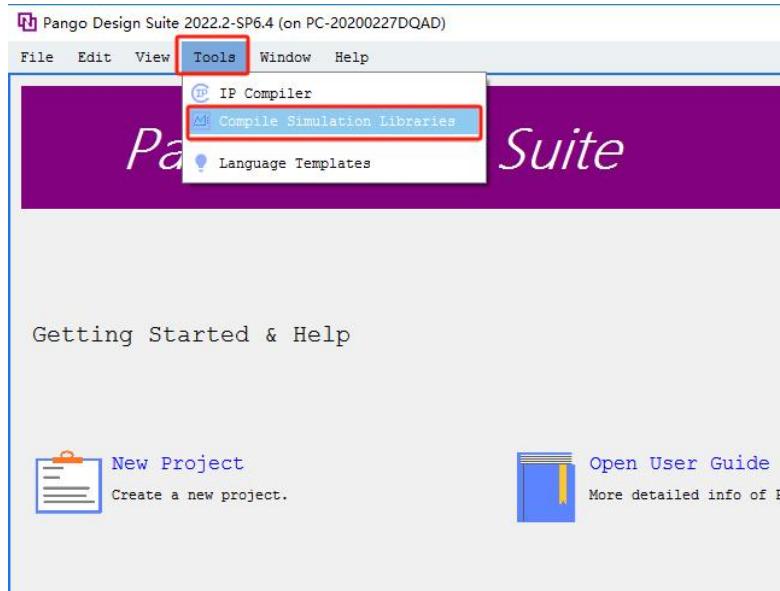

首先打开 PDS 软件, 可以不用打开工程, 具体图 3.2-1 所示:

图 3.2-1

不管是否打开工程, 均可以在软件上方工具栏中找到 Tools->Compile Simulation Libraries;

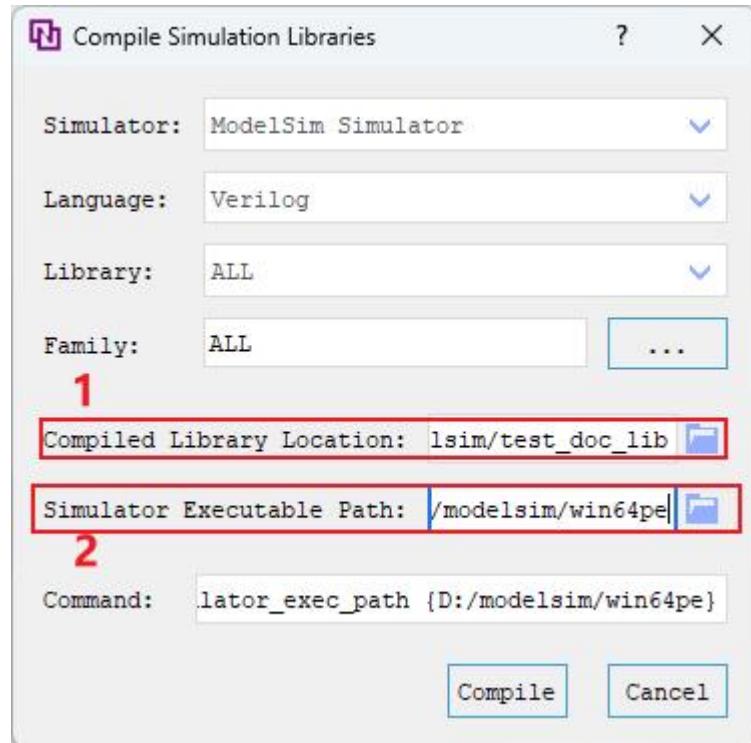

图 3.2-2

打开后可以看到弹出如图 3.2-2 所示的界面, 其中红框 1 表示存放生成的仿真库的路径, 推荐可以在 Modelsim 的安装目录下新建一个文件夹来存放, 笔者是用 pango\_sim\_lib 来表示, 通俗易懂。红框 2 表示 Modelsim 的启动路径, 不同版本其存放的文件夹名字可能不一样, 有 win64pe/win64/win32 等, 都是 win 开头, 笔者所用的 10.6c 为 win64pe。之后点击 Compile 即可, 等待编译完成。

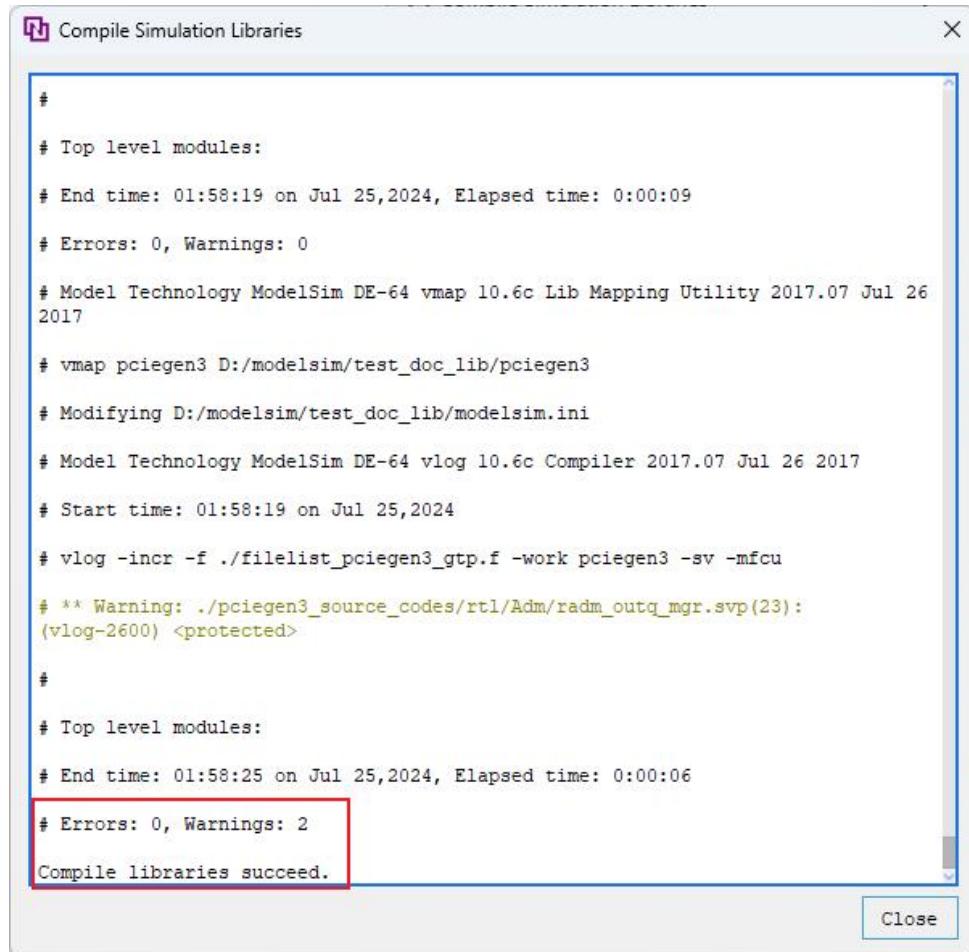

The screenshot shows a Windows application window titled "Compile Simulation Libraries". The main text area contains a command-line log from ModelSim. The log details the compilation process, including the use of vmap and vlog commands, and ends with a message indicating success: "Compile libraries succeed.". A red rectangular box highlights the line "# Errors: 0, Warnings: 2", which is the only line in the log that is not a standard black text color, suggesting it is the key indicator of success.

```

#

# Top level modules:

# End time: 01:58:19 on Jul 25,2024, Elapsed time: 0:00:09

# Errors: 0, Warnings: 0

# Model Technology ModelSim DE-64 vmap 10.6c Lib Mapping Utility 2017.07 Jul 26

2017

# vmap pciegen3 D:/modelsim/test_doc_lib/pciegen3

# Modifying D:/modelsim/test_doc_lib/modelsim.ini

# Model Technology ModelSim DE-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

# Start time: 01:58:19 on Jul 25,2024

# vlog -incr -f ./filelist_pciegen3_gtp.f -work pciegen3 -sv -mfcu

# ** Warning: ./pciegen3_source_codes/rtl/Adm/radm_outq_mgr.svp(23):

(vlog-2600) <protected>

#

# Top level modules:

# End time: 01:58:25 on Jul 25,2024, Elapsed time: 0:00:06

# Errors: 0, Warnings: 2

Compile libraries succeed.

```

图 3.2-3

当没有任何 Errors 时(Warnings 可以忽略), 表示我们的仿真库已经生成成功了。

### 3.2.2. 设置仿真路径

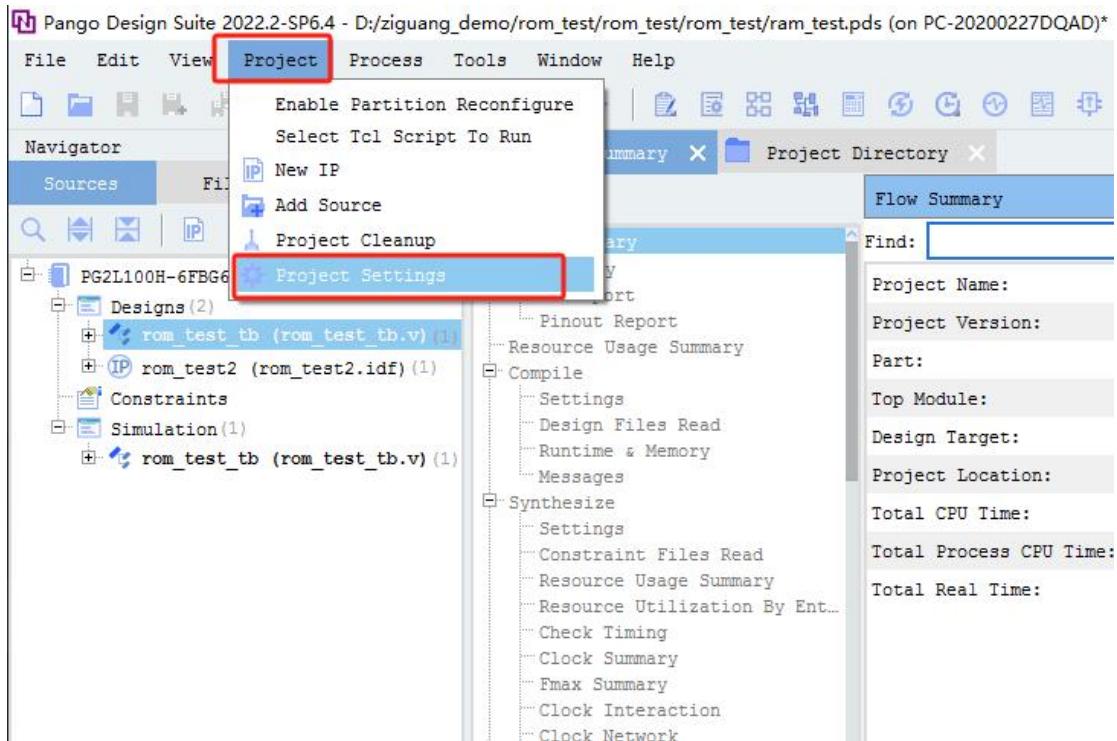

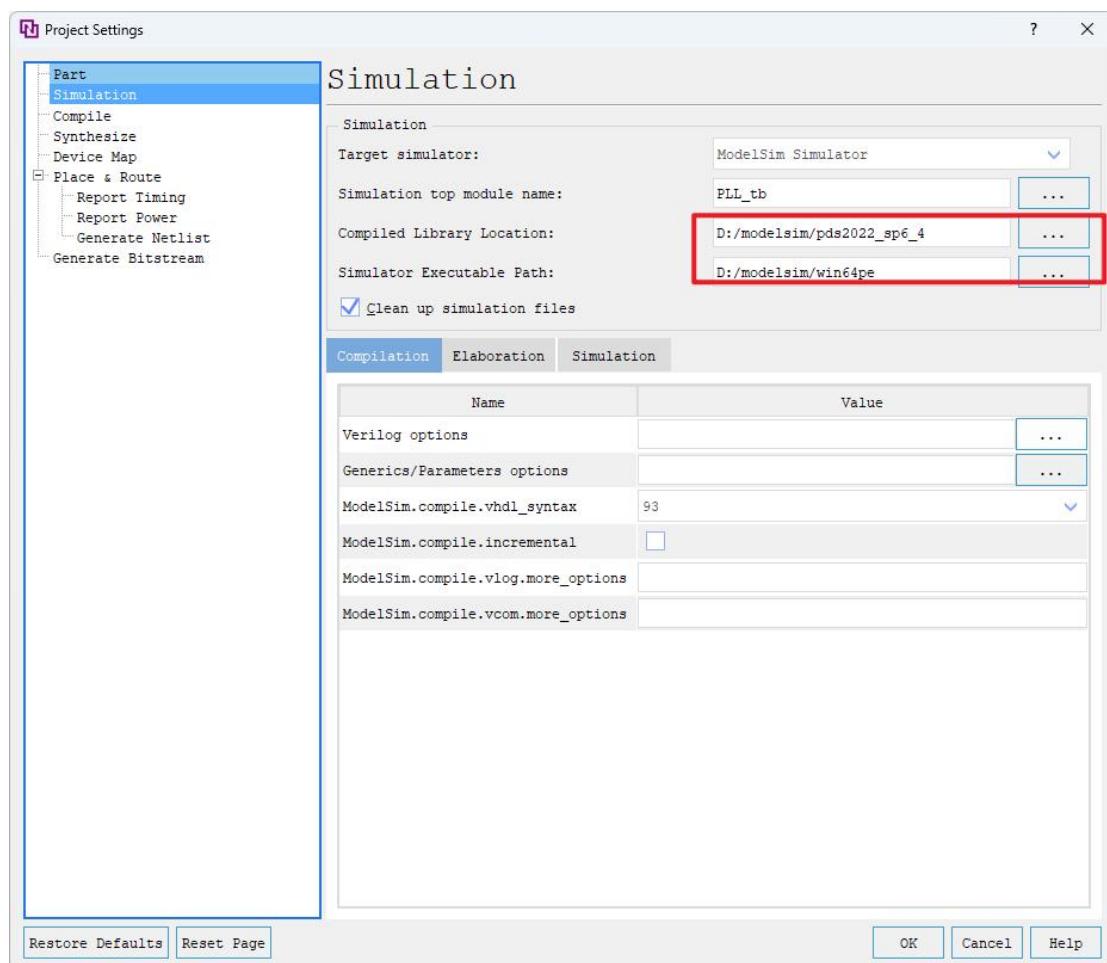

编译完成仿真库后, 我们需要在 PDS 工程中设置仿真路径, 即设置 Modelsim 的路径以及刚才生成的仿真库的路径。

图 3.2-4

打开工程后, 选择 Project->Project Settings;

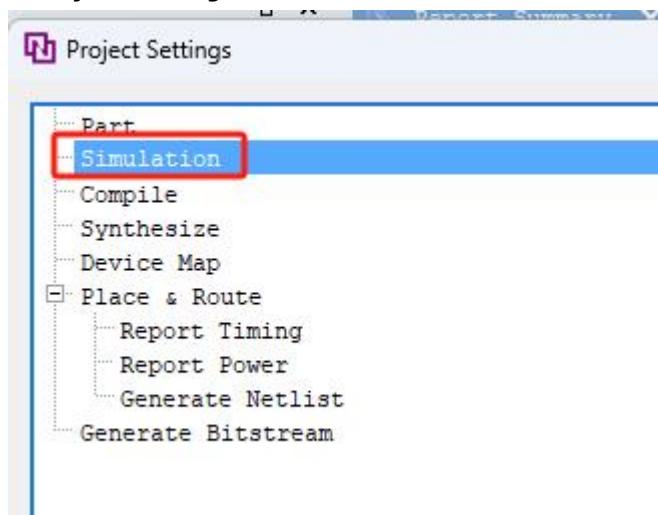

图 3.2-5

选择 Simulation 选项, 准备设置我们的仿真路径。

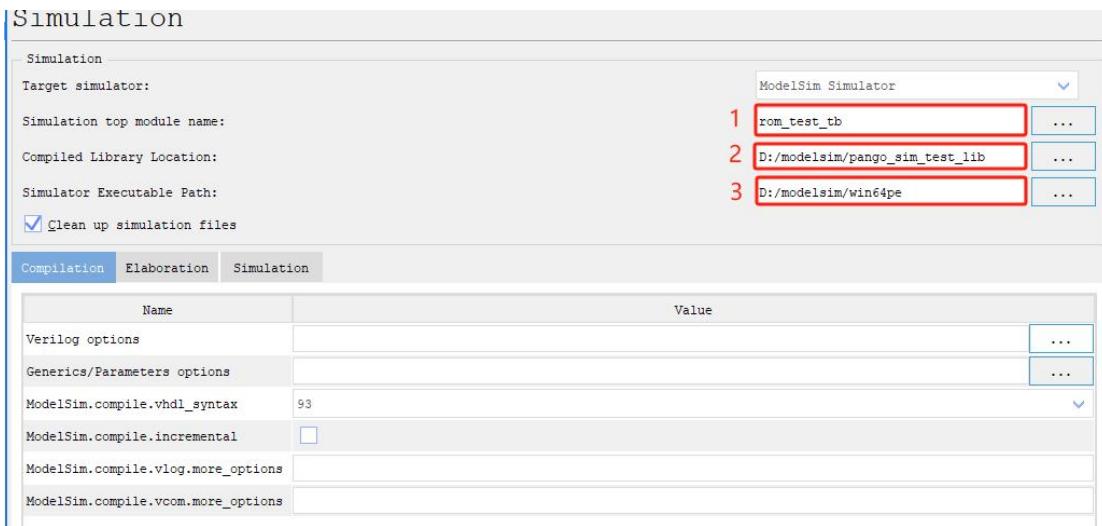

图 3.2-6

接下来开始配置路径, 红框 1 表示我们要仿真的顶层文件, PDS 软件会自动识别。红框 2 选择生成的仿真库的路径。红框 3 是 Modelsim 的启动路径, 也就是说红框 2 和红框 3 的路径和刚才生成仿真库所设置的路径是一模一样的。之后点击 OK 即可。

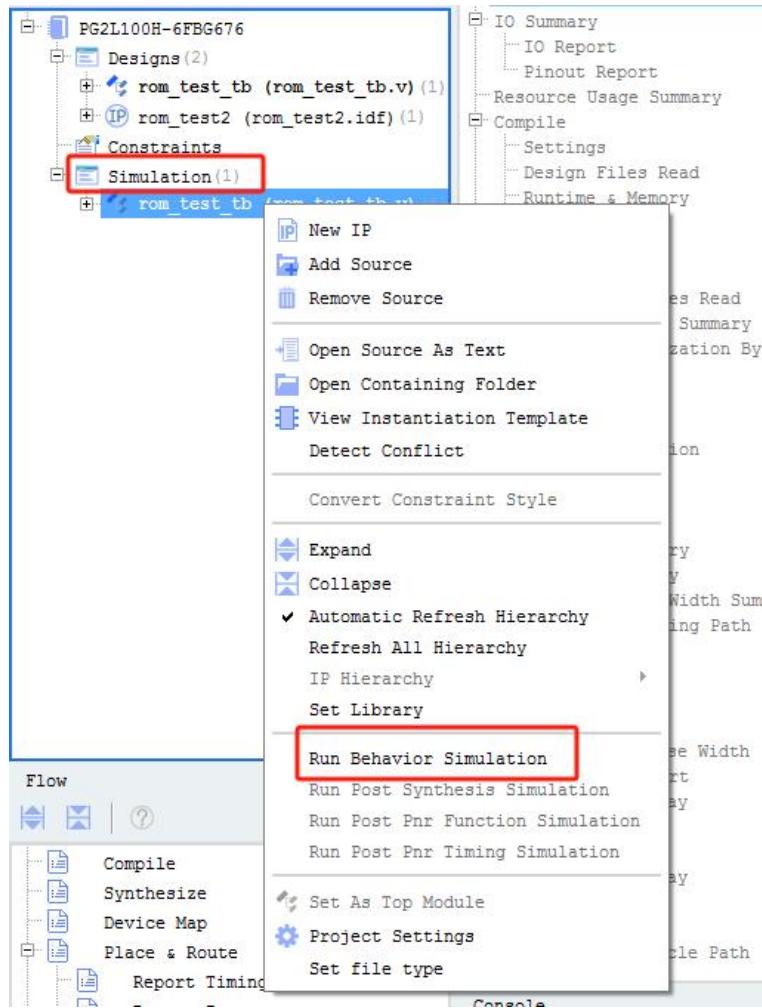

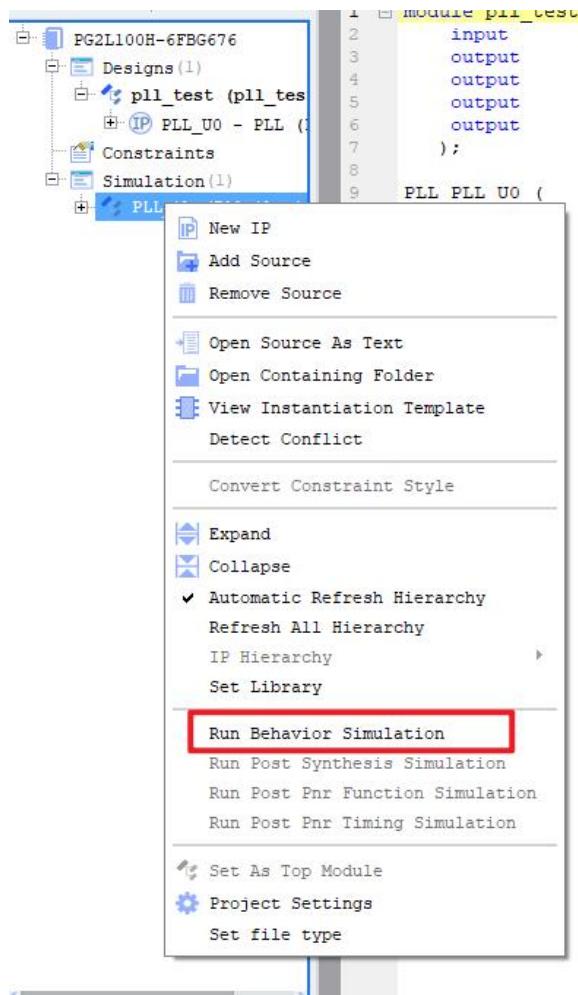

### 3.2.3. 启动联合仿真

图 3.2-7

接下来在 Simulation 下, 右键仿真的顶层文件, 可以看到有四种仿真, 我们常用的是第一种行为仿真, 可以通过查看仿真波形来验证我们设计的逻辑功能是否正确, 该仿真不需要进行任何编译即可直接进行, 如果是后面的三种, 比如 Post Synthesis Simulation 则需要综合后才能仿真。接下来点击 Run Behavior Simulation, 会自动弹出 Modelsim 的界面。如图 3.2-8 所示:

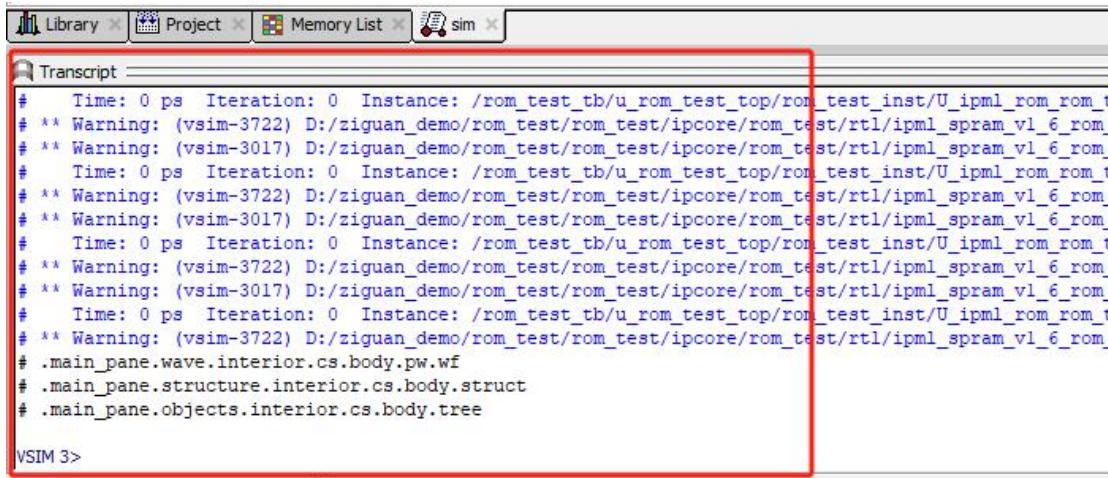

图 3.2-8

打开后 Modelsim 会自动执行仿真脚本, 具体在下个章节会介绍, 如果观察到打印区间没有显示任何 error, 即表示仿真成功, 可以开始进行某些操作任何观察波形(具体请看下一章节内容)。

## 4. 紫光同创 IP core 的使用及添加

### 4.1. 实验简介

实验目的:

了解 PDS 软件如何安装 IP、使用 IP 以及查看 IP 手册

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP-MINI

### 4.2. 实验原理

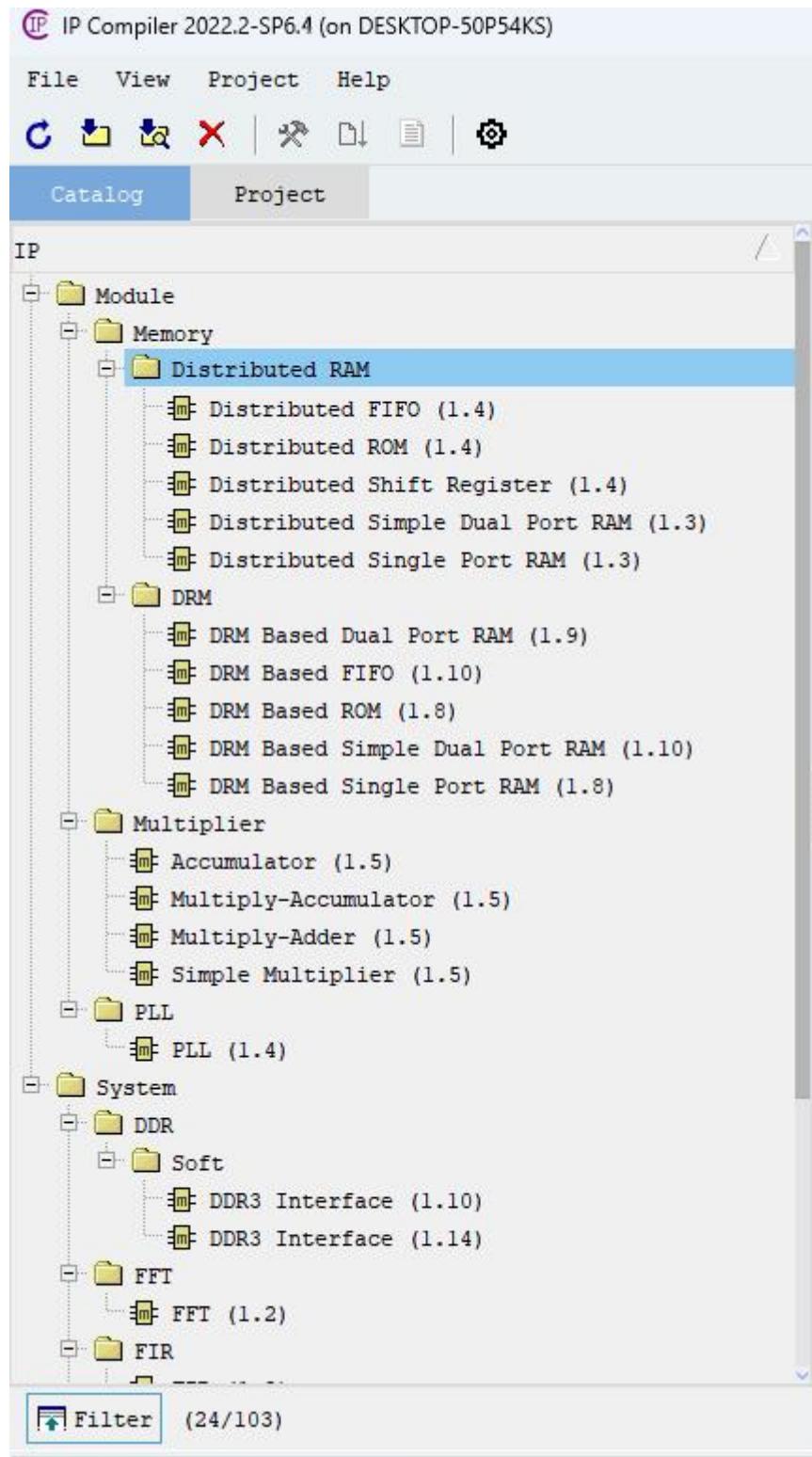

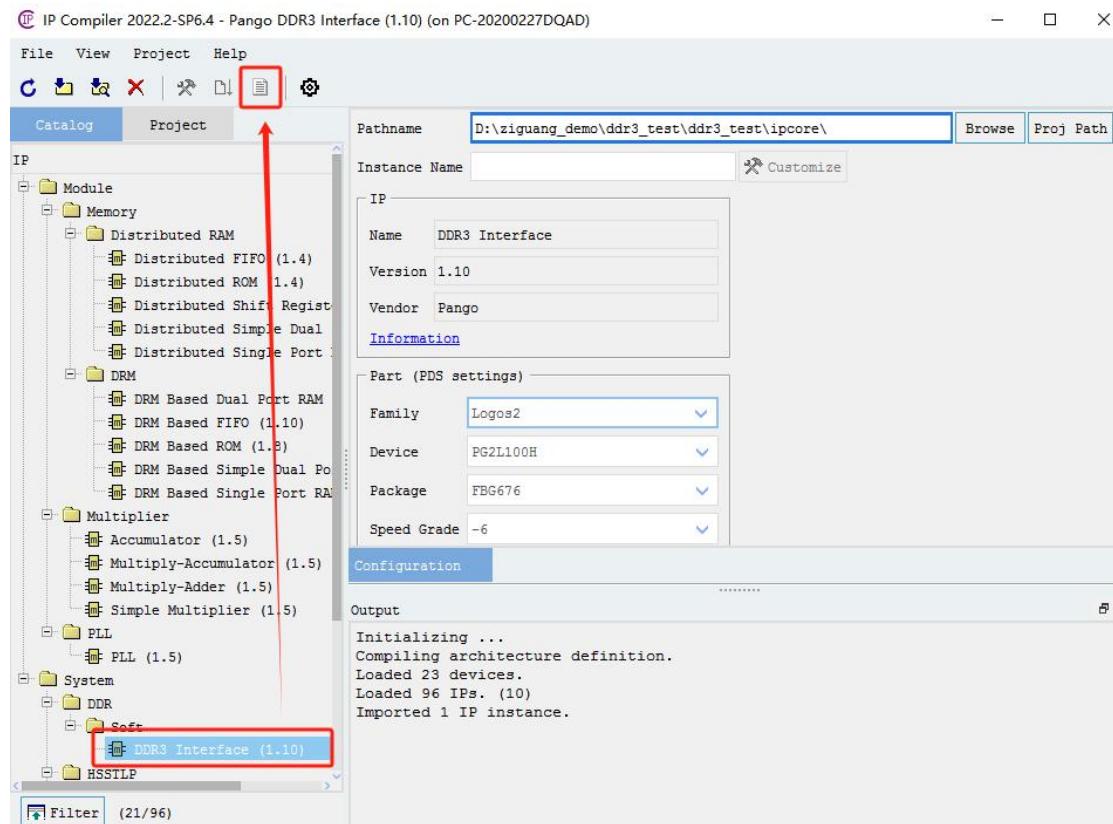

#### 4.2.1. IP 的安装

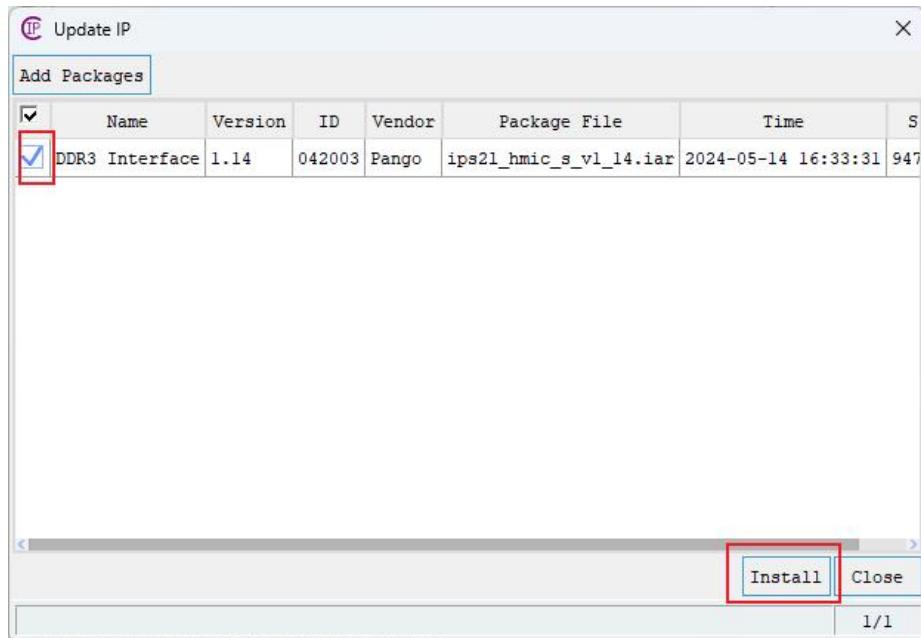

PDS 软件安装完成之后, PDS 自带部分基础 IP, 其他 IP 需用户下载 IP 安装包并安装 IP。

图 4.2-1

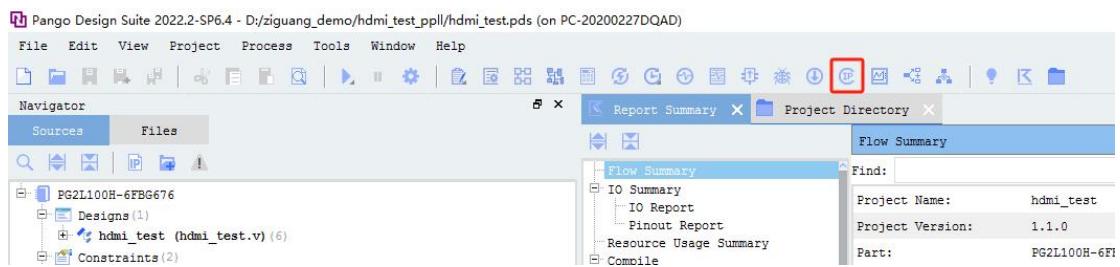

打开 PDS 后, 点击图 4.2-1 里红框部分的 IP 图标。

图 4.2-2

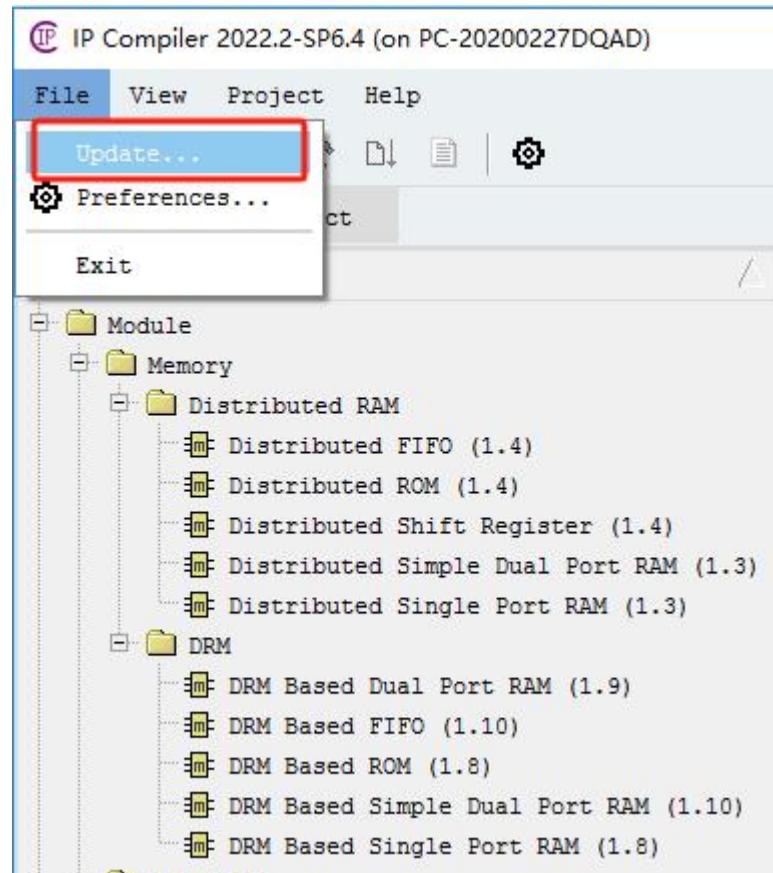

之后在弹出的选项卡的左上角点击 File->Update...

图 4.2-3

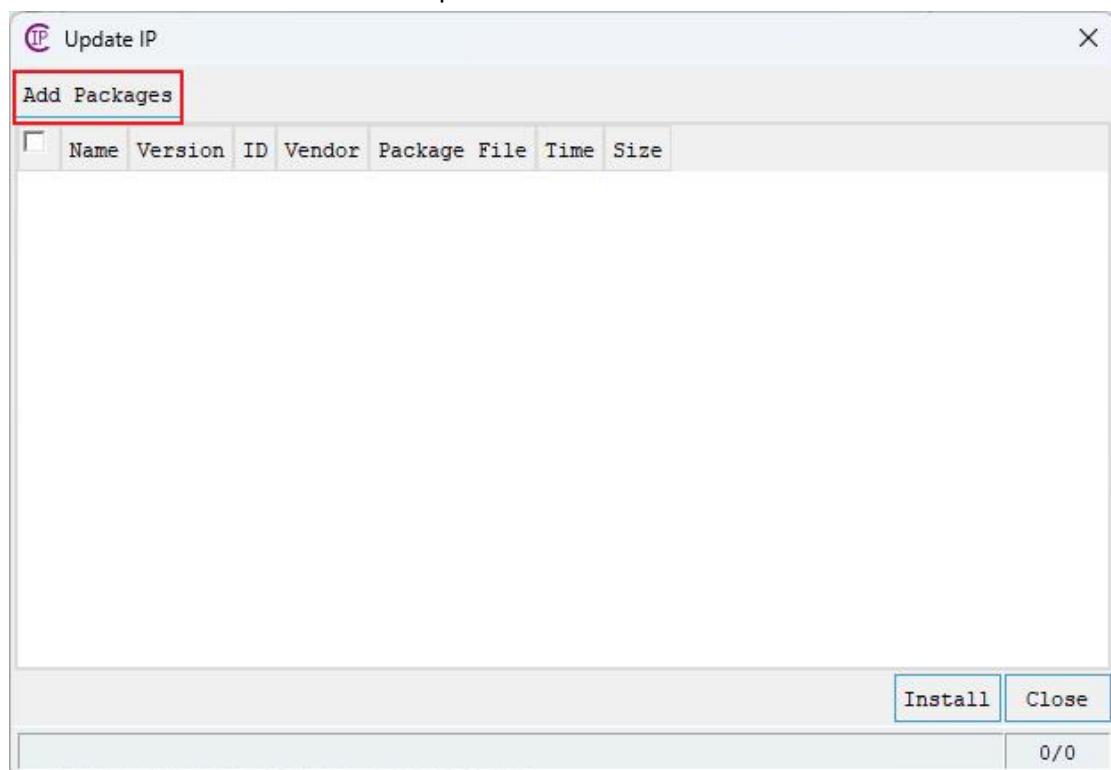

点击左上角 Add Package。

图 4.2-4

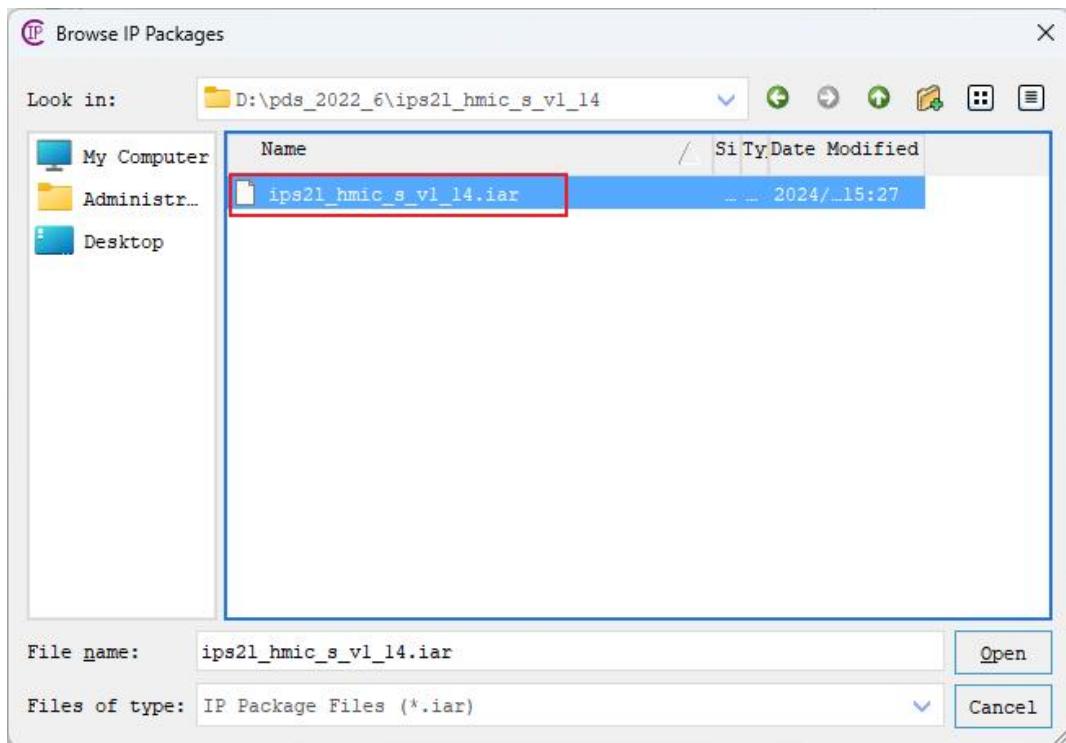

如图 4.2-4 是 DDR3 IP 的安装文件, 后缀都是.iar。大家选择对应的文件后, 点击右下角的 Open 即可。

图 4.2-5

之后勾选上前面的√, 点击 Install 即可。

图 4.2-6

之后在左边的界面可以看到刚才安装的 IP 即可。注意如果发现安装后，弹出了警告，并且左边的界面没有任何变化。那就意味着你安装的 IP 该系列的器件不支持。因为你的工程可能是 LOGOS、LOGOS2、或者 Tian2 等系列，不同芯片型号所用的 IP 是不太相同的，所以大家注意这一点。

#### 4.2.2.例化 IP 及查看 IP 手册

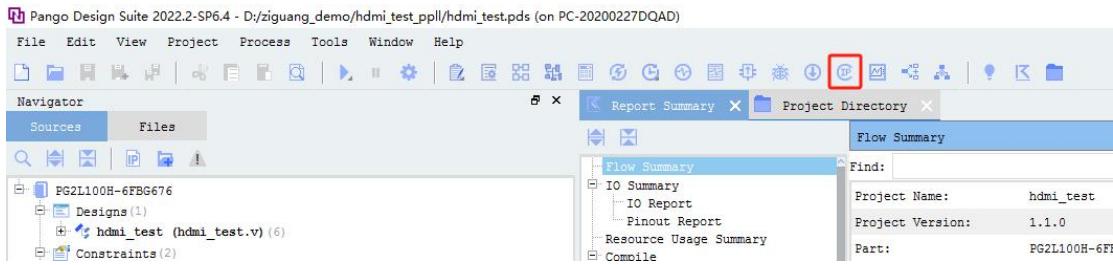

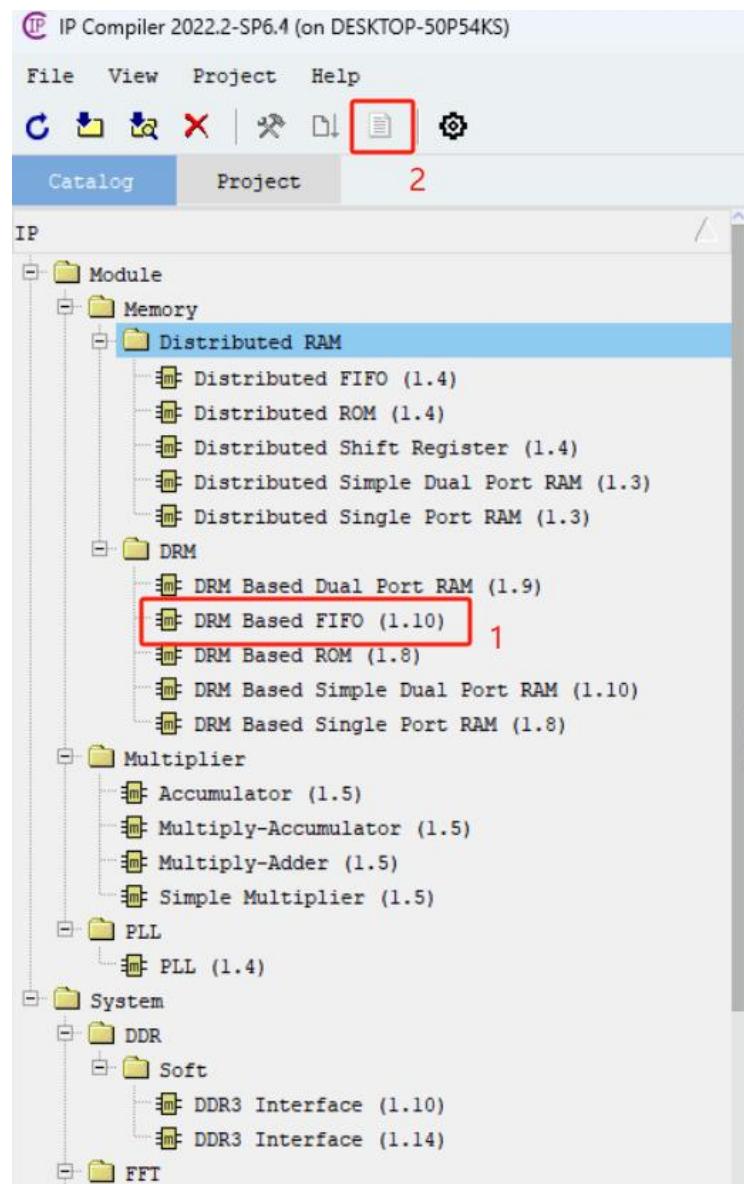

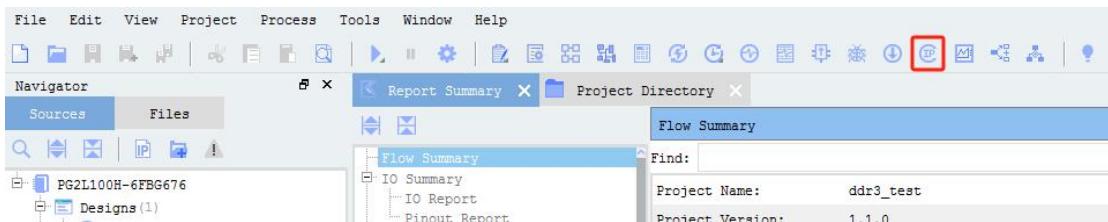

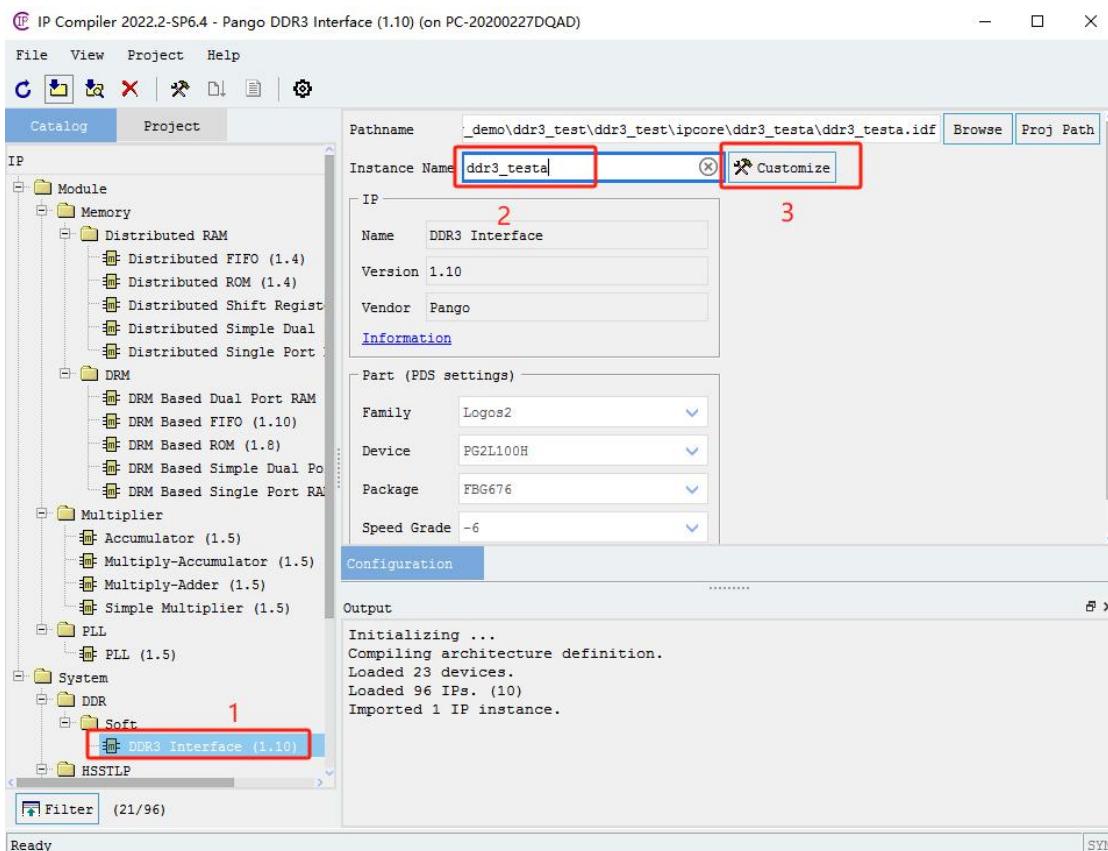

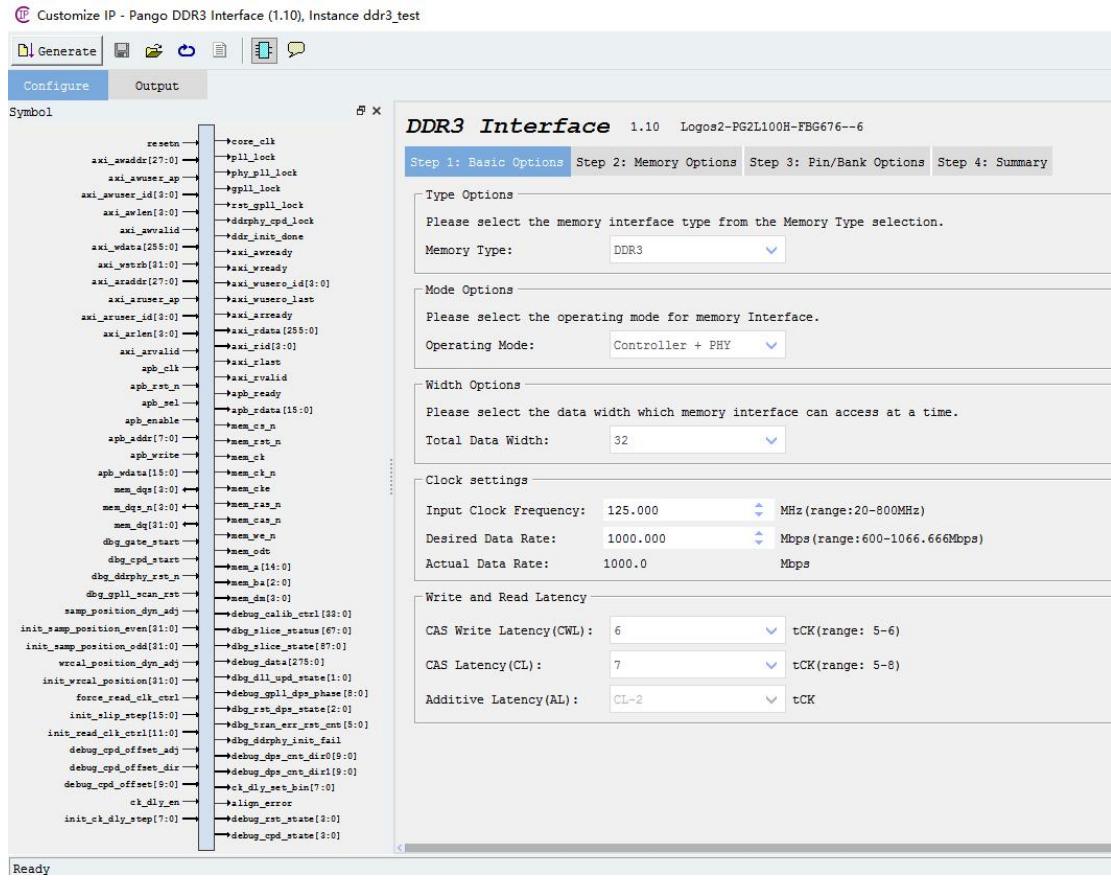

图 4.2-7

继续点击图 4.2-7 所示红框的图标。

图 4.2-8

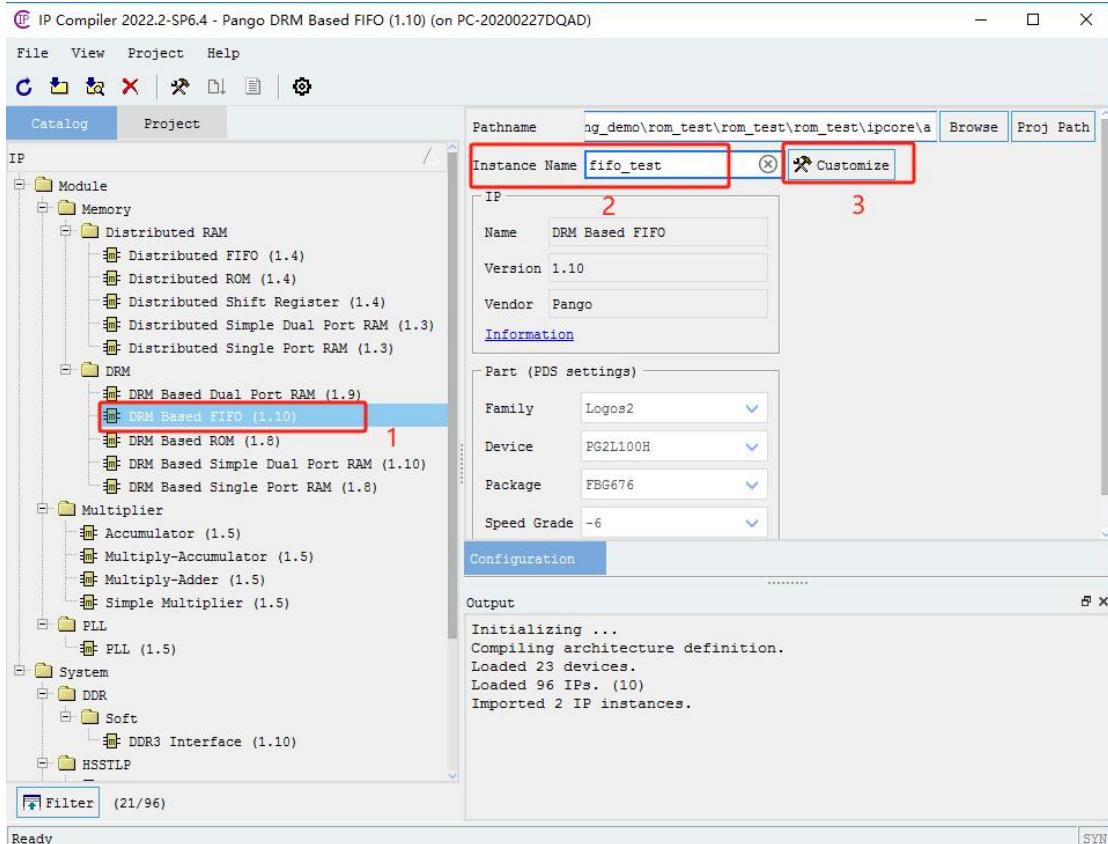

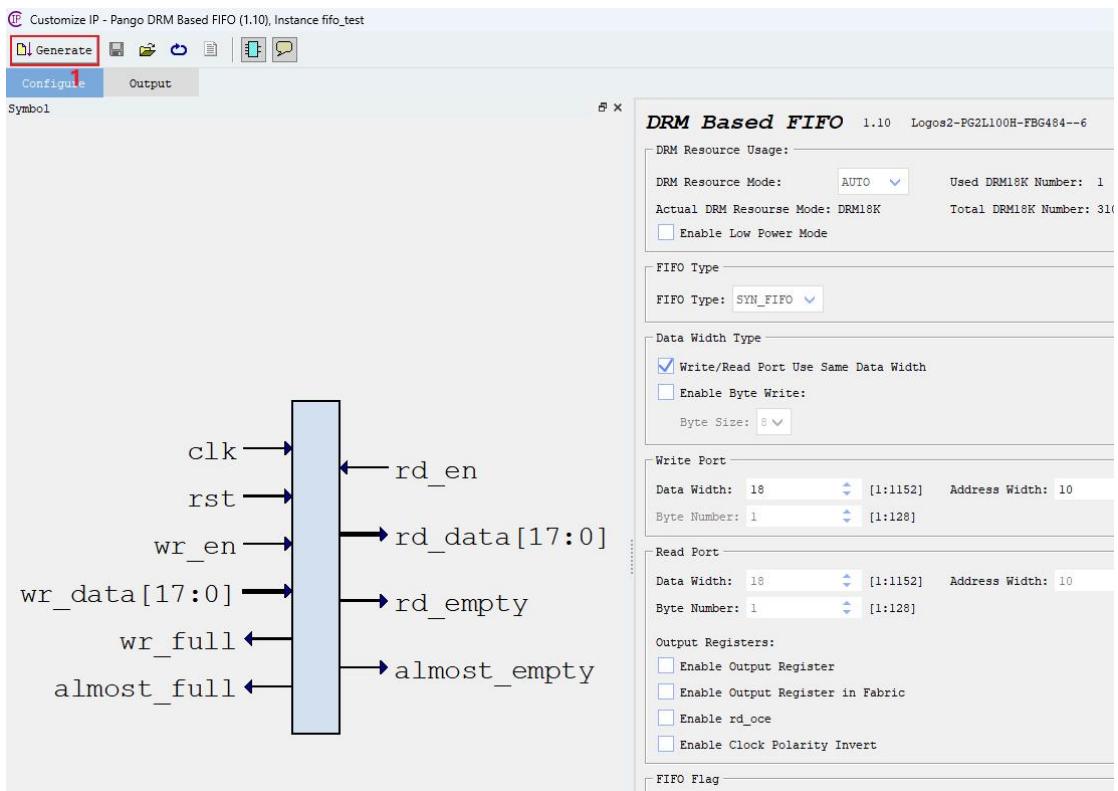

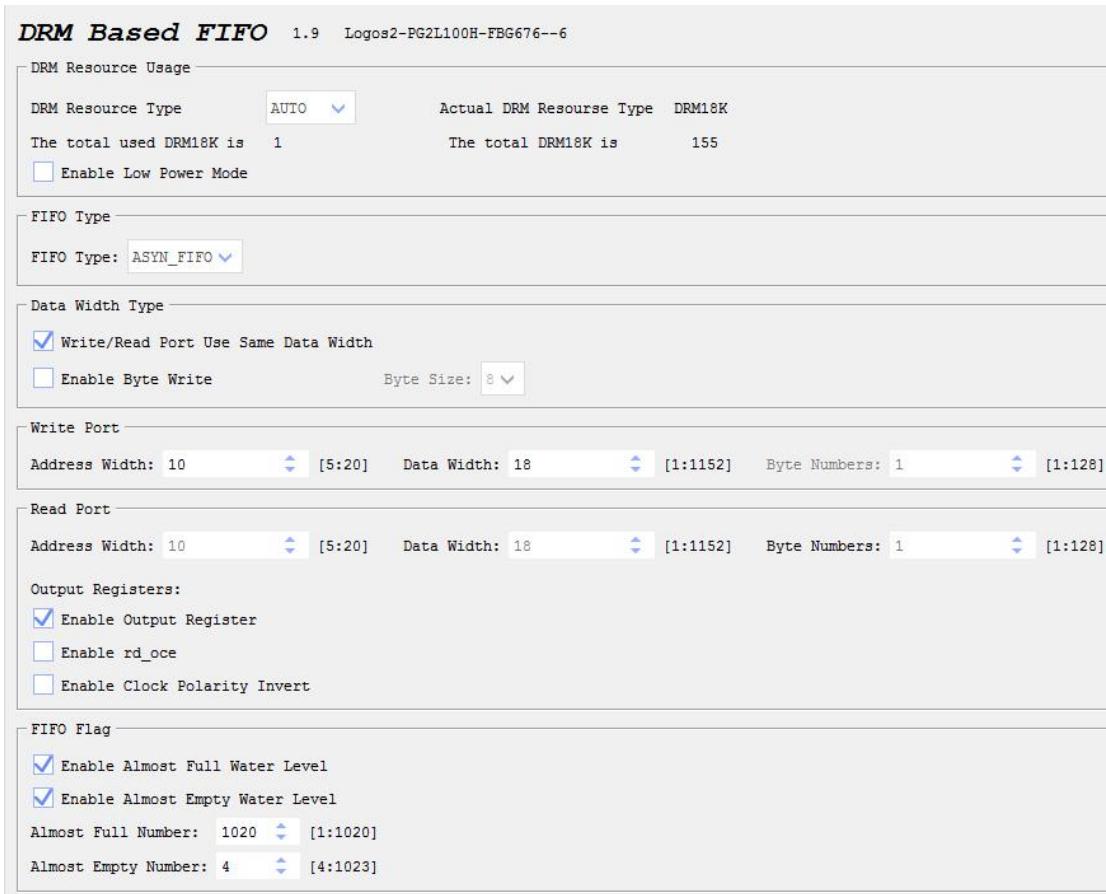

选择想要生成的 IP, 这里以 FIFO 为例子, 即红框 1 所示。红框 2 是用来填写生成的 IP 的名字。点击红框 3 后即可生成 IP, 并弹出该 IP 的配置界面。如图 4.2-9 所示:

图 4.2-9

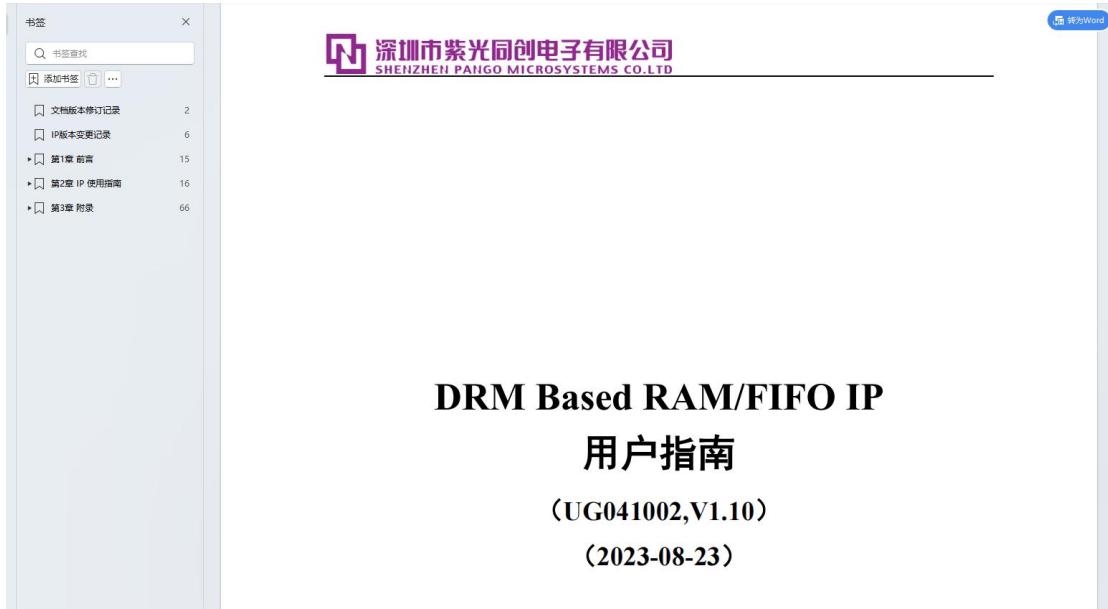

其弹出的提示是询问我们是否要把该 IP 添加到工程中，点击 YES 就行。如果我们不知道 IP 如何使用，可以打开官方参考手册查看，如图 4.2-10 所示：

图 4.2-10

选择想要查看的 IP, 如何点击红框 2 所示的图标, 即可自动弹出官方参考文档。

图 4.2-11

对我们的 IP 配置完成后, 点击左上角红框 1 处的 Generate 即可。

图 4.2-12

```

Customize IP - Pango DRM Based FIFO (1.10), Instance fifo_test

Generate | Run | Stop | Close | Configure | Output

IP Generator (Version 2022.2-SP6.1 build 138931)

Check out license ...

License checkout: fabric_ipc from D:\pds_2022_1\PDS_2022.1\license\new_pds_F4A80DA47D72.lic

Compiling architecture definition.

Compiling verification operator library.

Start generating at 2024-08-02 15:29

Instance: fifo_test (D:\ziguang_demo\hdmi_test_ppll\hdmi_test_ppll\ipcore\fifo_test\fifo_test.idf)

IP: Pango DRM Based FIFO (1.10)

Part: Logos2-PG2L100H-FBG484--6

Create directory 'rtl' ...

Copy 'rtl\ipm2l_fifo_ctrl_v1_1.v.xml' to 'rtl' ...

Copy 'rtl\ipm2l_fifo_v1_10.v.xml' to 'rtl' ...

Copy 'rtl\ipm2l_sdpram_v1_10.v.xml' to 'rtl' ...

Compile file 'rtl\ipm2l_sdpram_v1_10.v.xml' to 'rtl\ipm2l_sdpram_v1_10_fifo_test.v' ...

Compile file 'rtl\ipm2l_fifo_v1_10.v.xml' to 'rtl\ipm2l_fifo_v1_10_fifo_test.v' ...

Compile file 'rtl\ipm2l_fifo_ctrl_v1_1.v.xml' to 'rtl\ipm2l_fifo_ctrl_v1_1_fifo_test.v' ...

Copy 'ipm2l_fifo_wrapper_v1_10.v.xml' ...

Compile file 'ipm2l_fifo_wrapper_v1_10.v.xml' to 'fifo_test.v' ...

Found top module 'fifo_test' in file 'fifo_test.v'.

Copy 'ipm2l_fifo_wrapper_v1_0_tb.v.xml' ...

Compile file 'ipm2l_fifo_wrapper_v1_0_tb.v.xml' to 'fifo_test_tb.v' ...

Run file 'creatResetValue.tcl' ...

Create template file 'fifo_test_tmpl.v' ...

Create template file 'fifo_test_tmpl.vhd' ...

There are 4 source files to synthesize.

Synthesis is disabled.

Done: 0 error(s), 0 warning(s)

```

图 4.2-13

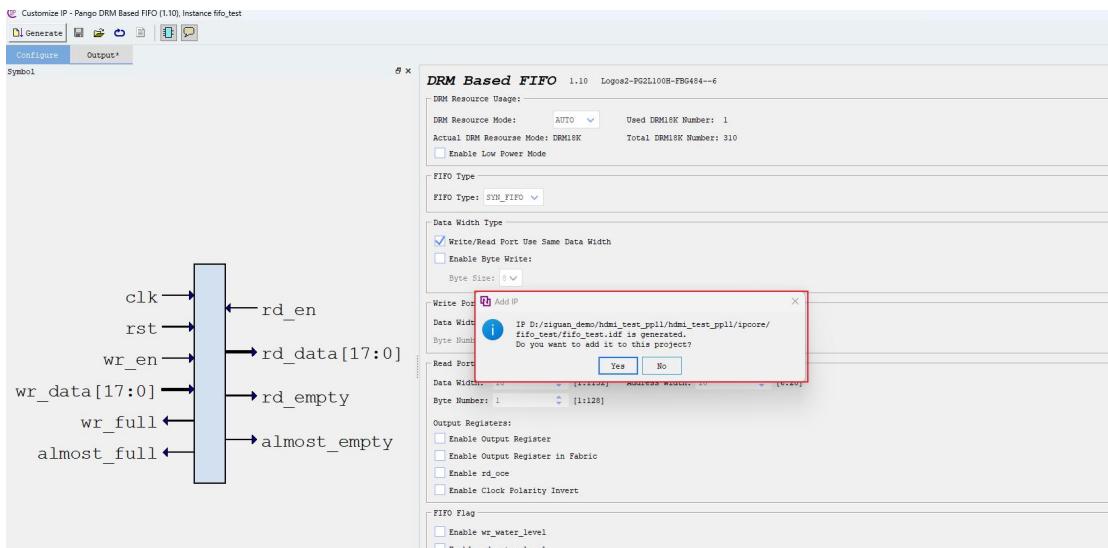

没有任何错误则表示生成成功。

```

// Created by IP Generator (Version 2022.2-SP6.1 build 138931)

// Instantiation Template

// Insert the following codes into your Verilog file.

// * Change the instance_name to your own instance name.

// * Change the signal names in the port associations

fifo_test the_instance_name (

.clk(clk),           // input

.rst(rst),           // input

.wr_en(wr_en),        // input

.wr_data(wr_data),    // input [17:0]

.wr_full(wr_full),    // output

.almost_full(almost_full), // output

.rd_en(rd_en),        // input

.rd_data(rd_data),    // output [17:0]

.rd_empty(rd_empty),   // output

.almost_empty(almost_empty) // output

);

```

图 4.2-14

同时工具也会自动弹出一个 IP 的例化模板, 供我们使用。只需要把该例化模板添加到自己的工程之中, 即可使用我们生成的 IP。

## 5. Pango 的时钟资源——锁相环

### 5.1. 实验目的

了解 Logos2 系列的 PLL 的使用及配置方法。

### 5.2. 实验原理

#### 5.2.1. PLL 介绍

锁相环作为一种反馈控制电路, 其特点是利用外部输入的参考信号来控制环路内部震荡信号的频率和相位。因为锁相环可以实现输出信号频率对输入信号频率的自动跟踪, 所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中, 当输出信号的频率与输入信号的频率相等时, 输出电压与输入电压保持固定的相位差值, 即输出电压与输入电压的相位被锁住, 这就是锁相环名称的由来。

锁相环拥有强大的性能, 可以对输入到 FPGA 的时钟信号进行任意分频、倍频、相位调整、占空比调整, 从而输出一个期望时钟; 除此之外, 在一些复杂的工程中, 哪怕我们不需要修改任何时钟参数, 也常常会使用 PLL 来优化时钟抖动, 以此得到一个更为稳定的时钟信号。正是因为 PLL 的这些性能都是我们在实际设计中所需要的, 并且是通过编写代码无法实现的, 所以 PLL IP 核才会成为程序设计中最常用 IP 核之一。

PLL IP 是紫光同创基于 PLL 及时钟网络资源设计的 IP, 通过不同的参数配置, 可实现时钟信号的调频、调相、同步、频率综合等功能。

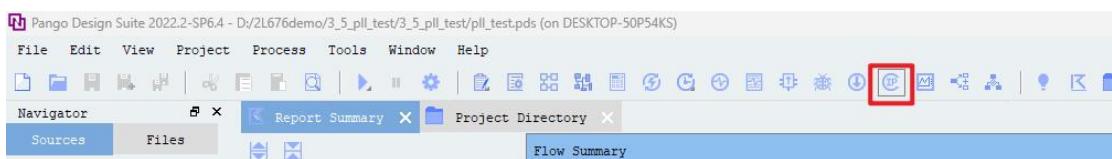

#### 5.2.2. IP 配置

首先点击快捷工具栏的“IP”图标, 进入 IP 例化设置

图 5.2-1 “IP”图标示意图

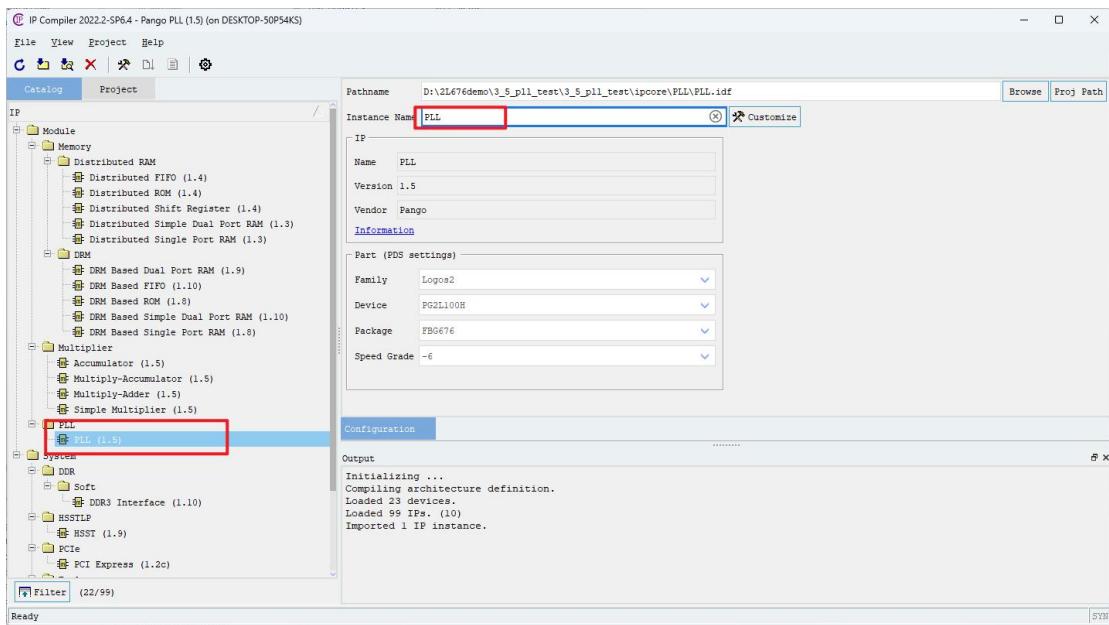

然后在 IP 目录处选择 PLL, 在 Instance name 处为本次实例化的 IP 取一个名字, 接着点击 Customise 进入 IP 配置页面。操作示意图如下:

图 5.2-2 IP 配置流程图 1

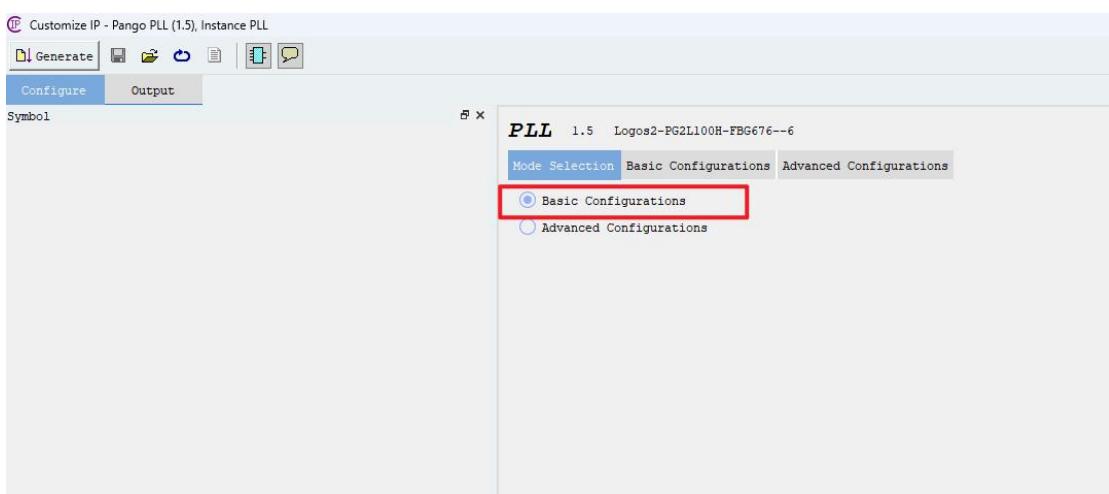

PLL 的使用可选择 Basic 和 Advanced 两种模式, Advanced 模式下 PLL 的内部参数配置完全开放, 需要自己填写输入分频系数、输出分频系数、占空比、相位、反馈分频系数等才能正确配置。Basic 模式下用户无需关心 PLL 的内部参数配置, 只需输入期望的频率值、相位值、占空比等, IP 将自动计算, 得到最佳的配置参数。如果没有特殊应用, 建议使用 Basic 模式配置 PLL。本次实验我们选择 Basic Configuration。

图 5.2-3 IP 配置流程图 2

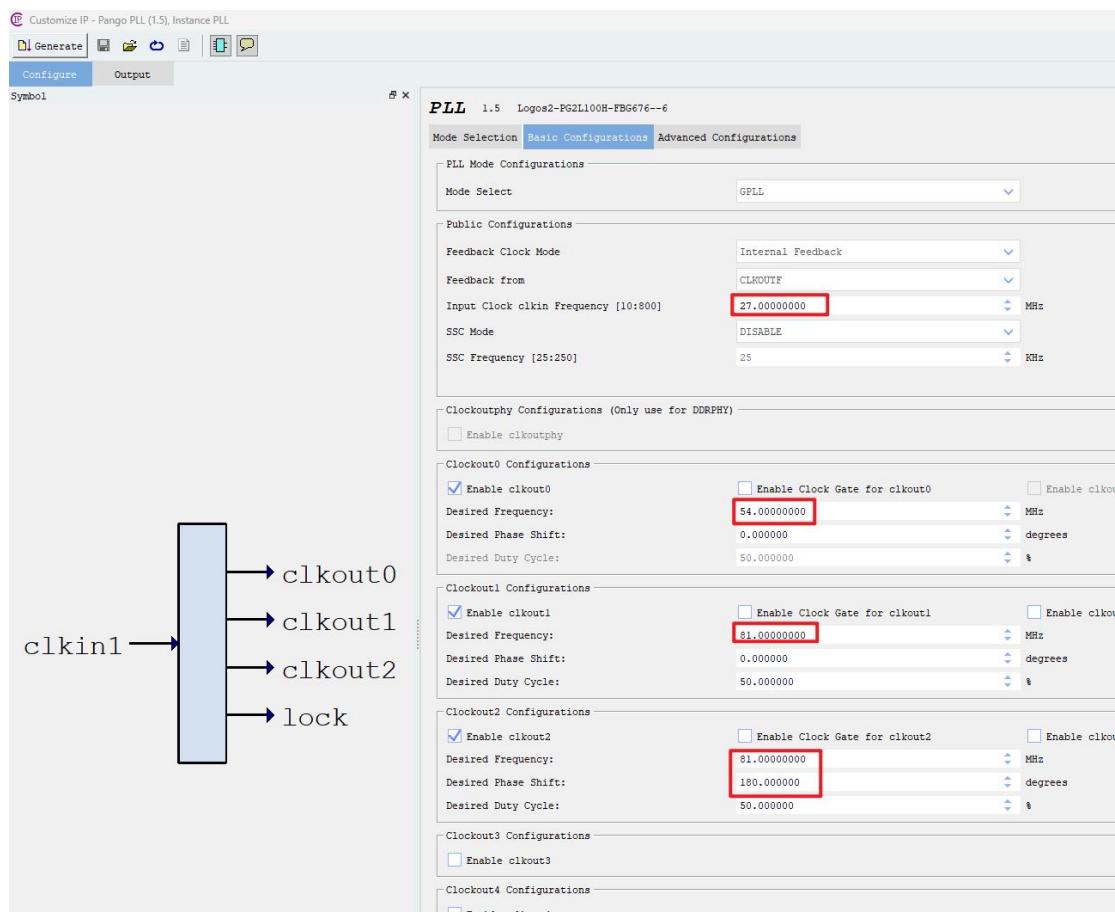

接下来进行基础配置:

在 Public Configurations 一栏将输入时钟频率设置为 27MHZ。

在 Clockout0 Configurations 选项卡下, 勾选使能 clkout0, 将输出频率设置为 54MHZ。

在 Clockout1 Configurations 选项卡下, 勾选使能 clkout1, 将输出频率设置为 81MHZ。

在 Clockout2 Configurations 选项卡下, 勾选使能 clkout2, 将输出频率设置为 81MHZ, 并设置相位偏移为 180 度。

其他选项可以使用默认设置, 若有其他需求可以查阅 IP 手册了解, 本实验我们暂介绍 IP 基本的使用方法:

图 5.2-4 IP 配置流程图 3

点击左上角 generate 生成 IP。

### 5.3. 代码设计

模块接口列表如下所示:

表 5.3-1 PLL IP 使用实验模块接口表

| 端口      | I/O    | 位宽 | 描述                             |

|---------|--------|----|--------------------------------|

| sys_clk | input  | 1  | 系统时钟                           |

| clkout0 | output | 1  | 54MHZ 时钟                       |

| clkout1 | output | 1  | 81MHZ 时钟                       |

| clkout2 | output | 1  | 81MHZ 时钟, 相位偏移 180 度           |

| lock    | output | 1  | 时钟锁定信号, 当为高电平时, 代表 IP 核输出时钟稳定。 |

PLL\_TEST 顶层代码:

```

1. module PLL_TEST(

2.     input      sys_clk      ,

3.     output     clkout0     ,

4.     output     clkout1     ,

5.     output     clkout2     ,

6.     output     lock

7. );

8.

9.     PLL PLL_U0 (

10.         .clkout0    (clkout0    ),// output

11.         .clkout1    (clkout1    ),// output

```

```

12.    .clkout2          (clkout2      ), // output

13.    .lock             (lock        ), // output

14.    .clkin1           (sys_clk     ) // input

15. );

16.

17.

18. endmodule

```

该模块的功能是例化 PLL IP 核, 功能简单, 在此不做说明。

PLL\_tb 测试代码:

```

1. timescale 1ns / 1ps

2.

3. module PLL_tb();

4. reg      sys_clk ;

5. wire     clkout0 ;

6. wire     clkout1 ;

7. wire     clkout2 ;

8. wire     lock      ;

9.

10.

11.

12. initial

13. begin

14. #2

```

```

15.           sys_clk <= 0  ;

16.       end

17.

18.   parameter CLK_FREQ = 27;//Mhz

19.   always #( 1000/CLK_FREQ/2 ) sys_clk = ~sys_clk ;

20.

21.

22.   PLL_TEST u_PLL_TEST(

23.     .sys_clk          (sys_clk      ),

24.     .clkout0          (clkout0    ),

25.     .clkout1          (clkout1    ),

26.     .clkout2          (clkout2    ),

27.     .lock             (lock        )

28. );

29.

30.

31. endmodule

```

timescale 定义了模块仿真的时间单位和时间精度。时间单位是 1 纳秒，精度是 1 皮秒。

initial 块负责初始化系统时钟。在仿真启动后的 2 纳秒，系统时钟 sys\_clk 被设置为 0。这是为了在仿真开始时定义一个已知的初始状态。

代码定义了一个时钟频率参数 CLK\_FREQ 为 27 MHz，并使用一个 always 块来翻转系统时钟信号。

always 块中的逻辑使得 sys\_clk 每 37 纳秒翻转一次，从而生成一个 27 MHz 的方波时钟信号。这种时钟信号用于驱动被测试的 PLL\_TEST 模块。

最后，将测试平台的各个信号连接到 PLL\_TEST 模块。这包括将生成的系统时钟 sys\_clk 连接到

PLL\_TEST 的时钟输入端, 并将 PLL\_TEST 的输出信号 clkout0、clkout1、clkout2 和 lock 使用 wire 引出观察。

#### 5.4. PDS 与 Modelsim 联合仿真

PDS 支持与 Modelsim 或 QuestaSim 等第三方仿真器的联合仿真, 而 Modelsim 是较为常用的仿真器, 使用 PDS 与 Modelsim 来进行联合仿真。

接下来选择 Project->Project Setting, 打开工程设置, 准备设置联合仿真。

图 5.4-1 PDS 和 Modelsim 联合仿真流程图 4

选择 Simulation 选项卡, 红框 1 选择刚才编译生成的仿真库的路径, 红框 2 选择 Modelsim 的启动路径, 之后点击 OK。

右键仿真的文件, 选择 Run Behavior Simulation 开始行为仿真。

图 5.4-2 PDS 和 Modelsim 联合仿真流程图 5

运行后会自动打开 Modelsim，并执行仿真，如果没有任何报错，则表示成功。如果出现错误，请检测 PDS 与 Modelsim 的配置。

```

#       PLL_tb

# End time: 11:10:22 on Feb 20,2025, Elapsed time: 0:00:00

# Errors: 0, Warnings: 0

# do {run_behav_simulate.tcl}

# vsim -novopt -L work -L usim -L adc_e2 -L ddc_e2 -L dll_e2 -L hsstlp_lane -L hsstlp_pll -L iolhr_df

# Start time: 11:10:22 on Feb 20,2025

# Loading work.PLL_tb

# Loading work pll_test

# Loading work.PLL

# Loading usim.GTP_GPLL

# Loading usim.GTP_GRS

# .main_pane.wave.interior.cs.body.pw.wf

# .main_pane.structure.interior.cs.body.struct

# .main_pane.objects.interior.cs.body.tree

VSIM 3>

```

图 5.4-3 PDS 和 Modelsim 联合仿真流程图 6

## 5.5. 实验现象

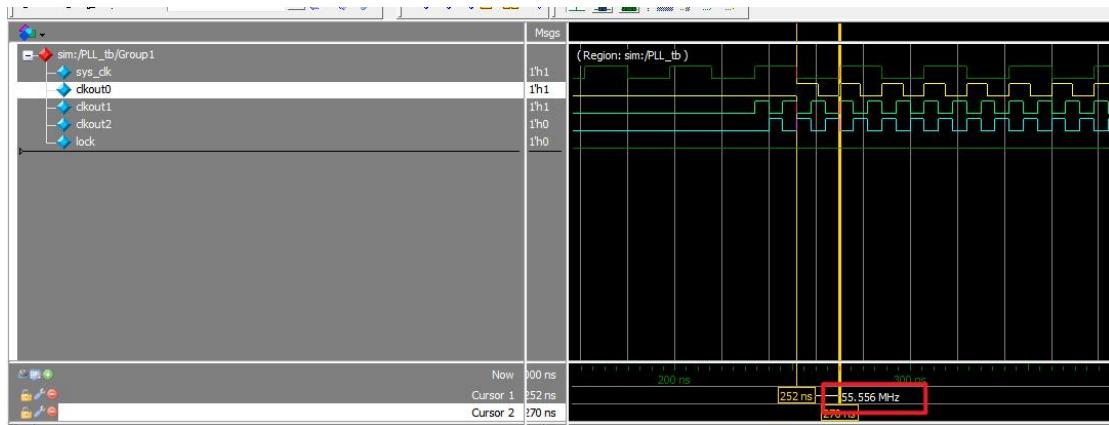

点击 Wave 观察 PLL 输出信号:

图 5.5-1 PLL IP 使用实验结果波形图 1

使用标尺测量 clkout0, 发现其一个时钟周期是 18ns, 也就是 55.556MHz。出现了偏差是因为 tb 生成的 27MHz 其实并不准确, 所以导致误差。

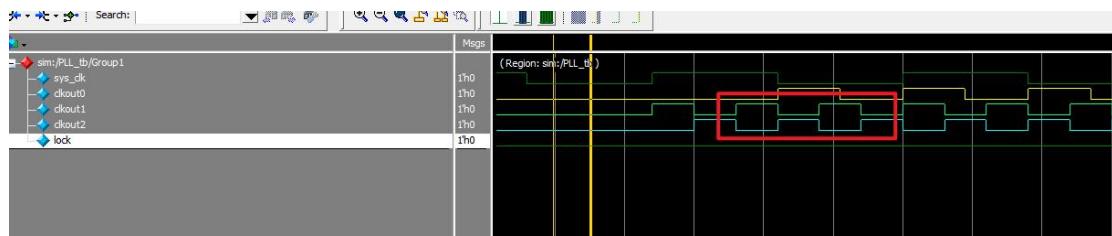

图 5.5-2 PLL IP 使用实验结果波形图 2

使用可以看到 clkout1 和 clkout2 相位偏差 180°, 符合设置。需要注意 PLL 的输出时钟应该在时钟锁定信号 lock 有效之后才能使用, lock 信号拉高之前输出的时钟是不确定的。

## 6. Pango 的 ROM、RAM、FIFO 的使用

### 6.1. 实验简介

实验目的:

掌握紫光平台的 RAM、ROM、FIFO IP 的使用

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP-MINI

## 6.2. 实验原理

不管是 Logos 系列或者是 Logos2 系列, 其 IP 配置以及模式和功能均一致, 不会像 PLL 那样有动态配置以及内部反馈选项的选择等之间的差异, 所以是 RAM、ROM、FIFO 是通用的。

### 6.2.1. RAM 介绍

RAM 即随机存取存储器。它可以在运行过程中把数据写进任意地址, 也可以把数据从任意地址中读出。其作用可以拿来做数据缓存, 也可以跨时钟, 也可以存放算法中间的运算结果等。

注意, PDS 的 IP 配置工具中提供两种不同的 RAM, 一种是 Distributed RAM(分布式 RAM)另一种是 DRM Based RAM, 分布式 RAM 用的是 LUT(查找表)资源去构成的 RAM, 这种 RAM 会消耗大量 LUT 资源, 因此通常在一些比较小的存储才会用到这种 RAM, 以节省 DRM 资源。而 DRM Based RAM 是利用片内的 DRM 资源去构成的 RAM, 不占用逻辑资源, 而且速度快, 通常设计中均使用 DRM Based RAM。

RAM 分为三种, 如下表所示:

表 6.2-1

| RAM 类型   | 特点                                   |

|----------|--------------------------------------|

| 单端口 RAM  | 只有一个端口可以读写。只有一个读写口和地址口               |

| 伪双端口 RAM | 有 wr 和 rd 两个端口, 顾名思义, wr 只能写, rd 只能读 |

| 真双端口 RAM | 提供 A 和 B 两个端口, 两个端口均可以独立进行读写         |

注意, 当使用真双端口时, 要避免出现同时读写同一个地址, 这会造成写入失败, 在逻辑设计上需要避开这个情况。

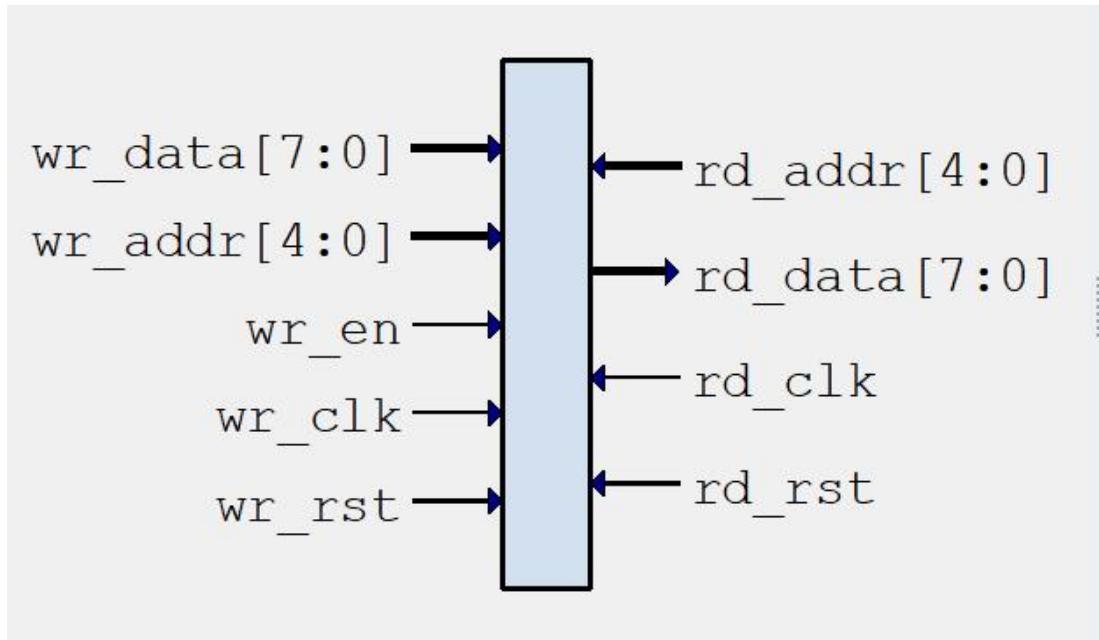

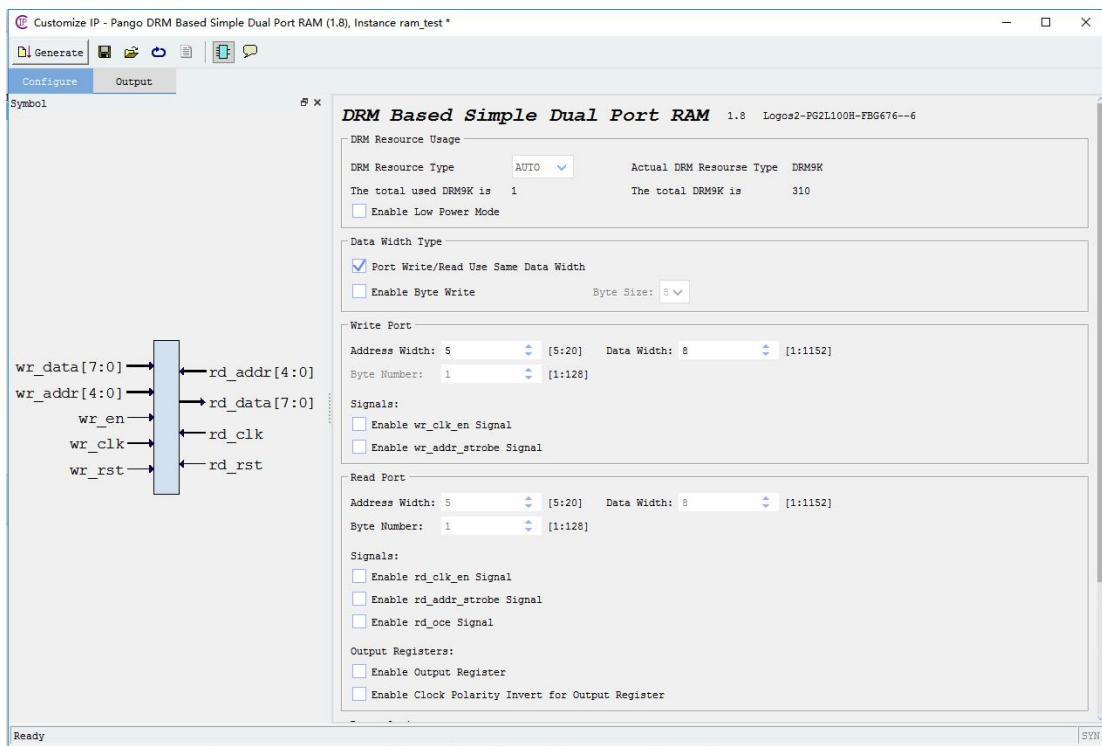

以下给出比较常用的 RAM 的配置作为介绍, 通常我们比较常用伪双端口 RAM 来设计, 如图 6.2-1 所示:

图 6.2-1

图 6.2-2 为 IP 配置:

图 6.2-2

注意, 如果勾选 Enable Output Register(输出寄存), 输出数据会延迟一个时钟周期。

具体每个端口的含义这里参考官方手册, 大家也可以自行查看 IP 手册, 如下图所示:

| 端口名            | 输入/输出 | 说明                                                                                         |

|----------------|-------|--------------------------------------------------------------------------------------------|

| wr_data        | 输入    | 写数据信号, 位宽范围1~1152                                                                          |

| wr_addr        | 输入    | 写地址信号, 位宽范围5~20                                                                            |

| wr_en          | 输入    | 写使能信号<br>1: 写使能<br>0: 读使能                                                                  |

| wr_clk         | 输入    | 写时钟信号                                                                                      |

| wr_clk_en      | 输入    | 写时钟使能信号<br>1: 对应地址有效<br>0: 对应地址无效                                                          |

| wr_RST         | 输入    | 写端口复位信号, 高有效                                                                               |

| wr_byte_en     | 输入    | Byte Write使能信号, 当配置“Enable Byte Write”选项勾选时有效, 位宽范围1~128。<br>1: 对应Byte值有效;<br>0: 对应Byte值无效 |

| wr_addr_strobe | 输入    | 写地址锁存信号<br>1: 对应地址无效, 上一个地址被保持<br>0: 对应地址有效                                                |

| rd_data        | 输出    | 读数据信号, 位宽范围1~1152                                                                          |

| rd_addr        | 输入    | 读地址信号, 位宽范围5~20                                                                            |

| rd_clk         | 输入    | 读时钟信号                                                                                      |

| rd_clk_en      | 输入    | 读时钟使能信号。<br>1: 对应地址有效;<br>0: 对应地址无效。                                                       |

| rd_RST         | 输入    | 读端口复位信号, 高有效                                                                               |

| rd_OCE         | 输入    | 读数据输出寄存使能信号<br>1: 对应地址有效, 读数据寄存输出<br>0: 对应地址无效, 读数据保持                                      |

| rd_addr_strobe | 输入    | 读地址锁存信号<br>1: 对应地址无效, 上一个地址被保持<br>0: 对应地址有效                                                |

图 6.2-3

DRM Resource Type: 用于配置所建 RAM IP 核用的是哪种资源, 不同芯片型号可选资源是不一样的, 有的是 9K, 有的是 18K, 有的是 36K, 如果没有特殊情况, 直接 AUTO 即可。

### 6.2.1.1. RAM 的读写时序

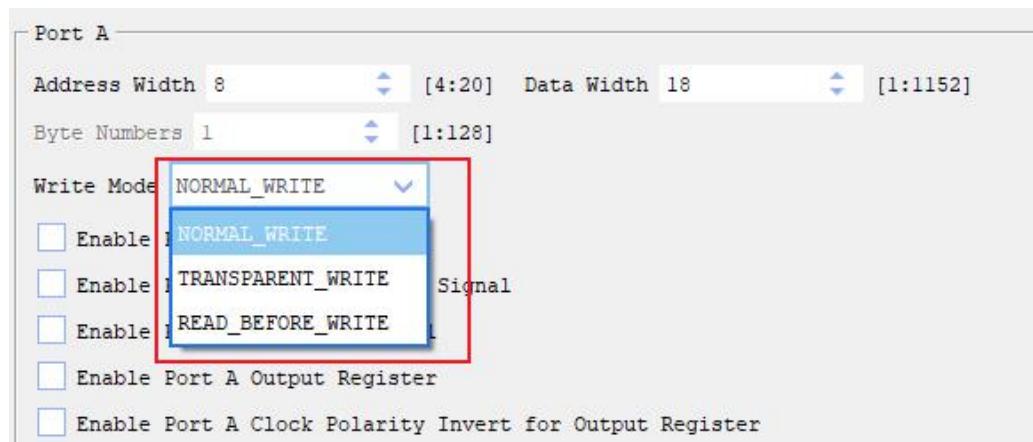

配置成不同模式的时候, RAM 的读写时序是不一样的, 真双端口和单端口的 RAM 配置均有三种模式, 而伪双端口只有一种。由于真双端口和单端口的配置是一样的, 这里以真双端口为例子。

分为 NORMAL\_WRITE(正常模式)、TRANSPARENT\_WRITE(直写)、READ\_BEFORE\_WRITE(读优先模式)三种

模式。

图 6.2-4

而伪双端口不属于上面三种模式, 有它独特的模式。这几种模式的差异就在于读写时序的不同, 接下来, 我们来分析读写时序。

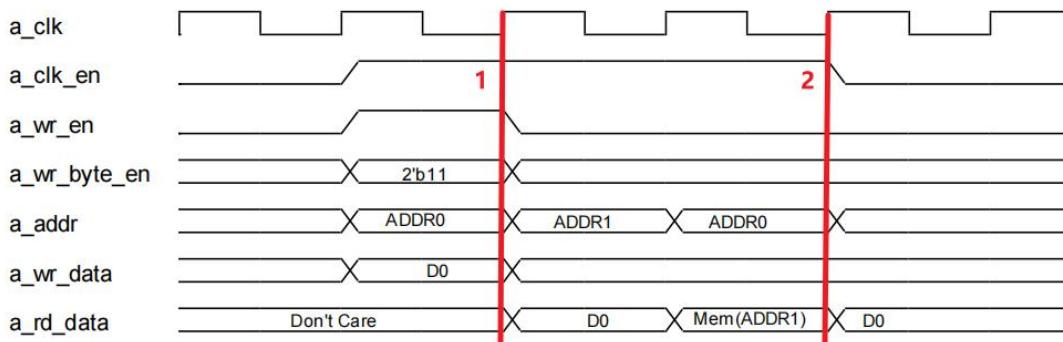

以下时序图均来自官方 IP 手册, 并且均未使能输出寄存。注意 wr\_en 为 1 时表示写数据, 为 0 表示读数据。

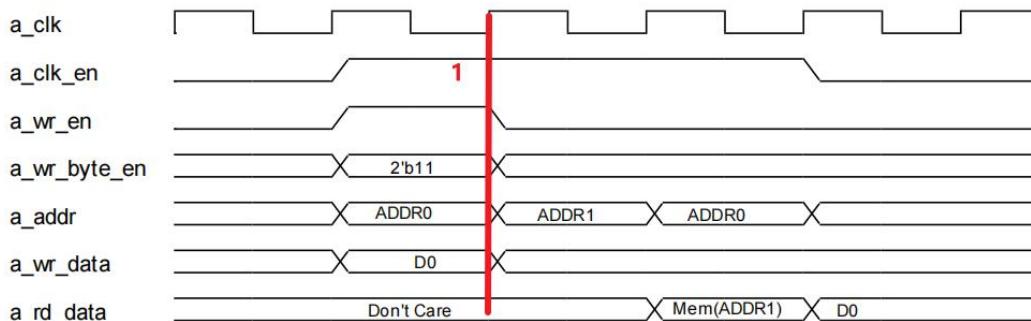

#### 6.2.1.1.1. NORMAL\_WRITE

图 6.2-5

在 NORMAL\_WRITE 这种模式下, 可以看到, 当时钟的上升沿到来, 且 clk\_en 和 wr\_en 均为高电平时, 就会把数据写到对应的地址里面, 如图中的 1 时刻。然后看读数据端口, 当 wr\_en 不为 0 的时候, a\_rd\_data 一直为 Don't Care 状态, 而当时钟上升沿到来, 且 clk\_en 为高电平, wr\_en 为低电平时, a\_rd\_data 输出当前 a\_addr 里的数据, 即 Mem(ADDR1)和 ADDR0 里的 D0。

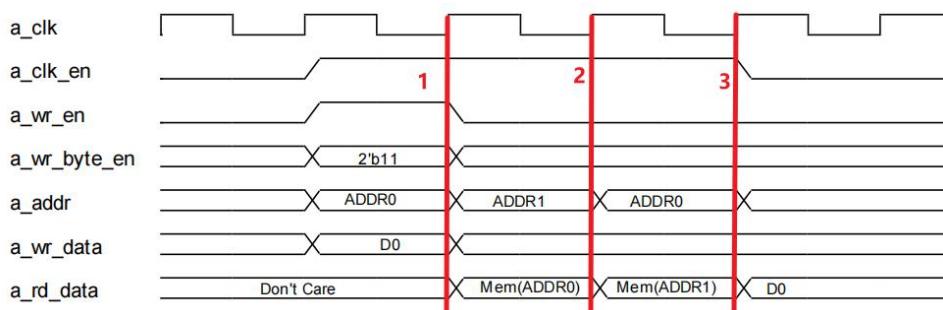

#### 6.2.1.1.2. READ\_BEFORE\_WRITE

图 6.2-6

在 READ\_BEFORE\_WRITE 这种模式下, 可以看到在 1 的时刻, 时钟上升沿到来, 且 clk\_en 和 wr\_en 均为高电平, D0 写进了 ADDR0 里面, 但是注意看此时的 a\_rd\_data 和 a\_addr, 可以发现, 此时 a\_wr\_en 并不为 0, 可 a\_rd\_data 还是输出了上一刻 ADDR0 的数据(因为不是输出 D0)。之后, a\_wr\_en 拉低, 此时才是读数据, 在 3 时刻, 把 ADDR0 的数据读出来, a\_rd\_data 才输出了 D0。

所以总结一下, 这个模式其实就是进行写操作时, 读端口会把当前写的地址的原始数据输出, 因此叫读优先模式很合情合理对吧, 顾名思义, 就是我优先把原来的数据读出来。

#### 6.2.1.1.3. Transparent\_Write

图 6.2-7

在 Transparent\_Write 这种模式下, 可以看到在 1 的时刻, 时钟上升沿到来, 且 clk\_en 和 wr\_en 均为高电平, D0 写进了 ADDR0 里面, 但是注意看此时的 a\_rd\_data 和 a\_addr, 可以发现, 此时 a\_wr\_en 并不为 0, 可 a\_rd\_data 居然直接输出了 D0, 之后 a\_wr\_en 拉低, 进入读状态, 在 2 时刻, 再一次把 ADDR0 的数据读出来, 输出了 D0。

分析总结一下, 根据 1 时刻的情况, 我们可以得出结论, 在这种模式下, 当我们进行写操作时, 读端口会马上输出我们写入的数据。所以叫直写模式。

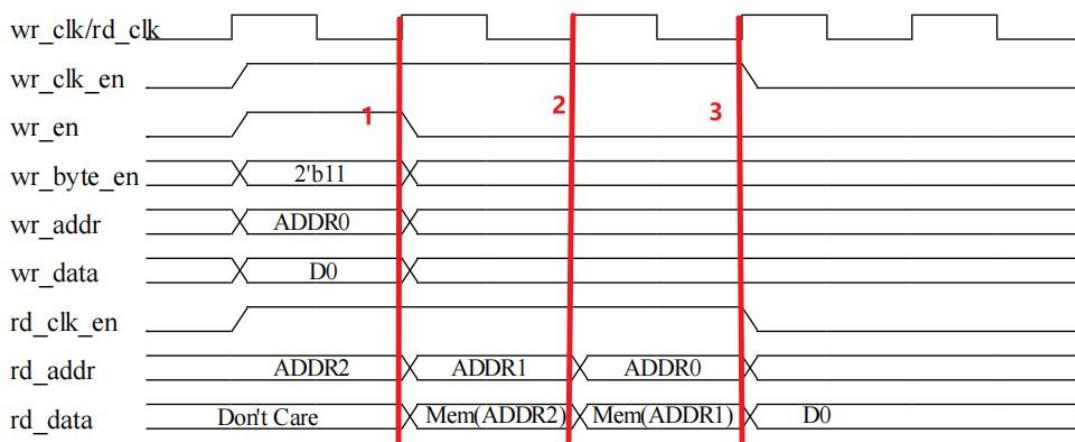

#### 6.2.1.1.4. 伪双端口的读写时序

注意: wr\_en 为 1 时是写操作, 为 0 是读操作。

伪双端口的读写时序与上面三种都不同, 我们看图 8 的时序来分析:

图 6.2-8

注意看 1 时刻, 此时 wr\_en 和 wr\_clk\_en 均为高电平, 所以是写操作, 所以 1 时刻就是往地址 ADDR0 里写

入 D0, 注意此时的 rd\_addr 和 rd\_data, 可以看到这一时刻 rd\_addr 是 ADDR2, 然后进行写操作时, rd\_data 同样输出了 ADDR2 里的数据, 而此时 wr\_en 还是高电平。接下来看 2 和 3 时刻, 此时 wr\_en 为 0, rd\_clk\_en 是高电平, 所以是读操作, 此时分别读出 ADDR1 和 ADDR0 里的数据, 之后 rd\_clk\_en 变成低电平, 读时钟无效, 可以看到 rd\_data 保持 D0 输出。

分析总结一下, 主要是 1 时刻, 大家可以看到 1 时刻往 ADDR0 写入了 D0, 读端口却输出了 ADDR2 中的数据。仔细观察可以得出结论: 伪双端口 RAM 在进行写操作的时候, 会把当前读端口指向的地址的数据输出。是不是有点像直写? 只不过直写是输出写入的数据, 而伪双端口是输出读端口指向的地址的数据。

具体大家可以结合视频讲解。

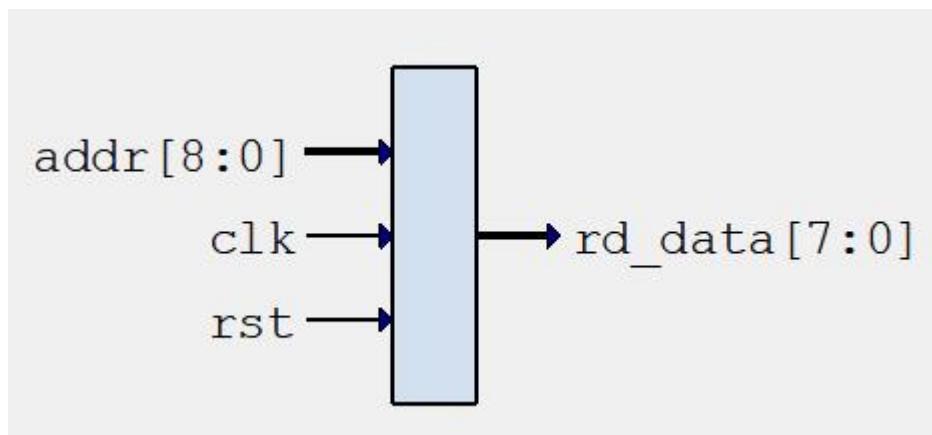

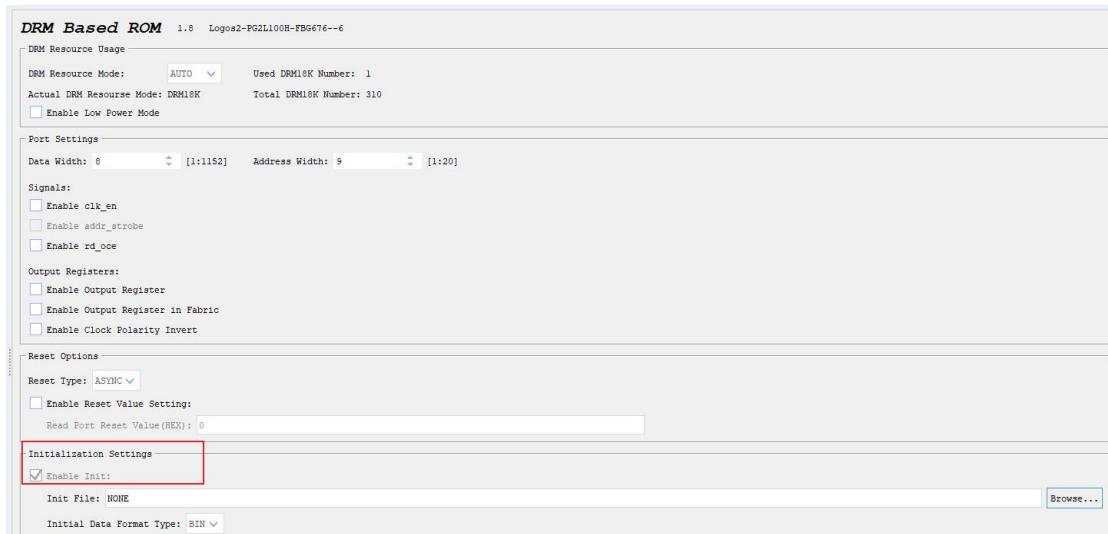

### 2.1.1.2 ROM 介绍

ROM 即只读存储器, 在程序的运行过程中他只能被读取, 无法被写入, 因此我们应该在初始化的时候就给他配置初值, 一般是在生成 IP 的时候通过导入.dat 文件对其进行初值配置。

注意, PDS 的 IP 配置工具中提供两种不同的 ROM, 一种是 Distributed ROM(分布式 ROM)另一种是 DRM Based ROM, 分布式 ROM 用的是 LUT(查找表)资源去构成的 ROM, 这种 ROM 会消耗大量 LUT 资源, 因此通常在一些比较小的存储才会用到这种 RAM, 以节省 DRM 资源。而 DRM Based ROM 是利用片内的 DRM 资源去构成的 ROM, 不占用逻辑资源, 而且速度快, 通常设计中均使用 DRM Based ROM。

以下给出比较常用的 ROM 的配置作为介绍, 由于只能读, 因此其均为单端口 ROM 如图 6.2-9 所示:

图 6.2-9

下图为 IP 配置:

图 6.2-10

注意, 如果勾选 Enable Output Register(输出寄存), 输出数据会延迟一个时钟周期。

同时, 可以看到 Enable Init 选项是默认勾选的, 并且不可取消。

图 6.2-11

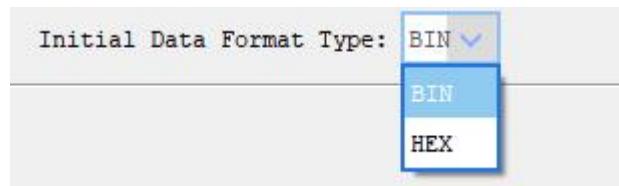

导入的数据的格式只能为二进制或者是十六进制。

具体每个端口的含义这里参考官方手册, 大家也可以自行查看 IP 手册, 如图 6.2-12 所示:

| 端口          | I/O | 描述                                          |

|-------------|-----|---------------------------------------------|

| addr        | I   | 读地址信号。                                      |

| addr_strobe | I   | 读地址锁存信号。<br>1: 对应地址无效, 地址被保持;<br>0: 对应地址有效。 |

| rd_data     | O   | 读数据信号。                                      |

| clk         | I   | 时钟信号。                                       |

| clk_en      | I   | 时钟使能信号。<br>1: 对应地址有效;<br>0: 对应地址无效。         |

| rst         | I   | 复位信号。<br>1: 复位;<br>0: 复位释放。                 |

| rd_oce      | I   | 输出寄存使能信号。<br>1: 读数据寄存输出;<br>0: 寄存输出数据保持。    |

图 6.2-12

可以看到图 6.2-12 给出的是完整的接口列表, 一般我们只需要 addr、rd\_data、clk、rst 这四个信号即可。以下时序图均来自官方 IP 手册, 并且均未使能输出寄存。

### 6.2.1.2. ROM 的读时序

图 6.2-13

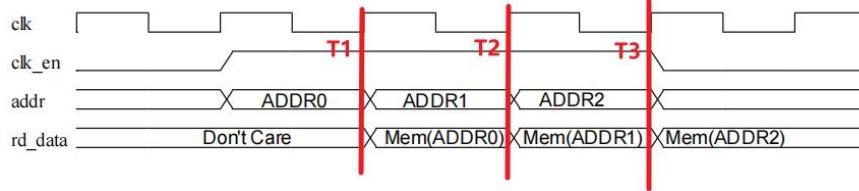

可以看到该时序是非常简单的, 比如在 T1 时刻, 当 clk 上升沿到来时, 且 clk\_en 为高电平时, 给出要读出的地址, rd\_data 就会输出数据, 在不勾选输出使能寄存的情况下, rd\_data 的输出会有延迟, 具体时间可以从仿真里看到, 所以我们在下个时钟周期的上升沿即 T2 时刻的上升沿才能获取到 ROM 读出的值。

所以整体时序非常简单, 如果勾选了 clk\_en 信号, 就要给 clk\_en 高电平才能读数据, 如果不勾选 clk\_en 信号, 就一直根据地址读取 ROM 数据。

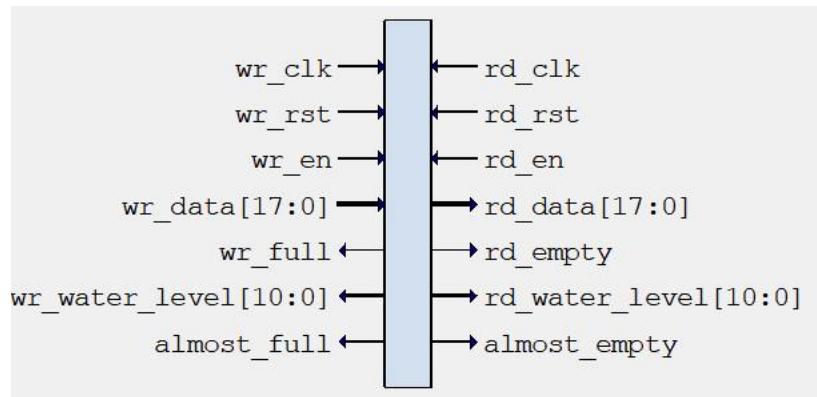

### 6.2.2.FIFO 介绍

FIFO 即先入先出, 在 FPGA 中, FIFO 的作用就是对存储进来的数据具有一个先入先出特性的一个缓存器, 经常用作数据缓存或者进行数据跨时钟域传输。FIFO 和 RAM 最大的区别就是 FIFO 不需要地址, 采用的是顺序写入, 顺序读出。

在紫光的 IP 工具中又分为 Distribute FIFO 和 DRM FIFO, 其实就是用不同的资源去构成, 前者 Distribute FIFO 也就是分布式 FIFO, 使用的是片上的 LUT 资源去构成, 而 DRM FIFO 使用的是片上的 DRM 资源去构成, DRM 构成的 FIFO 其性能大于 LUT 资源构成的, 不仅容量更大, 且可配置更多功能。

本章着重介绍 DRM Based FIFO。

注意: FIFO 写满后禁止继续写入数据, 否则将会写溢出。

注意: FIFO 读空后禁止继续读数据, 否则将会读溢出。

以下给出常用的 FIFO 的配置作为介绍。

图 6.2-14

图 6.2-15

注意, 如果勾选 Enable Output Register(输出寄存), 输出数据会延迟一个时钟周期。

FIFO Type 有 SYNC 和 ASYNC 两种, 第一种是同步 FIFO, 读写端口共用一个时钟和复位, 另一种是异步 FIFO, 读写时钟和复位均独立。在平常设计中, 比较常用的是异步 FIFO, 因为同步 FIFO 和异步 FIFO 的读写时序一模一样, 只有读写端口的时钟复位有差异, 当异步 FIFO 的读写端口使用相同的时钟和复位, 此时异步 FIFO 和同步 FIFO 基本是一致的。

Reset Type 也可以选择 SYNC 和 ASYNC 两种, SYNC 模式下需要时钟的上升沿采样到复位有效才会复位, 而在 ASYNC 模式下, 复位一旦有, FIFO 立即复位。

其余端口说明引用官方 IP 手册, 如图 6.2-16 所示:

| 端口名            | 输入/输出 | 说明                                                                                         |

|----------------|-------|--------------------------------------------------------------------------------------------|

| wr_data        | 输入    | 写数据信号, 位宽范围1~1152                                                                          |

| wr_en          | 输入    | 写使能信号, 高有效                                                                                 |

| wr_byte_en     | 输入    | Byte Write使能信号, 当配置“Enable Byte Write”选项勾选时有效, 位宽范围1~128。<br>1: 对应Byte值有效;<br>0: 对应Byte值无效 |

| clk            | 输入    | 同步FIFO时钟信号, 仅同步FIFO有效                                                                      |

| rst            | 输入    | 同步FIFO复位信号, 高有效, 仅同步FIFO有效                                                                 |

| wr_clk         | 输入    | 异步FIFO写时钟信号, 仅异步FIFO有效                                                                     |

| wr_RST         | 输入    | 异步FIFO写复位信号, 高有效, 仅异步FIFO有效                                                                |

| wr_full        | 输入    | FIFO Full信号<br>1: FIFO满<br>0: FIFO未满                                                       |

| almost_full    | 输出    | FIFO Almost Full信号<br>1: FIFO将满<br>0: FIFO未将满                                              |

| wr_water_level | 输出    | 写端口water level信号, 位宽范围5~20, 表示写数据水位                                                        |

| rd_data        | 输出    | 读数据信号                                                                                      |

| rd_en          | 输出    | 读使能信号                                                                                      |

| rd_clk         | 输入    | 异步FIFO读时钟信号, 仅异步FIFO有效                                                                     |

| rd_RST         | 输入    | 异步FIFO读复位信号, 仅异步FIFO有效                                                                     |

| rd_empty       | 输入    | FIFO Empty信号<br>1: FIFO空<br>0: FIFO未空                                                      |

| almost_empty   | 输出    | FIFO Almost Empty信号<br>1: FIFO将空<br>0: FIFO未将空                                             |

| rd_water_level | 输出    | 读端口water level信号, 位宽范围5~20, 表示读数据水位                                                        |

| rd_oce         | 输入    | 输出寄存使能信号<br>1: 对应地址有效, 读数据寄存输出<br>0: 对应地址无效, 读数据保持                                         |

图 6.2-16

其中 rd\_water\_level 和 wr\_water\_level 分别代表“可读的数据量”和“已写入的数据量”, 其含义与 Xilinx 的 FIFO 的 wr\_data\_count 和 rd\_data\_count 是一致的。

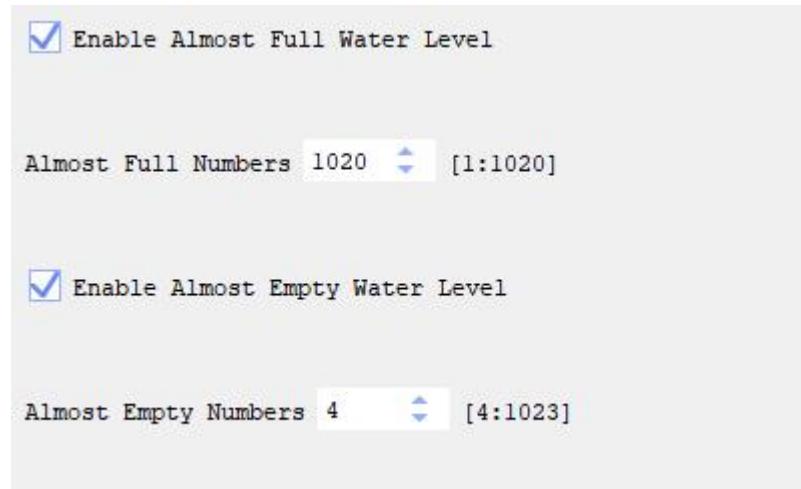

图 6.2-17

当我们勾选 Enable Almost Full Water Level 和 Enable Almost Empty Water Level 后，才能看到 rd\_water\_level 和 wr\_water\_level，而下面的 Almost Full Numbers 的设置是表示当写入 1020 个数据时，Almost Full 信号就会拉高，Almost Empty Numbers 的设置表示当可读数据剩下 4 个时 Almost Empty 信号就会拉高。

同时 FIFO 支持混合位宽，例如写端口 16bit，读端口 8bit。如果写入 16'h0102，那么读出来会是 8'h02,8'h01，会先读出低位。

如果写端口 8bit，读端口 16bit。当写入 8'h01,8'h02 时，读出来是 16'h0201，先写入的数据存放在低位。

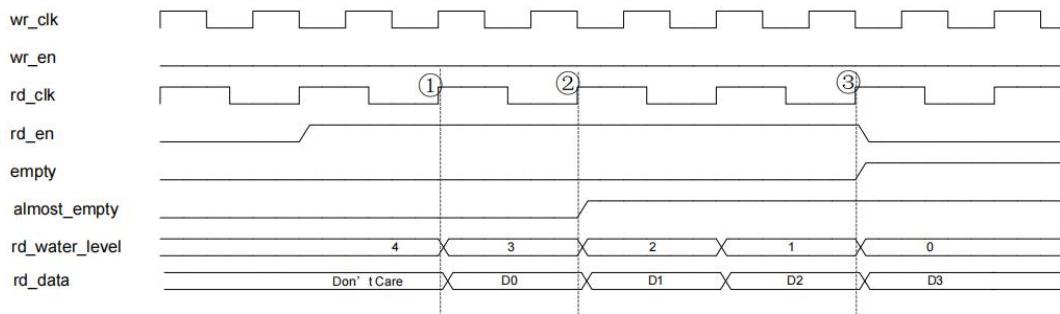

### 6.2.2.1. 的读写时序

因为同步 FIFO 和异步 FIFO 的读写时序一致，这里用异步 FIFO 的读写时序图来做介绍。

注意：复位时高电平有效。读出数据均未勾选 Enable Output Register(输出寄存)。

#### 6.2.2.1.1. FIFO 未满时的写时序

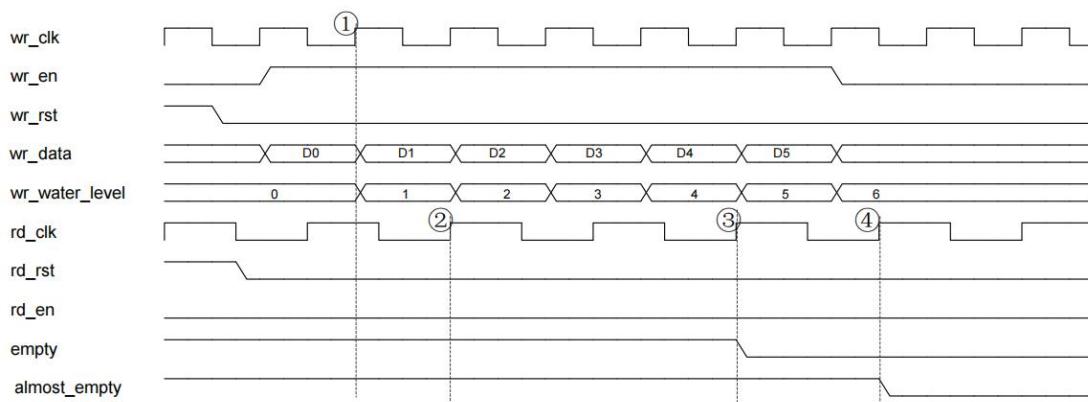

图 6.2-18

可以看到在 1 时刻，复位信号为低电平，处于工作状态，此时在 wr\_clk 的上升沿且 wr\_en 为高电平时将数据 D0 写入 FIFO，wr\_water\_level 也从 0 变 1，表示已经写入了一个数据，此时注意看读端口的 empty 信号，在 3 时刻 empty 信号从高变低，意味着读端口已经有数据可以读了，FIFO 不再为空，而注意看，rd\_clk 和 wr\_clk

是不一样的, 从 1 写入到 3 时刻 empty 拉低时, 经过了 3 个 rd\_clk。

所以这里我们可以得出结论: rd\_water\_level 要滞后 wr\_water\_level 三个 rd\_clk。

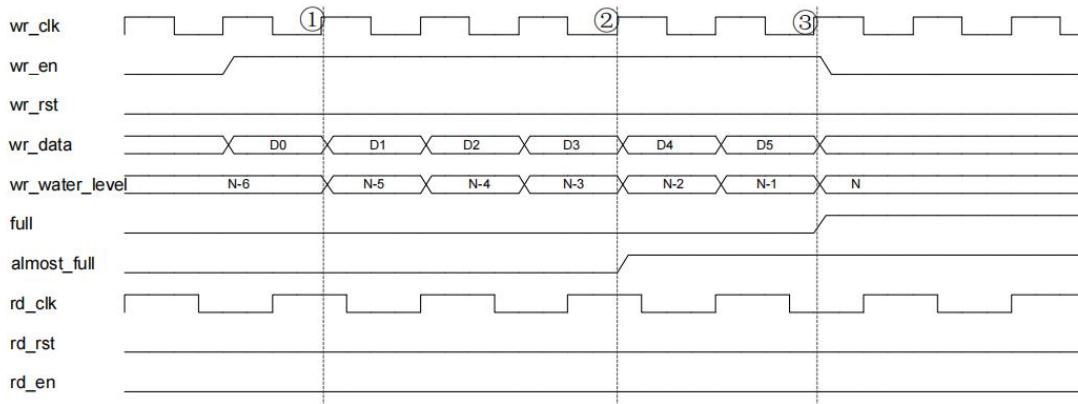

### 6.2.2.1.2. FIFO 将满时的写时序

图 6.2-19

将满时主要分析 full 和 almost\_full 信号。假设 Almost Full Numbers 设置为 N-2, 在 1 时刻, 此时已经写入了 N-6 个数据, 意味着再写 6 个数据 FIFO 就满了, 从 1 时刻到 2 时刻一共写入了 4 个数据, 因此当 wr\_water\_level 变成 N-2 时, 满足条件, 可以看到 Almost Full 信号拉高, 再写两个数据 FIFO 就满了, 所以再经过两个时钟周期后, Full 信号拉高。

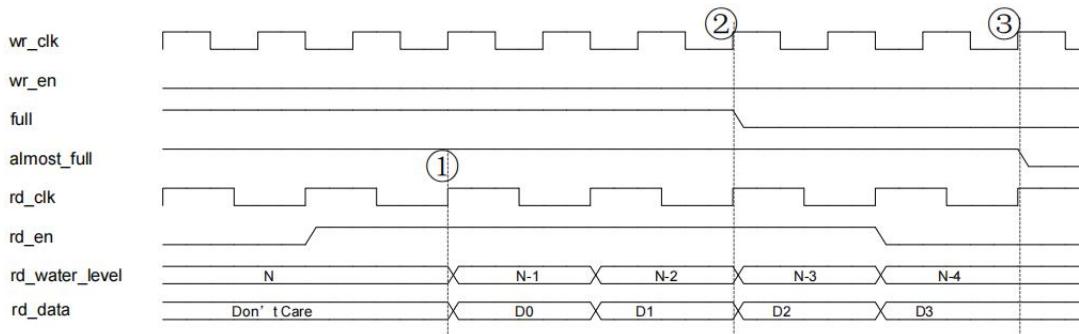

### 6.2.2.1.3. FIFO 在满状态下的读时序

图 6.2-20

在满状态下,FIFO 已经有 N 个数据了,此时在 1 状态下,rd\_clk 的上升沿,且 rd\_en 为高电平时,此时从 FIFO 里读出数据(数据的输出有延时,仿真中延时 0.2ns)。此时 rd\_water\_level 变成 N-1, rd\_data 输出 D0。然后看 2 时刻, full 信号拉低,此时可以看以下,在 1 时刻到 2 时刻期间一共经过了 3 个 wr\_clk 写端口才能判断到此时数据量已经不为满。所以我们可以得出结论, wr\_water\_level 要滞后 rd\_water\_level 三个 wr\_clk。

#### 6.2.2.1.4. FIFO 将空时的读时序

图 6.2-21

在 1 时刻, 可读的数据量剩下 4, 假设 Almost Empty Number 设为 2, 在 1 时刻和 2 时刻分别读出了两个数据, 所以在 2 时刻下, 可读数据量剩下两个, 达到 Almost Empty Number 触发条件, 因此 almost\_empty 信号拉高, 再过两个时钟周期, 即再读两个数据, FIFO 将变成空状态, 也就是状态 3, 此时 empty 信号拉高。

### 6.3. 接口列表

该部分介绍每个顶层模块的接口。

ram\_test\_top.v

| 端口      | I/O    | 位宽 | 描述          |

|---------|--------|----|-------------|

| wr_clk  | input  | 1  | 写时钟         |

| rd_clk  | input  | 1  | 读时钟         |

| rst_n   | input  | 1  | 全局复位        |

| rw_en   | input  | 1  | 1:写操作 0:读操作 |

| wr_addr | input  | 5  | 写地址         |

| rd_addr | input  | 5  | 读地址         |

| Wr_data | input  | 8  | 写入 RAM 的数据  |

| Rd_data | output | 8  | 从 RAM 读出的数据 |

rom\_test\_top.v

| 端口      | I/O   | 位宽 | 描述          |

|---------|-------|----|-------------|

| rd_clk  | input | 1  | 读时钟         |

| rst_n   | input | 1  | 全局复位        |

| rd_addr | input | 10 | 读地址         |

| rd_data | input | 64 | 从 ROM 读出的数据 |

fifo\_test\_top.v

| 端口             | I/O    | 位宽 | 描述             |

|----------------|--------|----|----------------|

| sys_clk        | input  | 1  | 写/读时钟          |

| rst_n          | input  | 1  | 全局复位           |

| wr_data        | input  | 8  | 写入 FIFO 的数据    |

| wr_en          | input  | 1  | 写使能            |

| rd_en          | input  | 1  | 读使能            |

| wr_water_level | output | 8  | 已写入 FIFO 的数据量  |

| rd_water_level | output | 8  | 可从 FIFO 读出的数据量 |

| Rd_data        | output | 8  | 从 FIFO 读出的数据   |

## 6.4. 工程说明

暂无

## 6.5. 代码仿真说明

本次的顶层模块实际就是例化 IP, 然后把端口引出而已, 主要代码都在 testbench 里面, 所以我们直接介绍仿真代码。

### 6.5.1. RAM 仿真测试

```

`timescale 1ns/1ns

module ram_test_tb();

reg sys_clk;

reg rd_clk ;

reg rst_n;

reg rw_en; //读写使能信号

reg [7:0] wr_data;

reg [4:0] wr_addr;

reg [4:0] rd_addr;

wire [7:0] rd_data;

reg [1:0] state;

initial

```

```

begin

rst_n  <=  1'd0;

sys_clk <=  1'd0;

rd_clk  <=  1'd0;

#20

rst_n  <=  1'd1;

end

//读写控制

always@(posedge sys_clk or negedge rst_n)  begin

if(!rst_n)

begin

state  <=  2'd0;

wr_data <=  8'd0;

rw_en  <=  1'd0;

wr_addr <=  8'd0;

rd_addr <=  8'd0;

end

else

begin

case(state)

2'd0:begin

rw_en  <=  1'd1;

state  <=  2'd1;

end

2'd1:begin

if(wr_addr == 5'd31)

begin

rw_en  <=  1'd0;

state  <=  2'd2;

wr_data <=  8'd0;

wr_addr <=  5'd0;

rd_addr <=  5'd0;

end

end

endcase

end

end

end

```

```

else

begin

state  <=  2'd1;

wr_data <=  wr_data+1'b1;

rd_addr <=  rd_addr+1'b1;

wr_addr <=  wr_addr+1'b1;

end

end

2'd2:begin

if(rd_addr == 5'd31)

begin

state  <=  2'd3;

rd_addr <=  5'd0;

end

else

begin

state  <=  2'd2;

rd_addr <=  rd_addr+1'b1;

end

end

2'd3:begin

state  <=  2'd0;

end

default: state  <=  2'd0;

endcase

end

end

//50MHZ

always#10 sys_clk = ~sys_clk;

//

GTP_GRS GRS_INST(

.GRS_N(1'b1)

);

```

```

ram_test_top u_ram_test_top(

.wr_clk ( sys_clk ),

.rd_clk ( sys_clk ),

.rst_n ( rst_n ),

.rw_en ( rw_en ),

.wr_addr ( wr_addr ),

.rd_addr ( rd_addr ),

.wr_data ( wr_data ),

.rd_data ( rd_data )

);

endmodule

```

涉及到 tb 的一些基础操作这里就不再详细讲解, 只关注重点逻辑部分。从代码的 27 行到 80 行是 ram 的读写控制状态机。主要用来控制读写地址的生成和使能以及写入的数据。这里只讲解主要实现的功能, 首先代码的 38-42 行, 也就是 state=0 的时候, 拉高 rw\_en, 并跳转到状态 1, 此时进入写操作(没有使能 clk\_en, 可以不管), 下个时钟周期开始写入数据(注意是时序逻辑, 边沿采样, 所以是下个时钟周期才开始写数据), 即 state=1 的时候是一直在往 ram 里面写数据, 在代码的 44 到 60 行就是写操作了, 可以看到, 当 wr\_addr 不等于 31 的时候, wr\_data 和 wr\_addr 不断加 1(rd\_addr 这里+1, 可以看视频讲解, 主要为了验证伪双端口的时序), 当 wr\_addr 等于 31 的时候, 在下个时钟周期把数据清 0, 状态跳转, 在当前时钟周期下还会再往地址 31 里面写入数据, 所以在该时钟周期, 一共写入了 32 个数据(从地址 0 写到地址 31)。即状态 1 完成写入 32 个数据后跳转到 state=2 的逻辑。代码的 61-72 行, 也就是 state=2 的时候, 在每个周期的上升沿让 rd\_addr 不断累加, 直到 rd\_addr=31 的时候, 在下个时钟周期清空地址并让状态跳转的操作, 而在当前时钟周期会继续把地址 31 的数据读出来, 完成读取地址 0-31 的数据, 一共 32 个数据, 所以该状态主要完成读取 32 个数据, 然后在下个时钟周期就跳转到 state=3。state=3 可以看到其主要作用就是等待一个时钟周期, 然后跳转回去 state=0 下, 起到一个延时作用。

具体波形大家可以看视频仿真, 或者自己尝试仿真, 根据波形来看代码。因为这里是时序逻辑, 所以如果是初学者, 纯看文字可能会对 rd\_addr=31 这一时刻还会再读一个数据感到疑惑, 建议直接仿真, 或者观看视频讲解的仿真部分, 可以帮助快速理解。

可以总结出一句话就是**时序逻辑的赋值总在下一个时钟周期才生效**, 所以在 rd\_addr=31 时执行的操作要在下一个时钟周期才会被采样生效。所以当前时钟还是会从 RAM 读出一个数据。

仿真代码的讲解到此结束, 大家要注意时序逻辑的特点, 具体的内容请看视频讲解。

### 6.5.2. ROM 仿真测试

```

`timescale 1ns/1ns

module rom_test_tb();

reg  sys_clk;

reg  rst_n;

reg [9:0] rd_addr;

```

```

wire [63:0] rd_data;

initial

begin

rst_n <= 1'd0;

sys_clk <= 1'd0;

#20

rst_n <= 1'd1;

end

//50MHZ

always#10 sys_clk = ~sys_clk;

//

GTP_GRS GRS_INST(

.GRS_N(1'b1)

);

always@(posedge sys_clk or negedge rst_n) begin

if(!rst_n)

rd_addr <= 10'd0;

else

rd_addr <= #2 rd_addr + 1'b1;

end

rom_test_top u_rom_test_top(

.rd_clk ( sys_clk ),

.rst_n ( rst_n ),

.rd_addr ( rd_addr ),

.rd_data ( rd_data )

);

endmodule

```

代码 31-36 行例化了 ROM 的顶层模块, 该模块里面其实只是调用了 ROM IP, 然后把信号引出端口, 没有任何逻辑操作。

代码 24-29 行通过一个 always 块不断生成地址, 任何给到 ROM IP, 将数据读出, 由于没勾选 clk\_en 信号, 所以数据在 ROM 复位完成后就会不断读出。所以并没有复杂的逻辑, 就是让地址从 0 不断累加, 把数据读出。

仿真代码的讲解到此结束, 大家要注意时序逻辑的特点, 具体的内容请看视频讲解。

### 6.5.3. FIFO 仿真测试

```

'timescale 1ns/1ns

module fifo_test_tb();

reg sys_clk;

reg rst_n;

reg [7:0] wr_data;

reg wr_en;

reg rd_en;

reg rd_state; //读状态

reg wr_state;

wire [7:0] rd_data;

reg [7:0] rd_cnt;

wire [7:0] rd_water_level;

wire [7:0] wr_water_level;

initial

begin

rst_n <= 1'd0;

sys_clk <= 1'd0;

#20

rst_n <= 1'd1;

end

always#10 sys_clk = ~sys_clk; //50MHZ

```

```

always@(posedge sys_clk or negedge rst_n) begin

if(!rst_n)

begin

wr_state  <= 1'd0;

wr_en   <= 1'd0;

wr_data <= 8'd0;

end

else

begin

case(wr_state)

1'd0: if(wr_water_level == 127) //128 个数据

begin

wr_en  <= #2 1'd0;

wr_data <= #2 8'd0;

wr_state <= #2 1'd1;

end

else

begin

wr_en  <= #2 1'd1;

wr_data <= #2 wr_data+1'b1;

wr_state <= #2 1'd0;

end

1'd1: if(rd_cnt == 127)

wr_state  <= #2 1'd0;

default: wr_state  <=1'd0;

endcase

end

end

always@(posedge sys_clk or negedge rst_n) begin

if(!rst_n)

begin

rd_state<= 1'd0;

```

```

rd_en  <= 1'd0;

rd_cnt <= 8'd0;

end

else

begin

case(rd_state)

1'd0: if(rd_water_level >= 8'd128) //等待 128 个数据

begin

rd_state  <= #2 1'd1;

rd_en     <= #2 1'd1;

end

else

begin

rd_cnt   <= #2 8'd0;

rd_state  <= #2 1'd0;

end

1'd1: begin

rd_cnt <= #2 rd_cnt + 1'b1;

if(rd_cnt == 127)

begin

rd_en     <= #2 1'd0;

rd_state  <= #2 1'd0;

end

end

default: rd_state  <= 1'd0;

endcase

end

end

GTP_GRS GRS_INST(

.GRS_N(1'b1)

);

fifo_test_top u_fifo_test_top(

```

```

.sys_clk      ( sys_clk      ),

.rst_n        ( rst_n       ),

.wr_data      ( wr_data      ),

.wr_en        ( wr_en       ),

.rd_en        ( rd_en       ),

.wr_water_level ( wr_water_level ),

.rd_water_level ( rd_water_level ),

.rd_data      ( rd_data      )

);

endmodule

```

涉及到 tb 的一些基础操作这里就不再详细讲解, 只关注重点逻辑部分。整个设计分为读写两个状态的控制。分别完成了写入 128 个数据, 和读出 128 个数据, 由于 FIFO 不需要地址, 所以只需要产生使能信号即可。

首先看写状态, 在 wr\_state=0 时, 拉高写使能, 并让 wr\_data 不断累加, 往 FIFO 里面写数据, 当 wr\_water\_level=127 的时候, 拉低写使能, 写数据置 0, 写状态跳转到 1, 注意此时还会再写入一个数据, 所以到此一个写入了 128 个数据。至于拉低写使能, 写数据置 0, 写状态跳转到 1 这些操作将在下一个时钟周期才会被采样生效。之后, 在 wr\_state=1 时, 不断等待 rd\_cnt, 该条件就是判断当读出 128 个数据的时候, wr\_state 跳转到 0 状态。

接下来看读状态, 在 rd\_state=0 的时候, 一旦可读的数据量超过 128 个(包括 128), 状态跳转到 rd\_state=1 下, 然后开始读出数据, 同时在 rd\_state=1 下用变量 rd\_cnt 对我们的读出数据也进行计数, rd\_cnt 从 0 开始计数, 当 rd\_cnt=127 的时候会再往 FIFO 读出一个数据, 所以此时就一共读出了 128 个数据, 下一个时钟周期 rd\_en 和 rd\_state 都将置 0。

具体波形大家可以看视频仿真, 或者自己尝试仿真, 根据波形来看代码。因为这里是时序逻辑, 所以如果是初学者, 纯看文字可能会对 rd\_cnt=127 这一时刻还会再读一个数据感到疑惑, 建议直接仿真, 或者观看视频讲解的仿真部分, 可以帮助快速理解。

可以总结出一句话就是时序逻辑的赋值总在下一个时钟周期才生效。所以在 rd\_cnt=127 时执行的操作要在下一个时钟周期才会被采样生效。所以当前时钟 rd\_en 还是为 1, 会再从 FIFO 读出一个数据。

仿真代码的讲解到此结束。

## 7. 基于紫光 FPGA 的键控 LED 流水灯

### 7.1. 实验简介

实验目的:

通过按键控制 8 个 LED 灯按顺序依次点亮和熄灭。

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP-MINI

### 7.2. 实验原理

通常的时, 分, 秒的计时进位大家应该不陌生;

1 小时=60 分钟=3600 秒, 当时针转动 1 小时, 秒针跳动 3600 次;

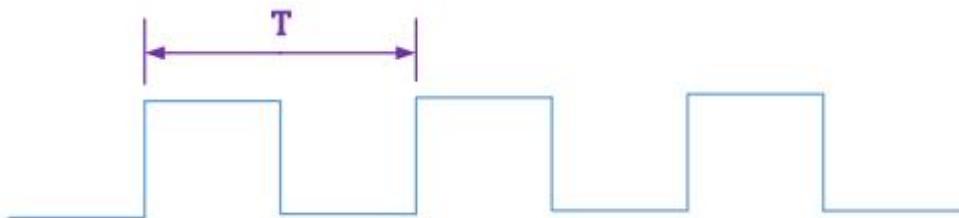

在数字电路中的时钟信号也是有固定的节奏的, 这种节奏的开始到结束的时间, 我们通常称之为周期 ( $T$ )。

图 7.2-1

在数字系统中通常关注到时钟的频率, 那频率与周期的关系如下:

$$f = 1/T$$

在 100K 板卡上单端时钟有一个 27MHz 的时钟。

所以其周期约为 37.037ns。而在我们 FPGA 的设计中, 我们的 always 块通常都是在时钟的上升沿时对数据进行赋值, 因此我们可以定义一个变量, 每到时钟的上升沿就让该变量+1, 让其变成一个计数器, 该变量每加 1 就表示经过了 37.037ns, 那如果要定时 1s 的话, 只需要让其计数到 26999999 即可, 因为从 0 开始计数, 所以计数到 26999999 即可, 此时就是一秒了。以此类推, 13499999 就是 0.5s。

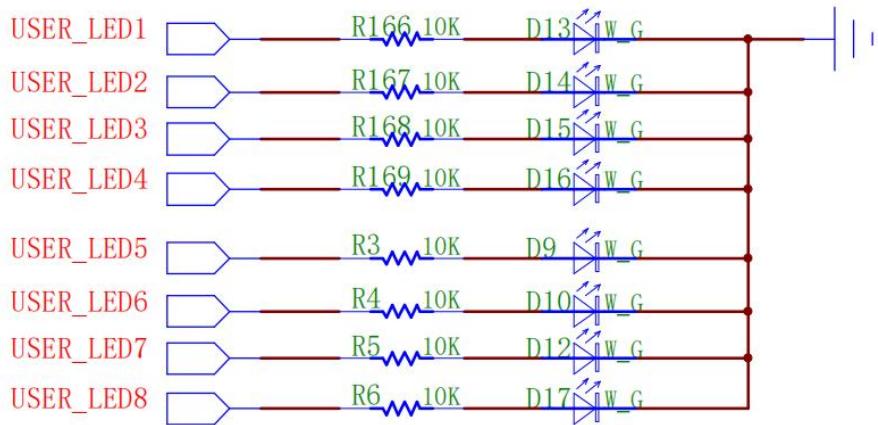

图 7.2-2

图 7.2-2 为开发板上 8 个 LED 灯的原理图。

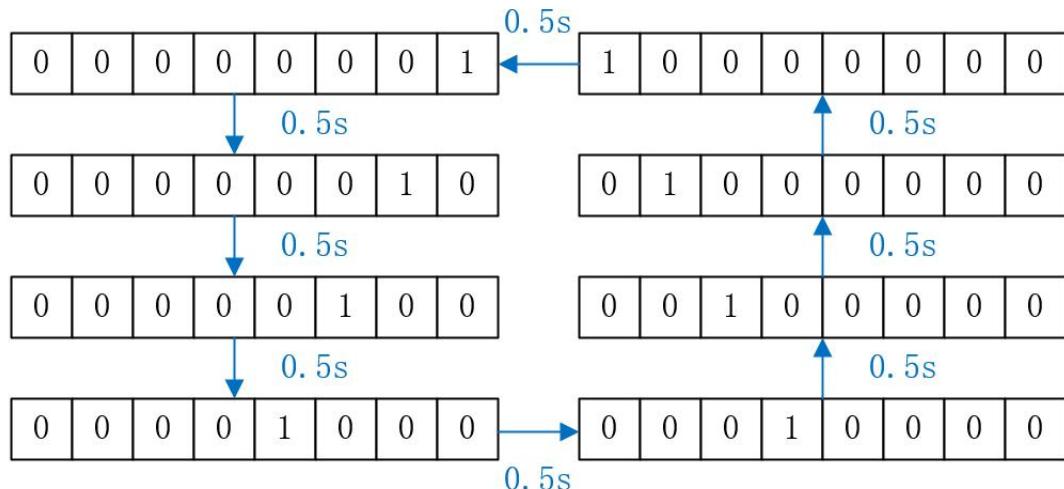

控制 0.5s 更换一次 LED 灯状态, 使 LED 灯呈现流水灯现象, 可以每 0.5s 依次点亮一个 LED 灯。(高电平用 1 表示, 低电平用 0 表示)

图 7.2-3

故只需要定义一个变量, 让其在时钟上升沿达到时就+1, 计数到 13500000-1 即可, 此时就是 0.5s。

### 7.3. 接口列表

| 端口             | I/O              | 位宽        | 描述                      |

|----------------|------------------|-----------|-------------------------|

| <b>CNT_MAX</b> | <b>Parameter</b> | <b>26</b> | <b>计数的最大值, 修改定时的时间。</b> |

| clk            | input            | 1         | 系统时钟, 27MHz             |

| key            | input            | 1         | 按键信号                    |

| rst_n          | input            | 1         | 复位信号, 低有效               |

| led[7:0]       | output           | 8         | led 灯控制信号               |

## 7.4. 工程说明

## 7.5. 代码模块说明

```

1. `timescale 1ns/1ns

2. `define UD #1

3. module key_led_test

4. #(

5.     parameter CNT_MAX = 26'd13_500_000

6. )

7. (

8.     input      clk      ,

9.     input      rstn     ,

10.    input      key      ,

11.

12.    output [7:0] led

13.

14. );

15.

16.

17.//=====

18.//reg and wire

19.

20.reg [25:0] led_light_cnt = 26'd0;

21.reg [7:0] led_status = 8'b0000_0001;

22.

23.//time counter

24.always@(posedge clk)

25.begin

26.    if(!rstn)

27.        led_light_cnt <= `UD 26'd0;

28.    else    if(led_light_cnt == CNT_MAX-1)

29.        led_light_cnt <= `UD 26'd0;

30.    else

31.        led_light_cnt <= `UD led_light_cnt + 26'd1;

32.end

33.

34.//led status change

35.always@(posedge clk)

```

```

36.begin

37.    if(!rstn)

38.        led_status <= `UD 8'b0000_0001;

39.    else    if(led_light_cnt == CNT_MAX-1 && key)

40.        led_status <= `UD {led_status[6:0],led_status[7]};

41.    else    if(led_light_cnt == CNT_MAX-1 && !key)

42.        led_status <= `UD {led_status[0],led_status[7:1]};

43.end

44.

45.assign led = led_status;

46.

47.

48.endmodule

```

代码的第 5 行所定义的参数 CNT\_MAX 是用来设定计数的最大值, 默认是 13500000, 也就是定时 0.5S, 可以通过修改该值来改变定时的时间。

代码的 24-32 行, 用变量 led\_light\_cnt 实现了定时器的功能, 每到时钟的上升沿就让其加 1, 不断计数。由于从 0 开始计数, 所以计数到 CNT\_MAX-1 即把它清 0。

代码的 35-43 行, 实现了 LED 灯的状态控制, led\_status 是个 8bit 的变量, 当 key 没按下时, 也就是 key 的值为 1 时, 且 Led\_light\_cnt=CNT\_MAX-1 时, 就让 led\_status 向左移 1 位。实现 LED0->LED7。当按键按下时, key 为 0, 实现 LED7->LED0。

代码 45 行, 就通过组合逻辑, 将 led\_status 的值赋值给 led。

## 7.6. 代码仿真

```

1.  `timescale  1ns/1ns

2.  module tb_key_led_test();

3.

4.  reg          clk          ;

5.  reg          rst_n        ;

6.  wire [7:0]   led          ;

7.  reg          key          ;

8.

9.  reg [7:0]   data          ;

10.

11. initial

12. begin

13.     rst_n    <=  0;

14.     clk      <=  0;

15.     key     <=  0;

16.     #20

```

```

17.      rst_n    <=    1;

18.      key     <=    1;

19.      #2000

20.      key     <=    0;

21.      #2000

22.      $display("I am stop");

23.      $stop;

24. end

25.

26. always#10 clk = ~clk;//20ns 50MHZ

27.

28. key_led_test#(

29.     .CNT_MAX (10 )

30. )u_key_led_test(

31.     .clk    ( clk    ),

32.     .rstn   ( rst_n  ),

33.     .key    ( key    ),

34.     .led    ( led    )

35. );

36.

37. initial

38. begin

39.     $monitor("led:%b",led);

40. end

41.

42.

43. always@(posedge clk or negedge rst_n) begin

44.     if(!rst_n)

45.         data    <=    8'd0;

46.     else

47.         begin

48.             data    <=    {$random}%256;

49.             $display("Now data is %d",data);

50.         end

51.     end

52.

53. endmodule

```

该 testbench 部分代码是用于测试一些仿真函数使用,在前面的 Modelsim 的使用章节已经做了介绍,所以本次只关注代码的 28-35 行, 例化了我们的流水灯模块。可以看到代码的 29 行, CNT\_MAX 传入的参数给的是

10, 这是为了减少仿真时间, 如果还是 13500000 的话, 我们需要仿真 0.5s 才能看到结果, 这非常的久。

代码的 11-26 行依旧是对复位和时钟赋初值, 延时 20ns 后, 复位结束。时钟依然是每隔 10ns 取反一次, 来生成 50MHz 的时钟。

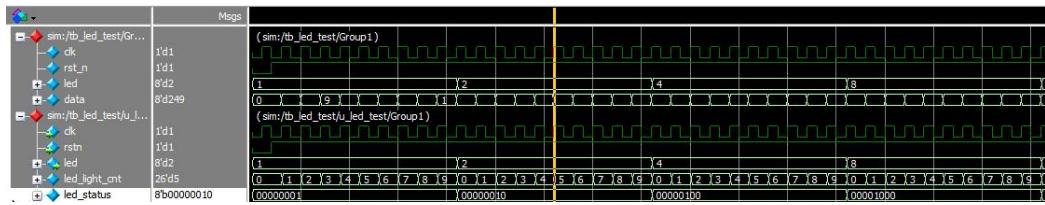

图 7.6-1

图 7.6-1 为仿真结果, 可以看到 led\_light\_cnt 每次计数 10 个数据后, led\_status 会向左移一位, 符合实验结果。

## 7.7. 实验步骤

这里将会详细介绍从新建工程到下载程序的具体步骤, 后续的工程将不再详细解释。

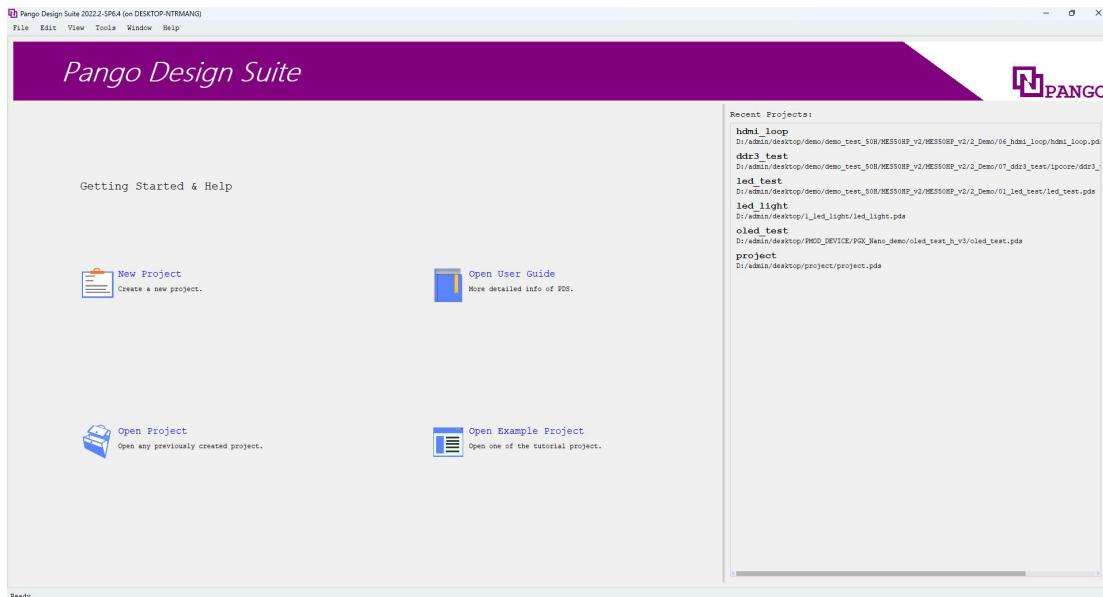

### 7.7.1. 打开 PDS 软件, 创建工程

Step1: 打开 PDS 软件, 点击 NEW Project, 然后对其设置完成新建工程;

图 7.7-1

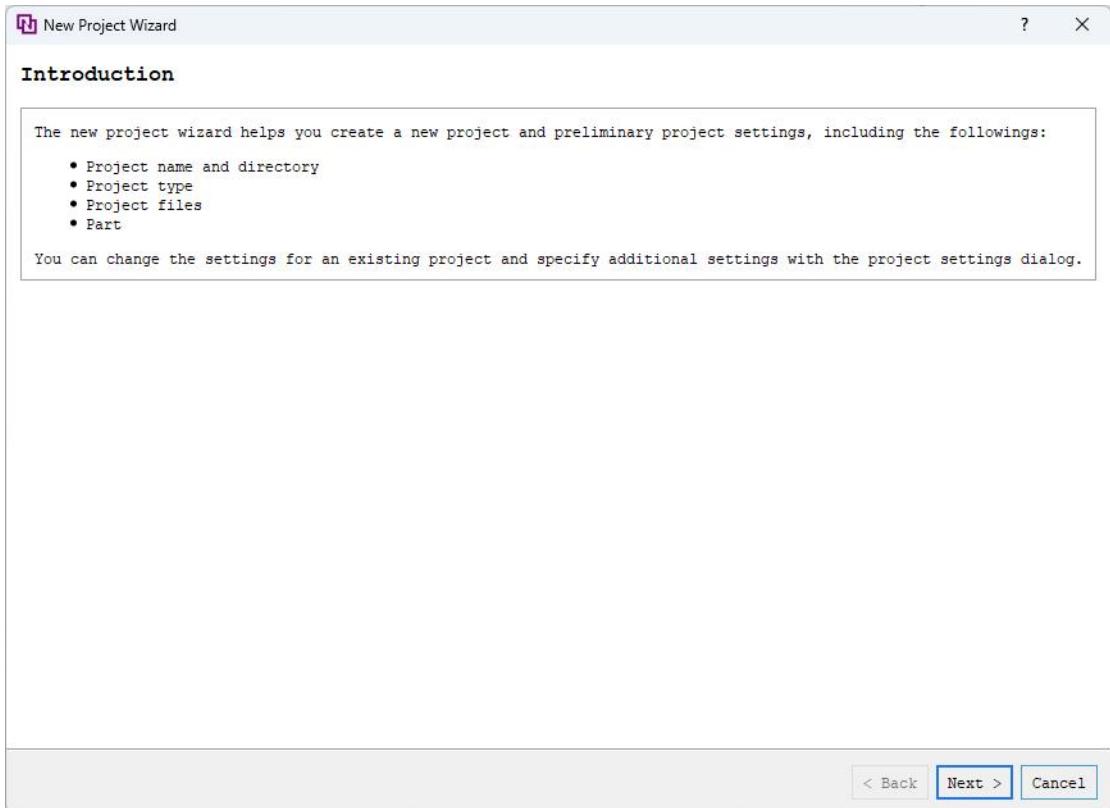

Step2: 单击 NEXT;

图 7.7-2

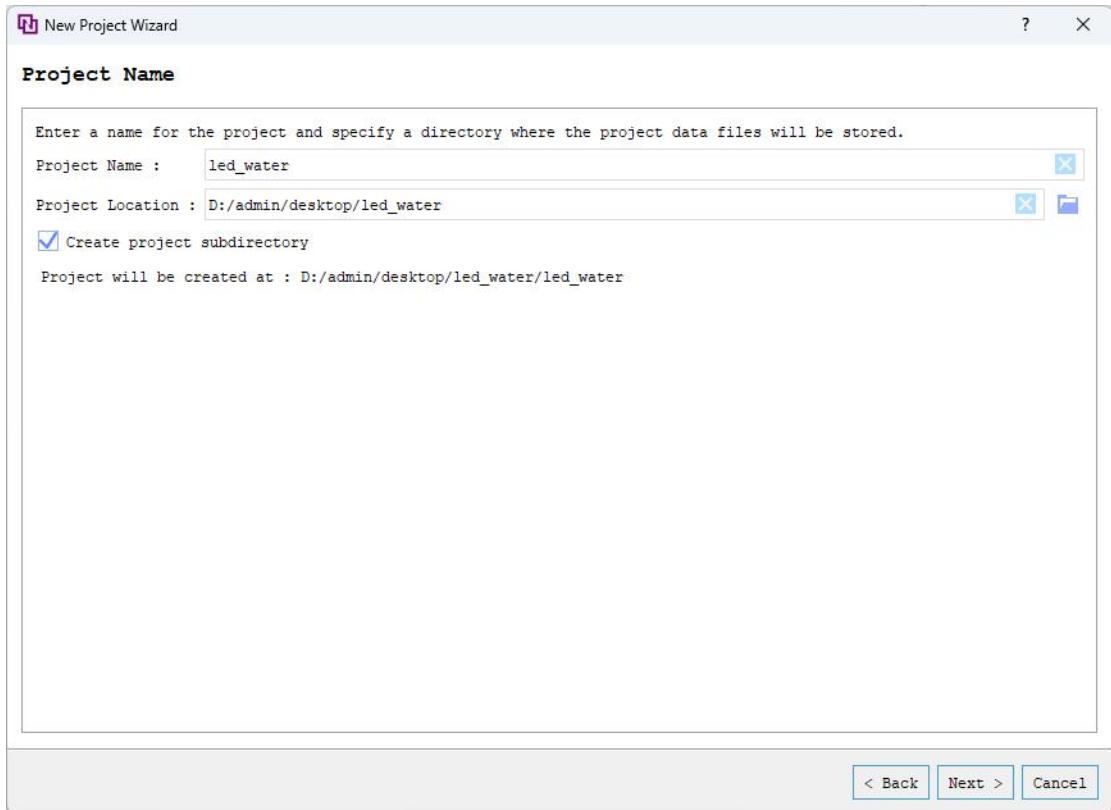

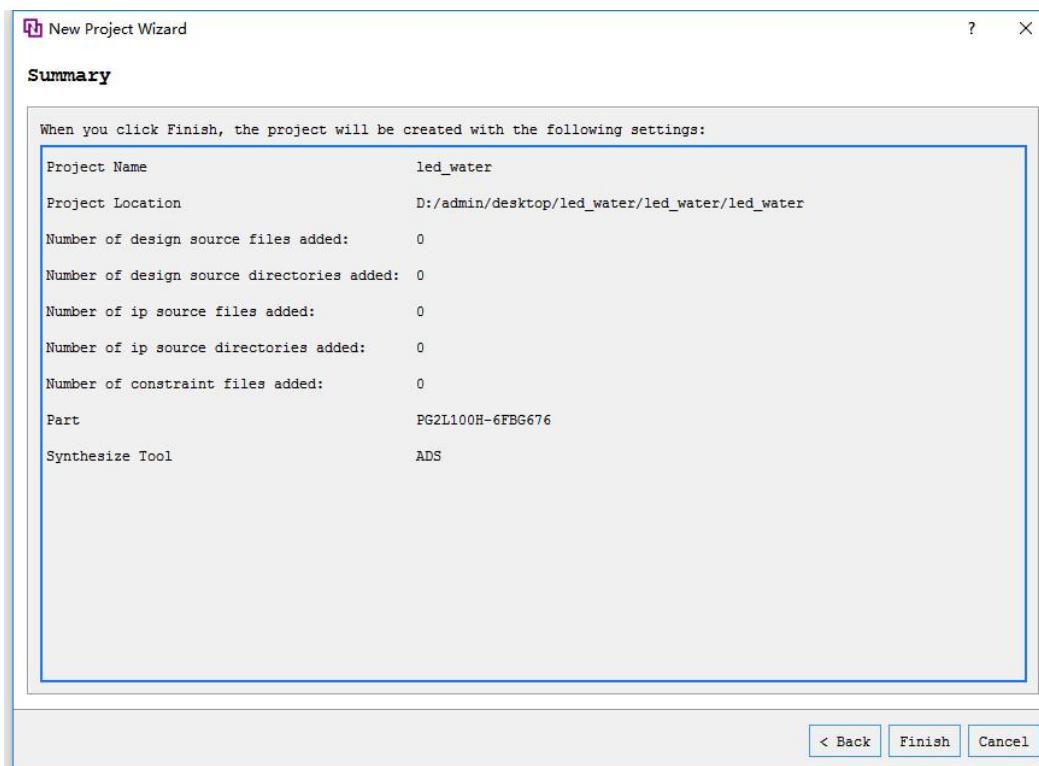

Step3: 创建名为 led\_water 的工程到对应的文件目录, 之后单击 Next;

新建工程大致包括设置工程名和工程路径、工程类型、工程文件及器件信息。

【Project Name】是工程文件名称, 默认为 project。(只允许字母、数字、下划线(\_)、杠(-)、点(.))。

【Project Location】用于选择新工程的工作路径, 文件夹名只允许字母、数字、下划线(\_)、杠(-)、点(.)、@、~、,、+、=、#、空格( ), 但空格不能出现在路径名首尾, 即工程文件放置的路径。

【Create Project Subdirectory】将工程文件名作为工作目录的一部分。

图 7.7-3

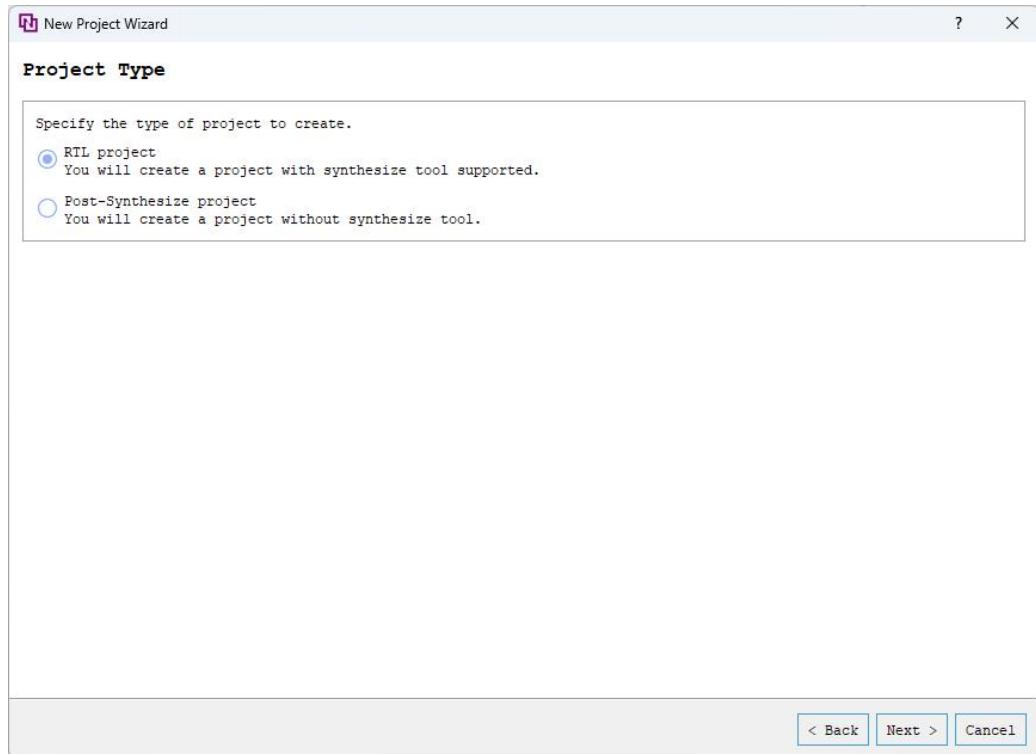

Step4: 选择 RTL project, 点击 Next;

【RTL Project】用于创建 RTL 工程。新建的工程可以执行 synthesize, device map, place& route, report timing, report power, generate netlist 及 generate bitstream 等。

【Post-Synthesize Project】用于创建综合后工程。新建的工程可以执行 device map, place& route, report timing, report power, generate netlist 及 generate bitstream 等。

图 7.7-4

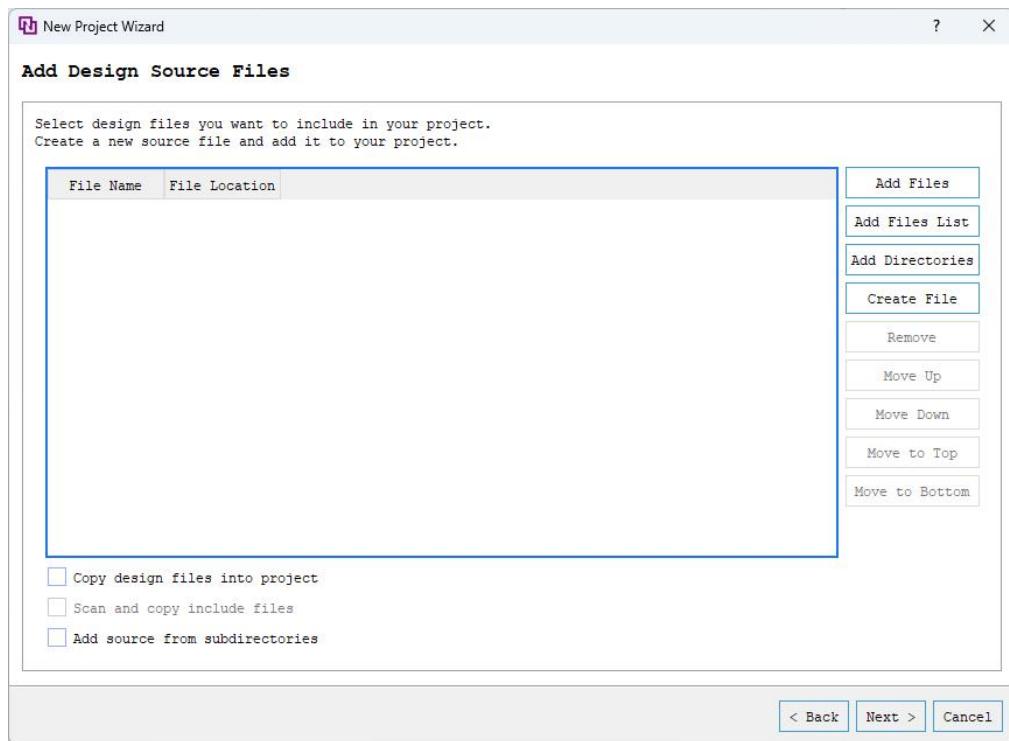

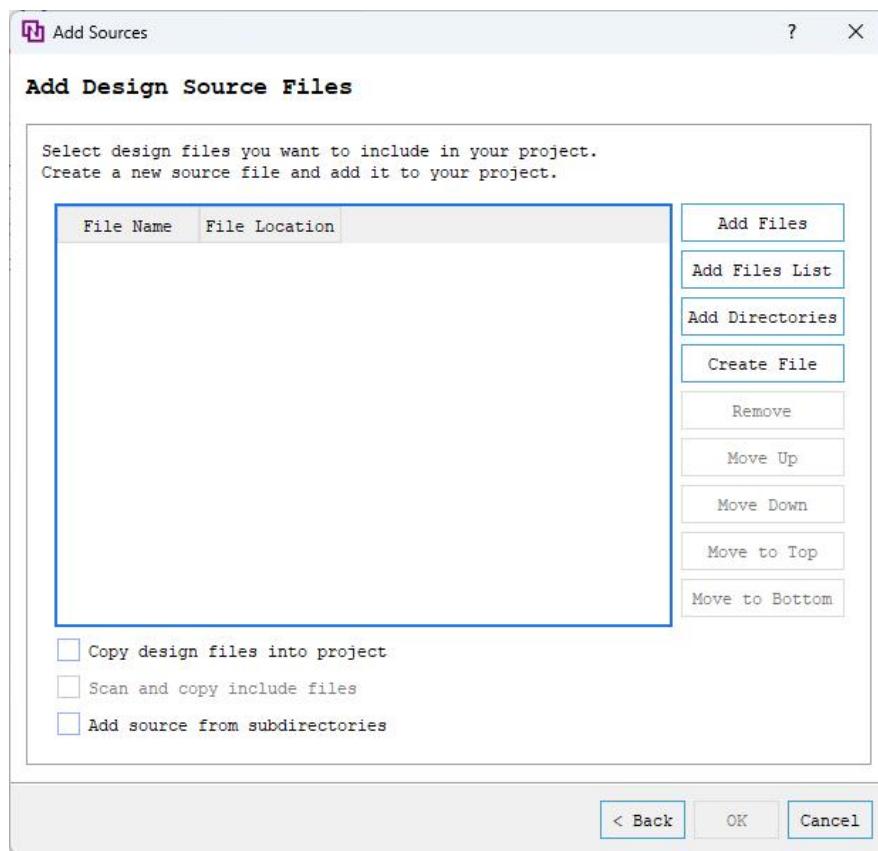

Step5: 单击 Next;

该界面可以 Add Files 和 Add Directories 来添加 rtl 源文件及新建 rtl 源文件, 以及调整 rtl 文件编译顺序, Add Files 添加选中的文件, Add Directories 添加选中的文件夹下所有合适的文件, 若勾选了下方的 Add source from subdirecotires 则添加所有的子目录下合适的文件, 也可直接 NEXT 跳过添加文件。

图 7.7-5

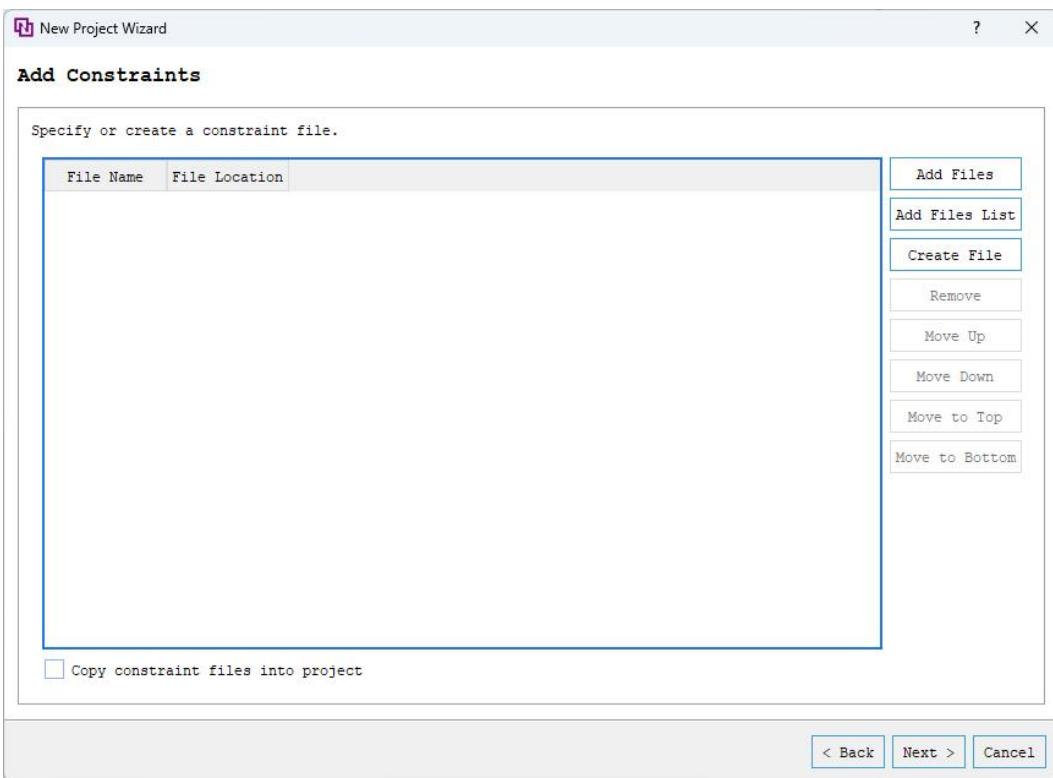

Step6: 单击 Next;

图 7.7-6

Step7: 单击 Next;

图 7.7-7

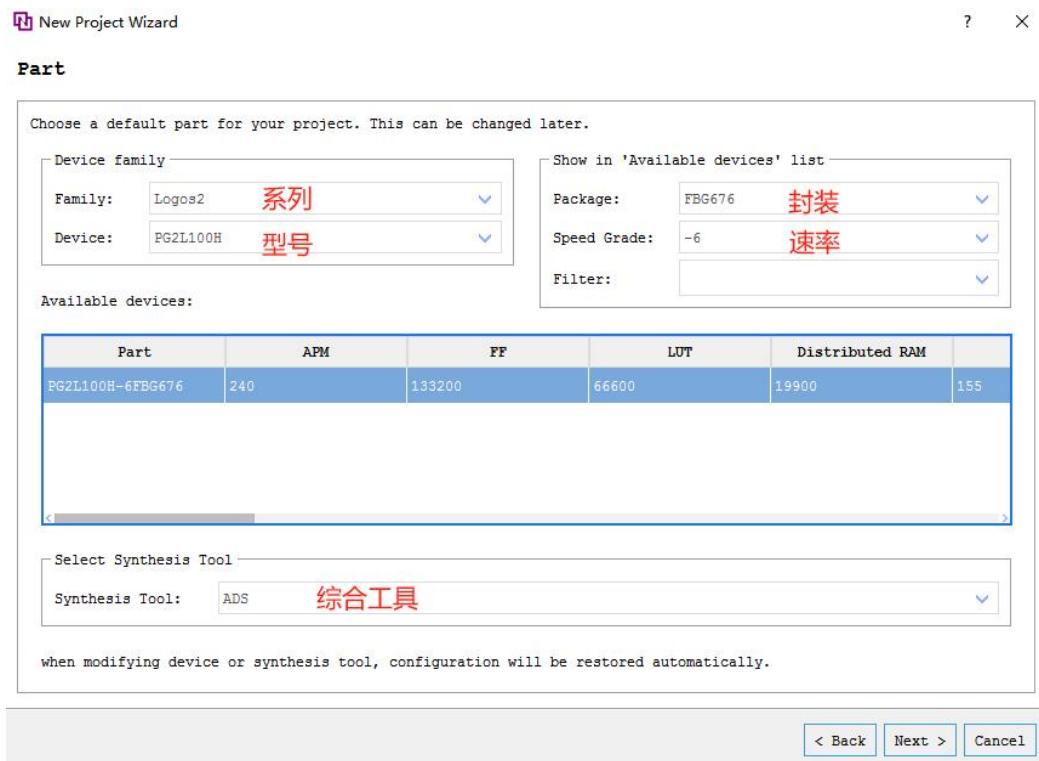

Step8: 选择器件系列、型号、封装、速率、综合工具, 之后单击 Next;

synthesize tool 中可以选择综合工具为 Synplify Pro 或 ADS, 在实验中使用 ADS 综合工具。

图 7.7-8

Step9: 在 summary 单击 Finish, 完成工程的创建;

图 7.7-9

### 7.7.2.添加设计文件

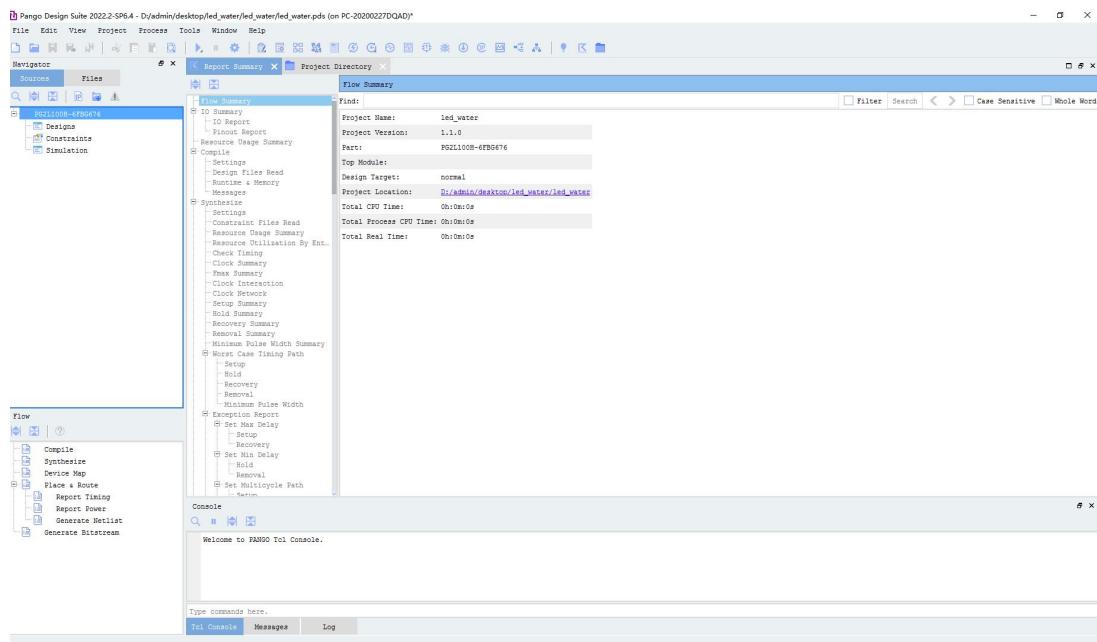

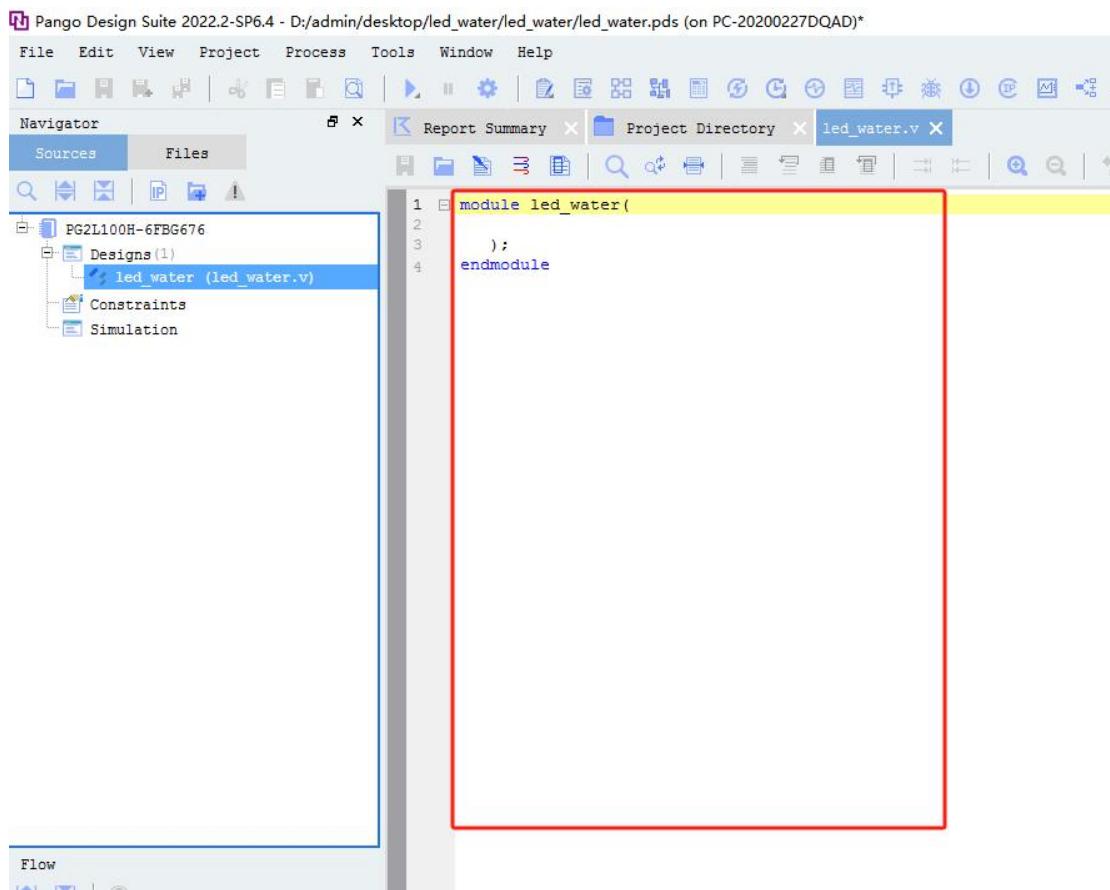

PDS 软件界面如下图:

图 7.7-10

双击 Designs, 将前面设计的 module 新建到文件中, 或者将前面编辑好的 verilog 文件添加到工程中;

图 7.7-11

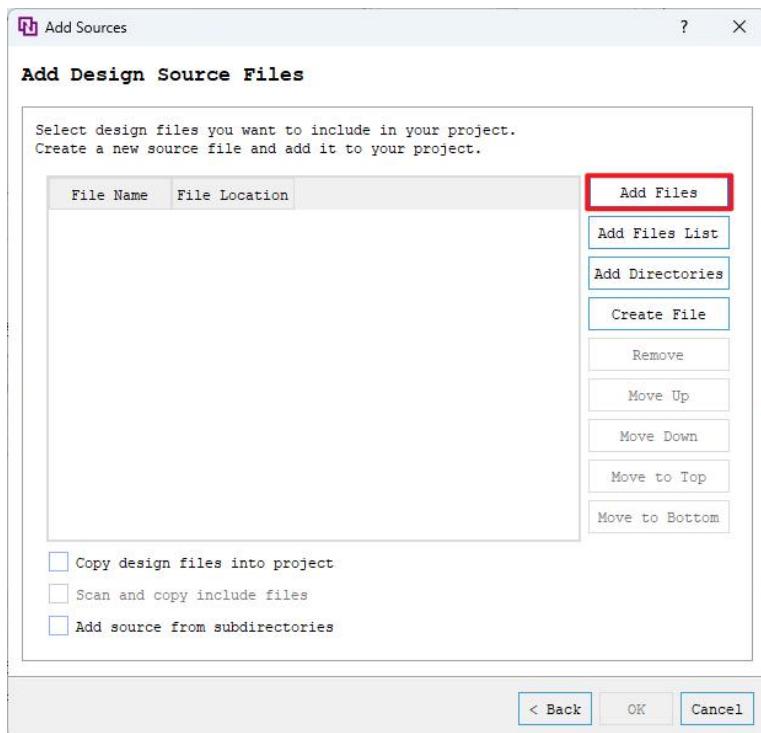

添加文件到工程:

在窗口中点击 Add Files, 选择添加文件到工程;

图 7.7-12

新建文件到工程:

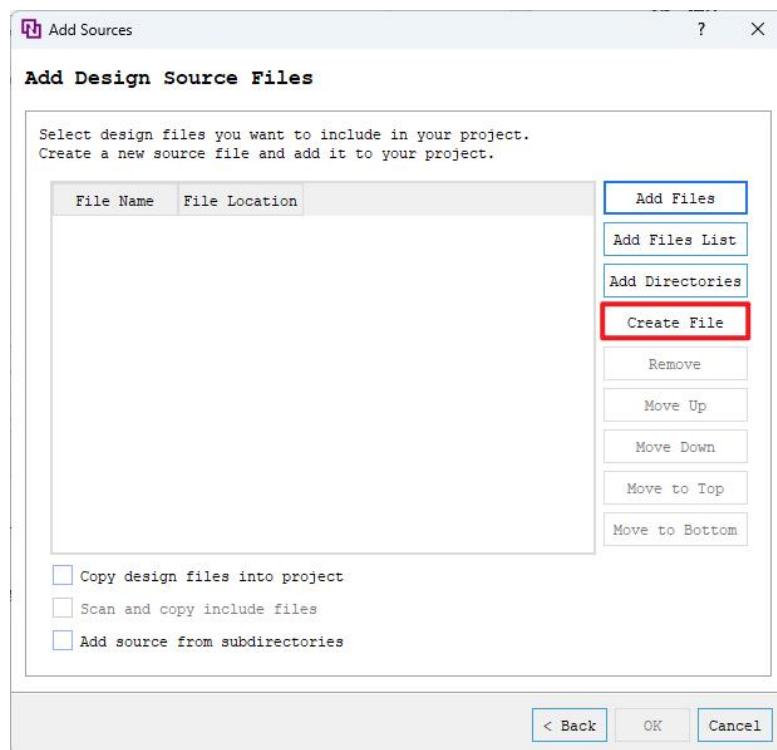

1) 在窗口中点击 Create File;

图 7.7-13

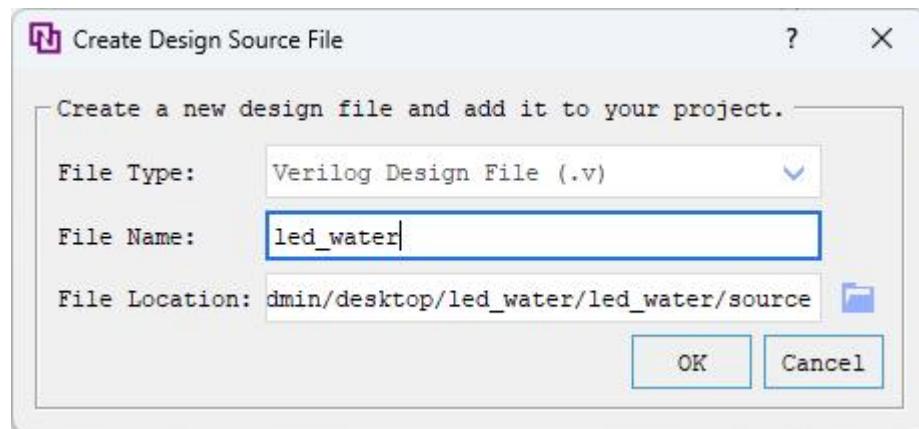

2) 选择 Verilog Design File, 文件名和 module 名一致, 默认路径, 点击 OK;

图 7.7-14

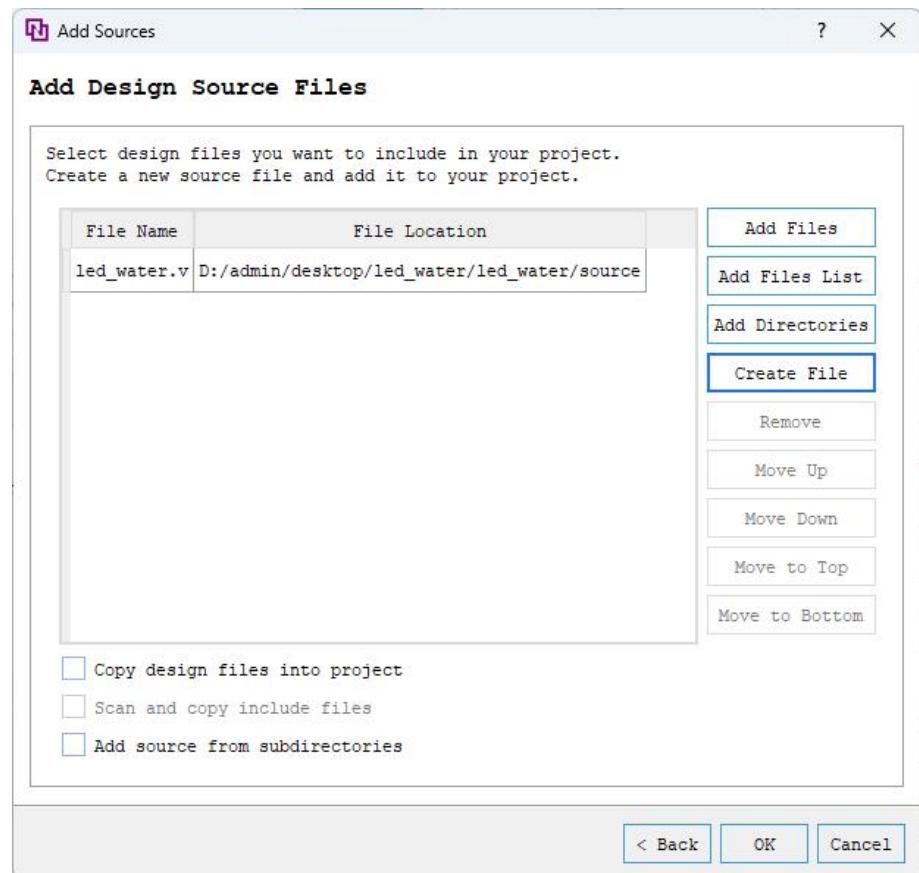

点击 OK;

图 7.7-15

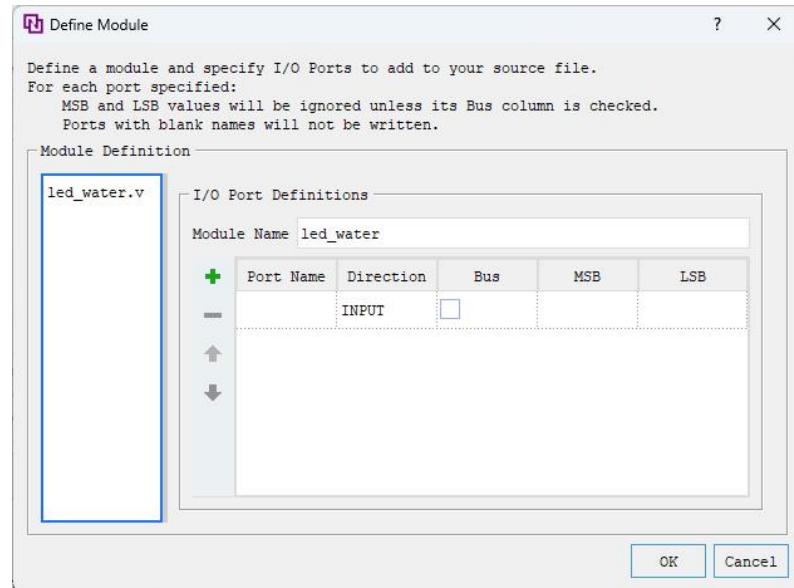

4) 点击 Cancel;

图 7.7-16

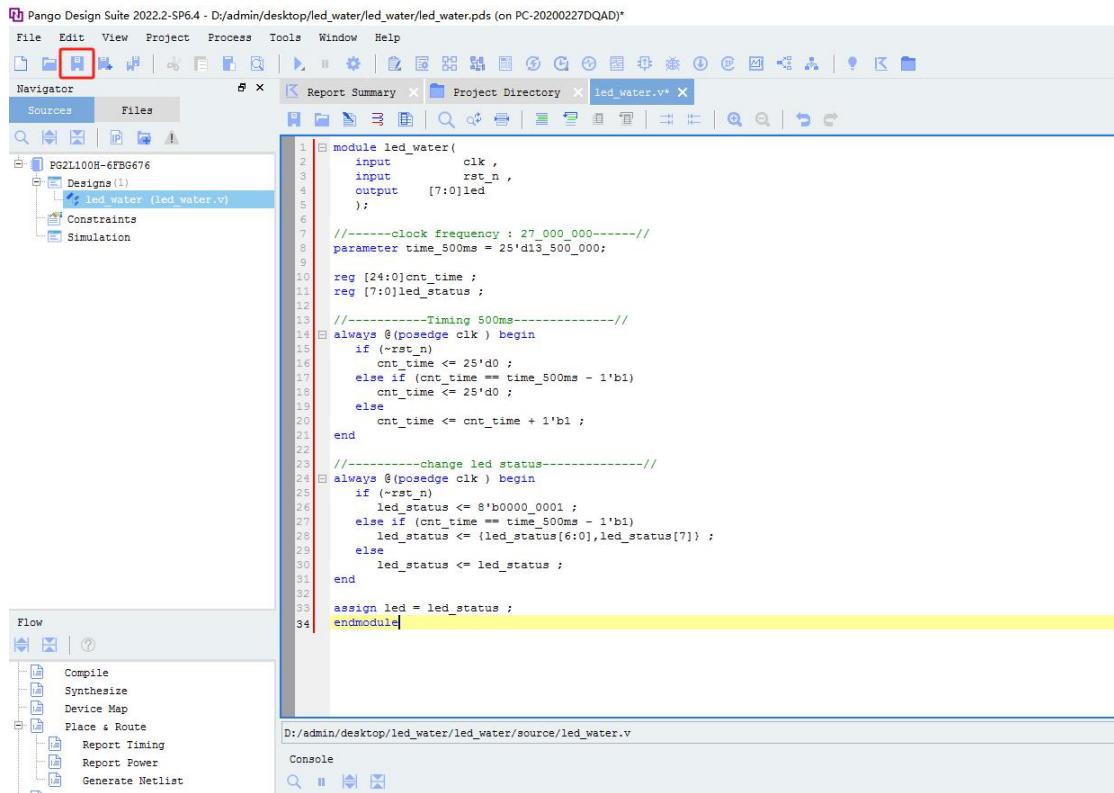

5) 默认打开新建文件, 将前面设计的 module 复制进去;

图 7.7-17

点击保存, 新建文件完成。

图 7.7-18

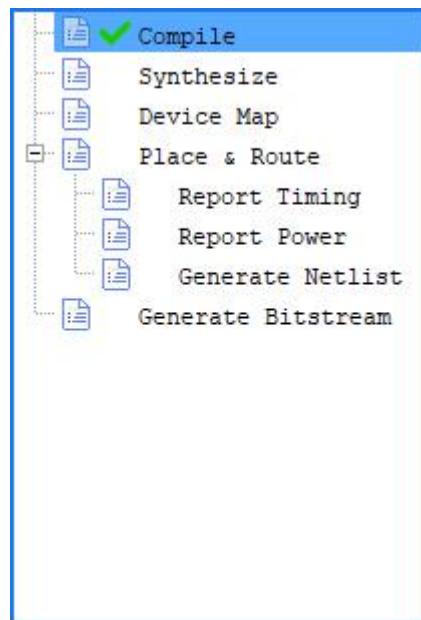

### 7.7.3. 编译

可采用以下方式运行 Compile 流程：

- (1) 双击 Flow 中的 Compile 进行综合；

- (2) 右击 Compile 点击 Run 进行综合；

图 7.7-19

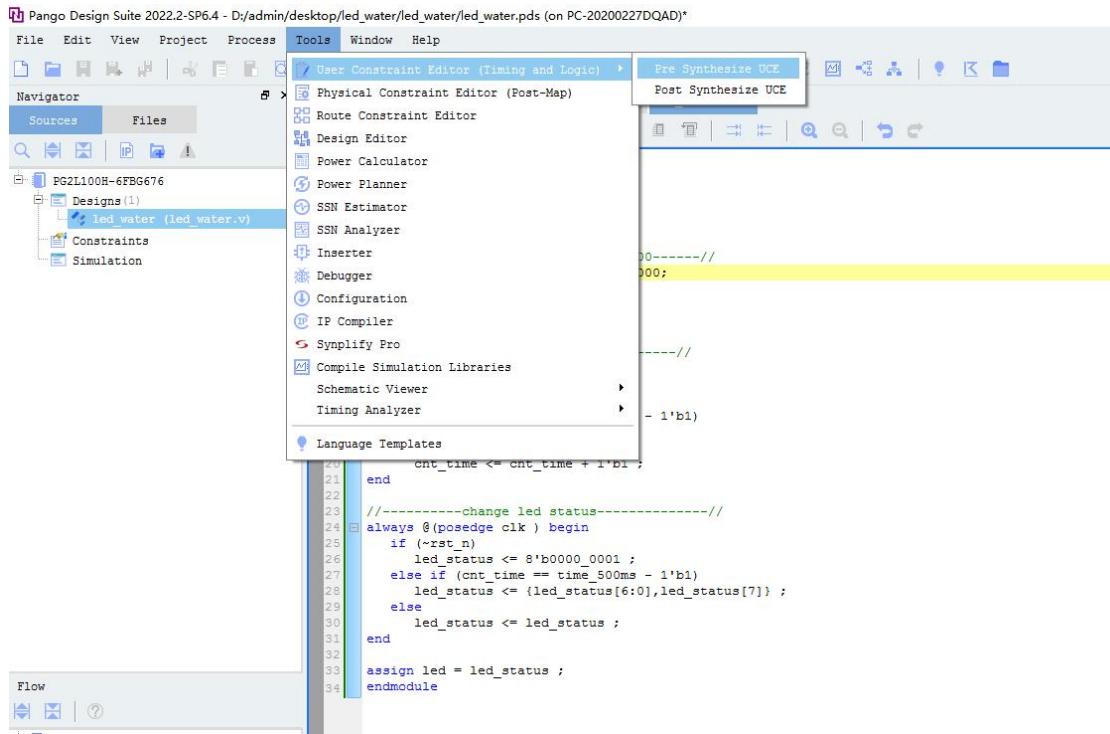

### 7.7.4. 工程约束

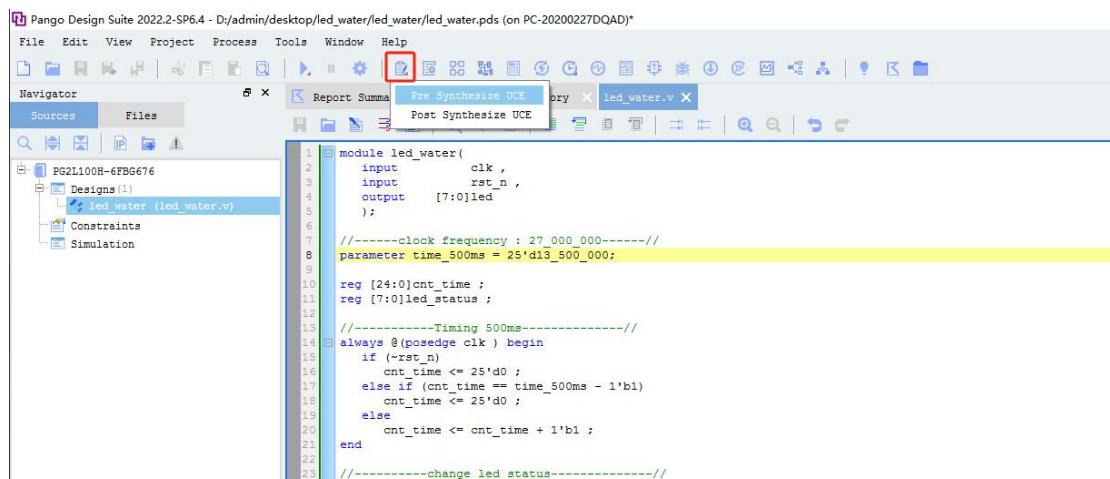

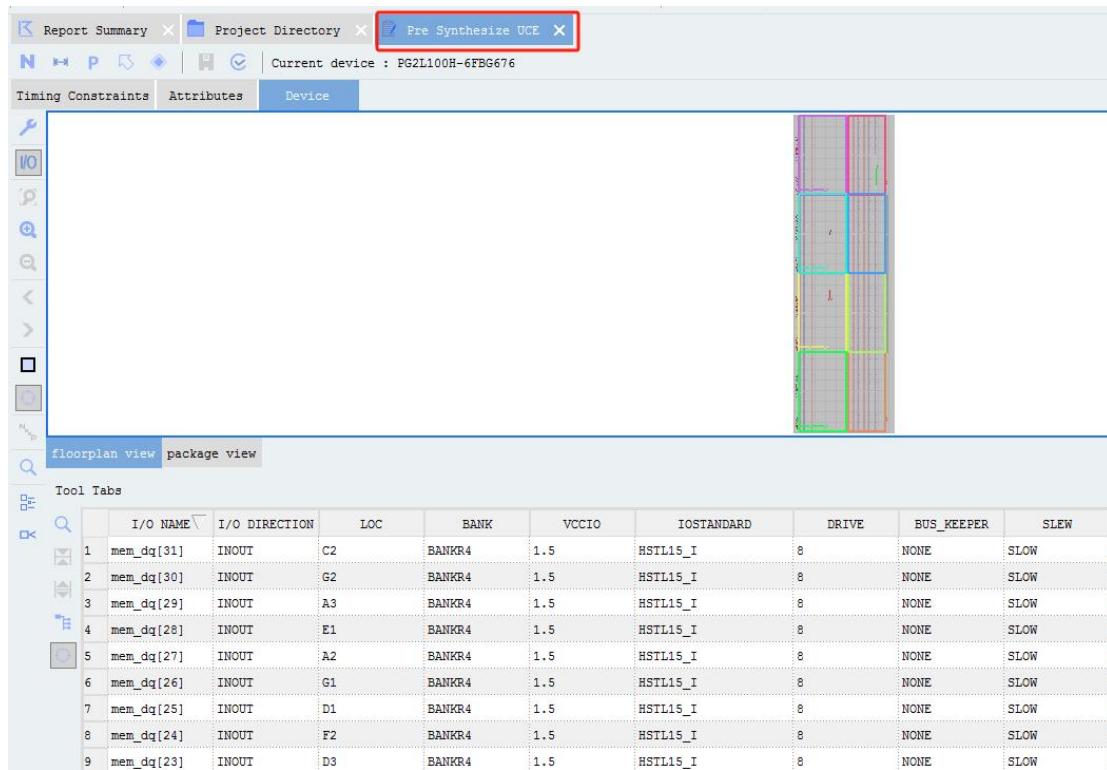

点击 Tools 选择 User Constraint Editor(Timing and Logic)或者点击工具栏图标，User Constraint Editor(Timing and Logic) 选择 Pre Synthesize UCE, 如下图所示：

图 7.7-20

Tools 下的 User Constraint Editor(Timing and Logic)。

图 7.7-21

工具栏 User Constraint Editor(Timing and Logic)图标。

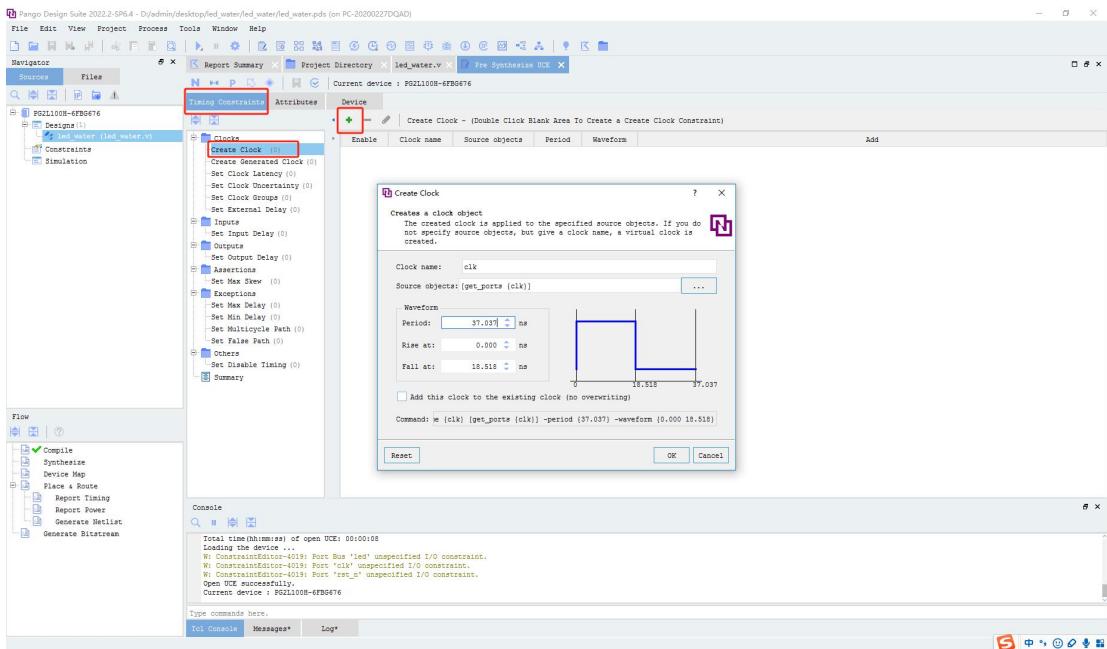

#### 7.7.4.1. 时钟约束

打开 UCE 后, 选择 Timing Constraints 后选择 Create Clock 添加基准时钟, 基准时钟一般是通过输入

port 输入用户所使用的板上时钟。

图 7.7-22

在弹窗中对时钟命名, 关联时钟管脚, 添加时钟参数, 点击 OK 会创建一条时钟约束, Reset 重置该页面。创建完成如下图所示:

图 7.7-23

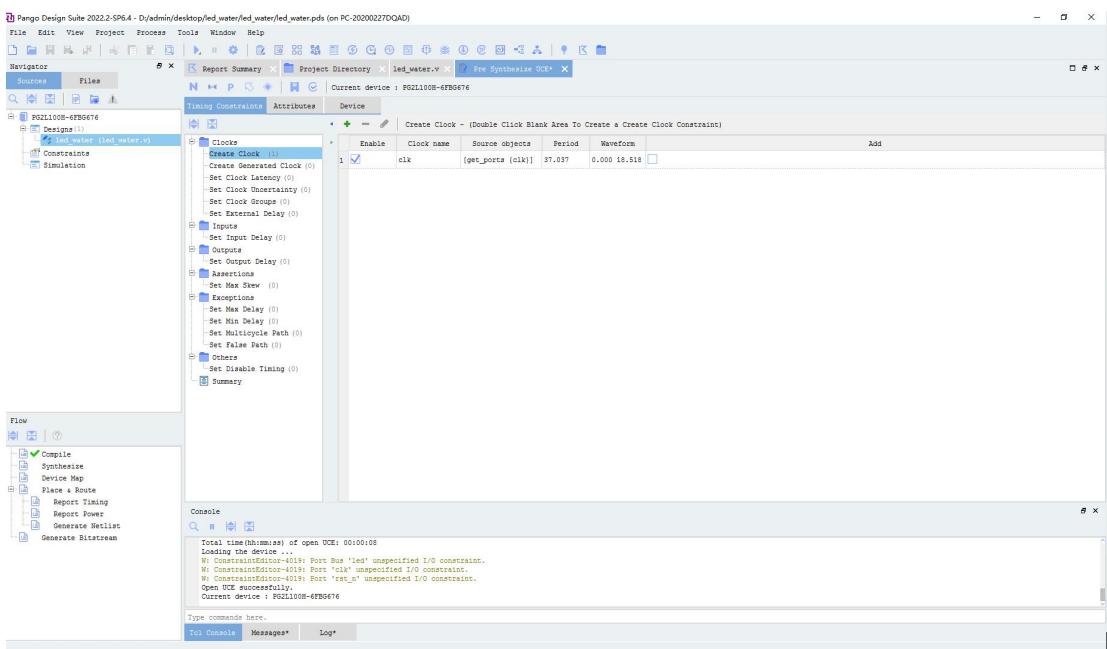

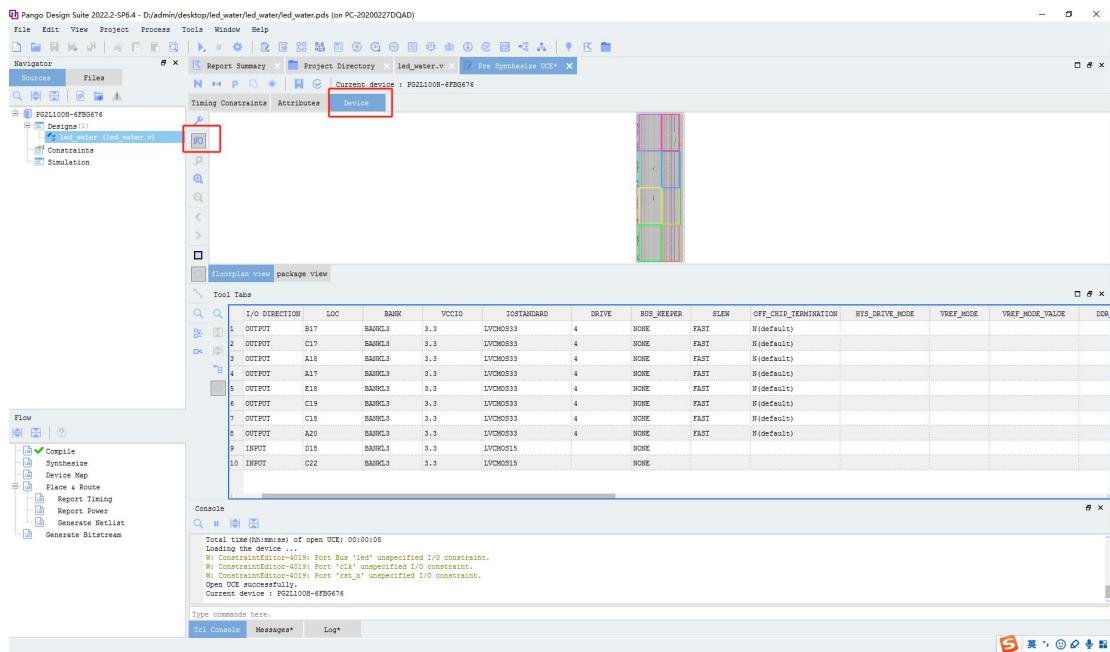

#### 7.7.4.2. 物理约束

打开 UCE 后, 选择 Device 后选择 I/O, 根据原理图编辑 IO 的分配。

图 7.7-24

按照原理图编辑好 IO 分配后，点击保存，会生成.fdc 文件，完成约束。

### 7.7.5.综合

运行 Synthesize 流程有以下四种方式可以实现：

(1) 双击 Flow 中的 Synthesize 进行综合；

(2) 右击 Synthesize 点击 Run 进行综合；

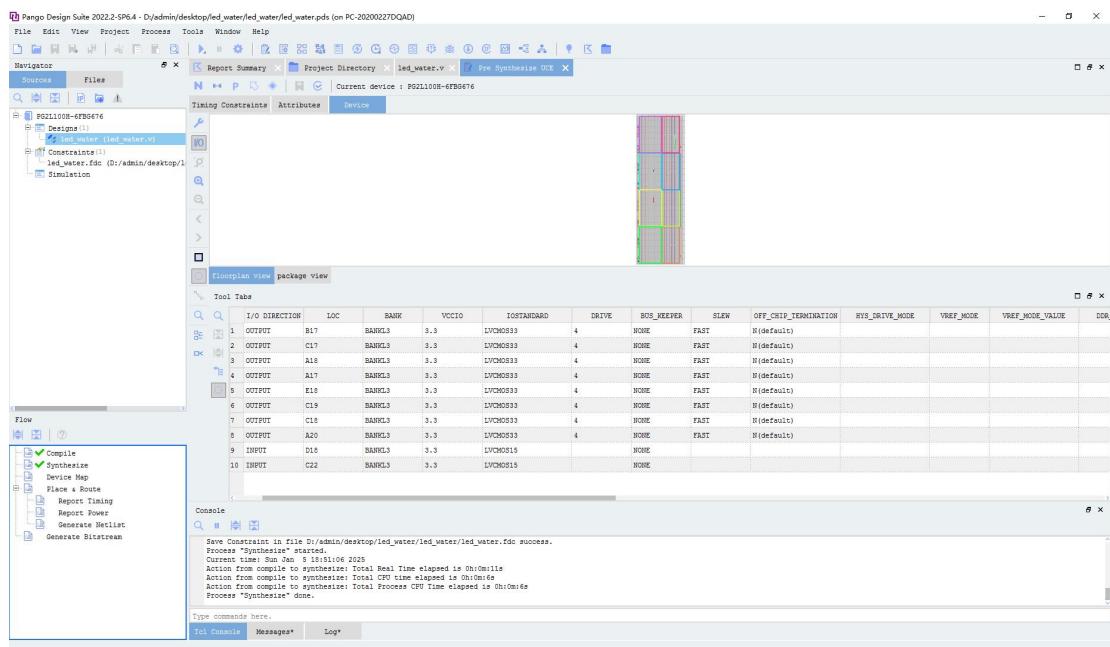

完成 Synthesize 操作后，会看到下图所示：

图 7.7-25

### 7.7.6.Device Map

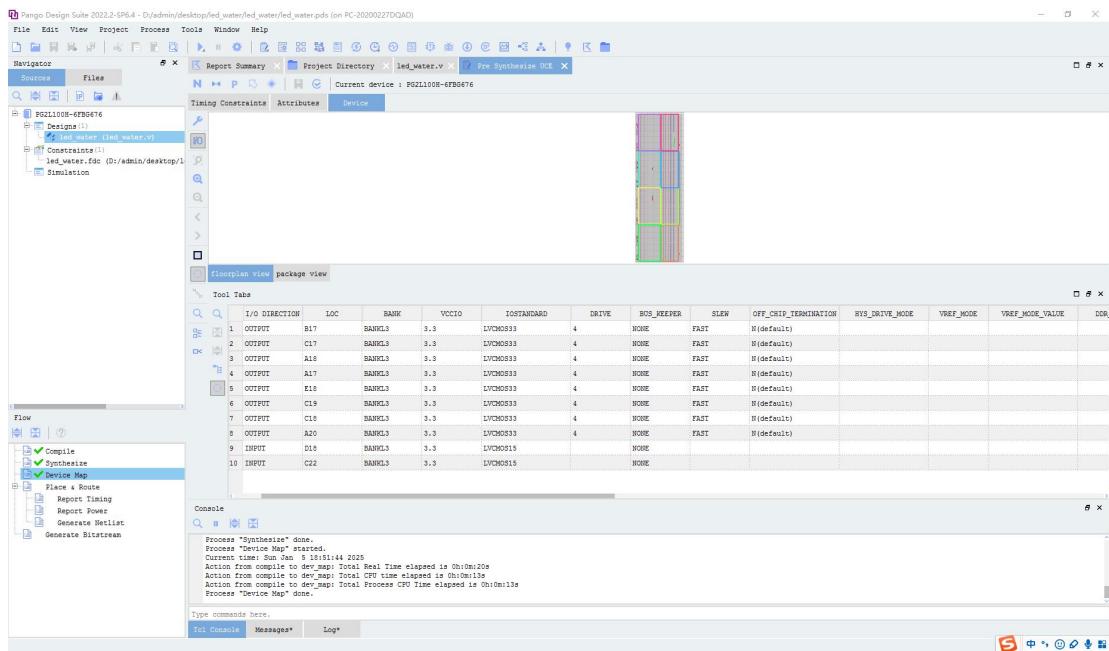

Device Map 的主要作用是将设计映射到具体型号的子单元上 (LUT、FF、Carry 等)。运行 Device Map 流程有以下方式可以实现:

- (1)直接双击 Device Map;

- (2)右击 Device Map 点击 Run;

完成 Device Map 操作后, 会看到下图所示:

图 7.7-26

### 7.7.7.Place & Route

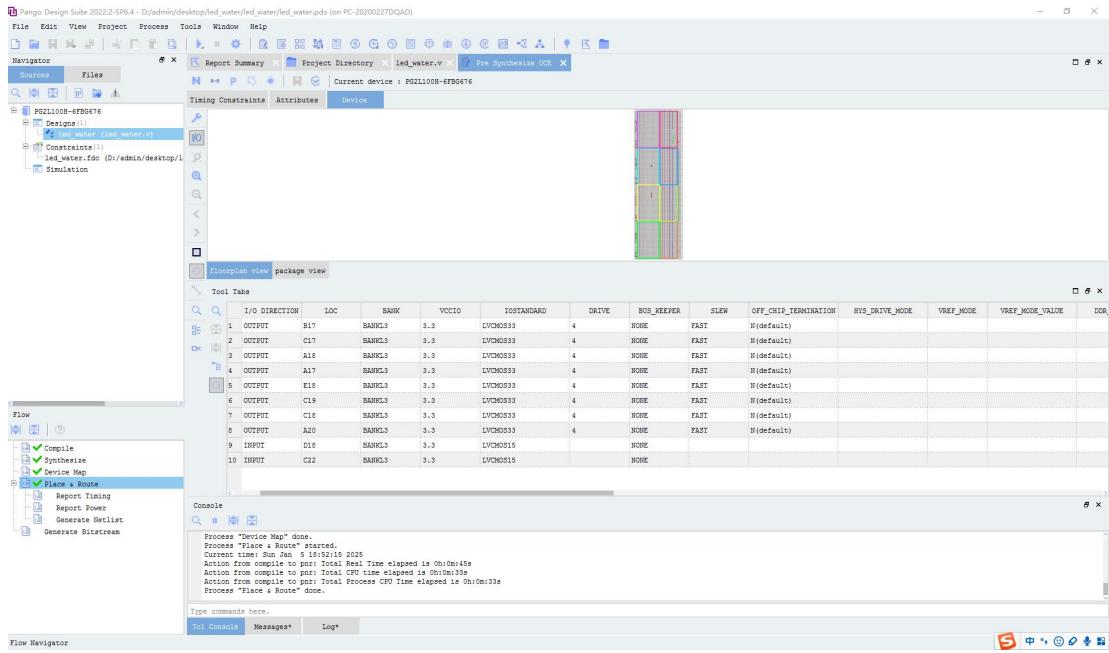

布局布线 (Place & Route)根据用户约束和物理约束, 对设计模块进行实际的布局及布线。

运行 Place & Route 流程有以下方式可以实现:

- (1)直接双击 Place & Route;

- (2)右击 Place & Route 点击 Run;

- 完成 Device Map 操作后, 会看到下图所示:

图 7.7-27

### 7.7.8. Generate Bitstream

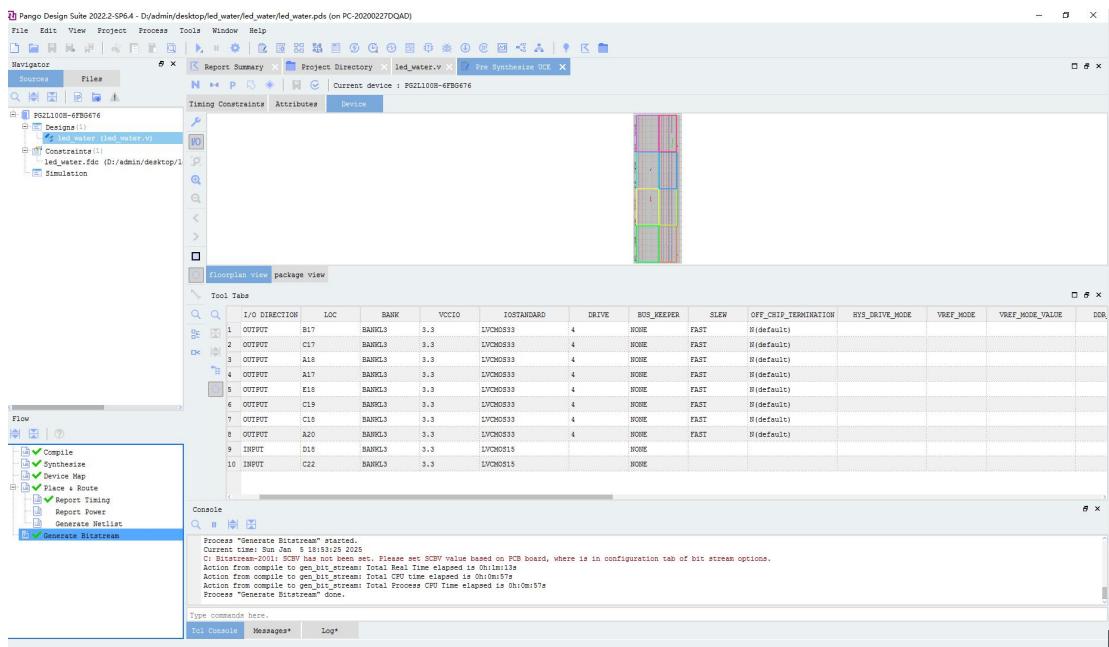

Generate Bitstream 生成二进制位流文件。运行 Generate Bitstream 流程有以下方式可以实现：

- (1) 直接双击 Generate Bitstream；

- (2) 右击 Generate Bitstream 点击 Run；

完成以上操作，将会产生位流文件。运行 Generate Bitstream，可以看到界面如下图所示：

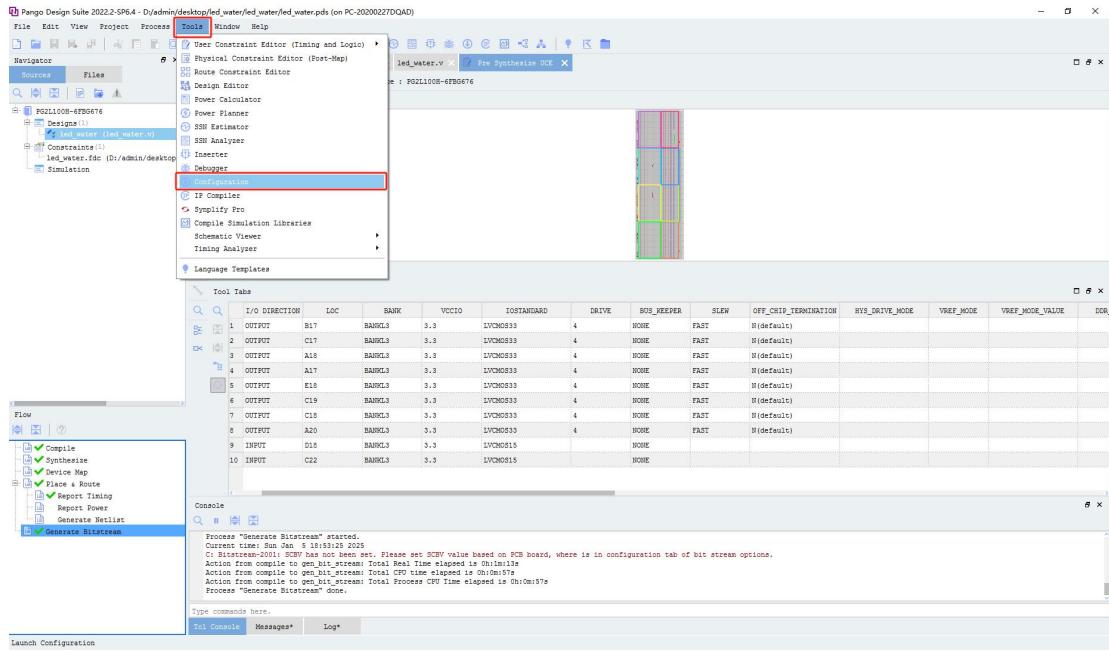

图 7.7-28

### 7.7.9. 下载生成的位流文件

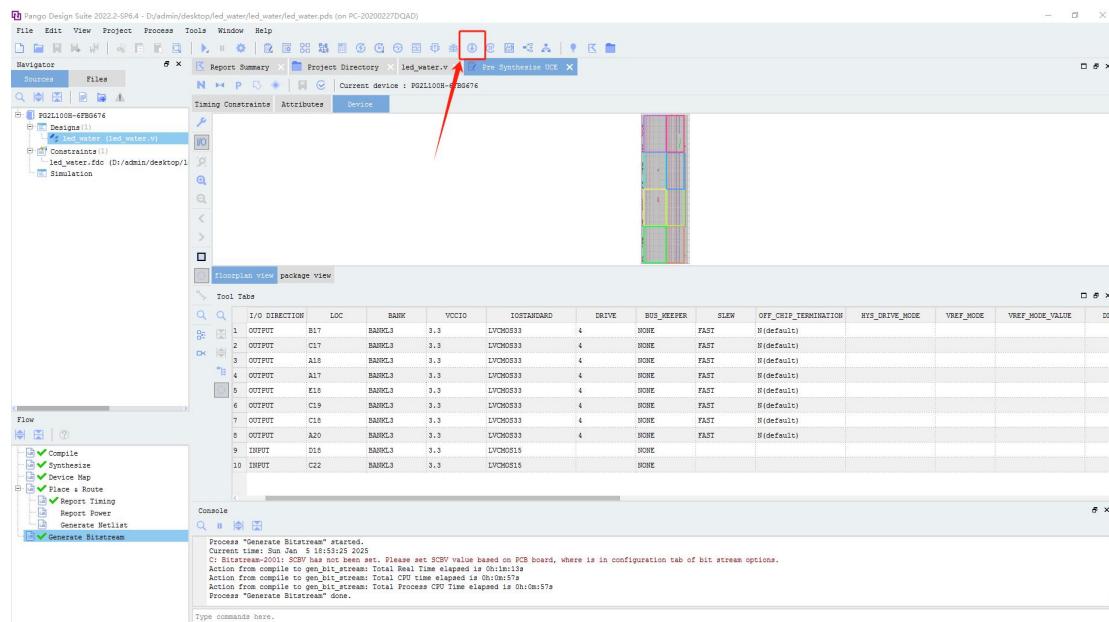

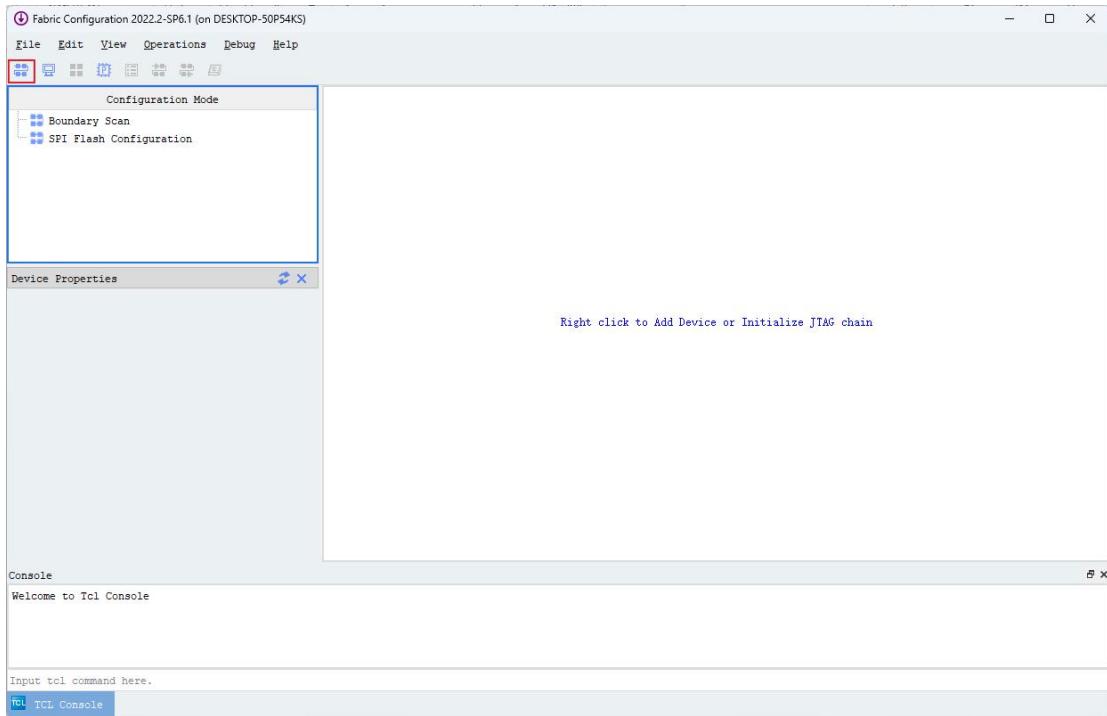

点击 Tools 选择 Configuration 或者点击工具栏图标 Configuration, 如下图所示：

图 7.7-29

上图为 Tools 下的 Configuration 选项。

图 7.7-30

上图为工具栏 Configuration 图标。

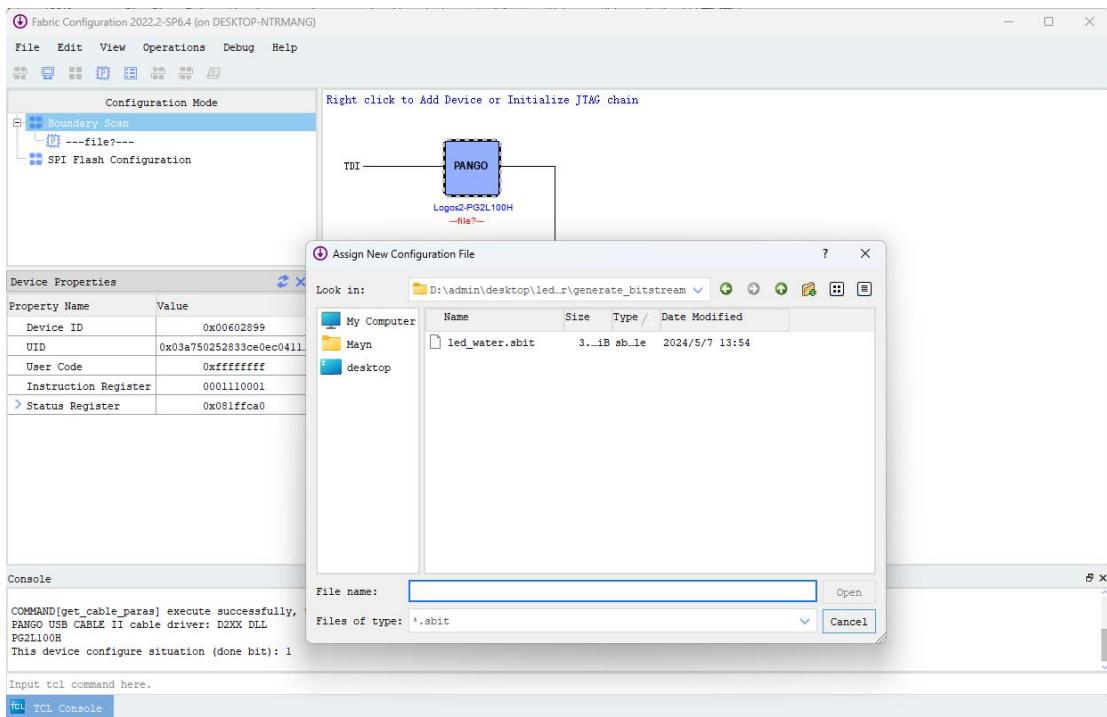

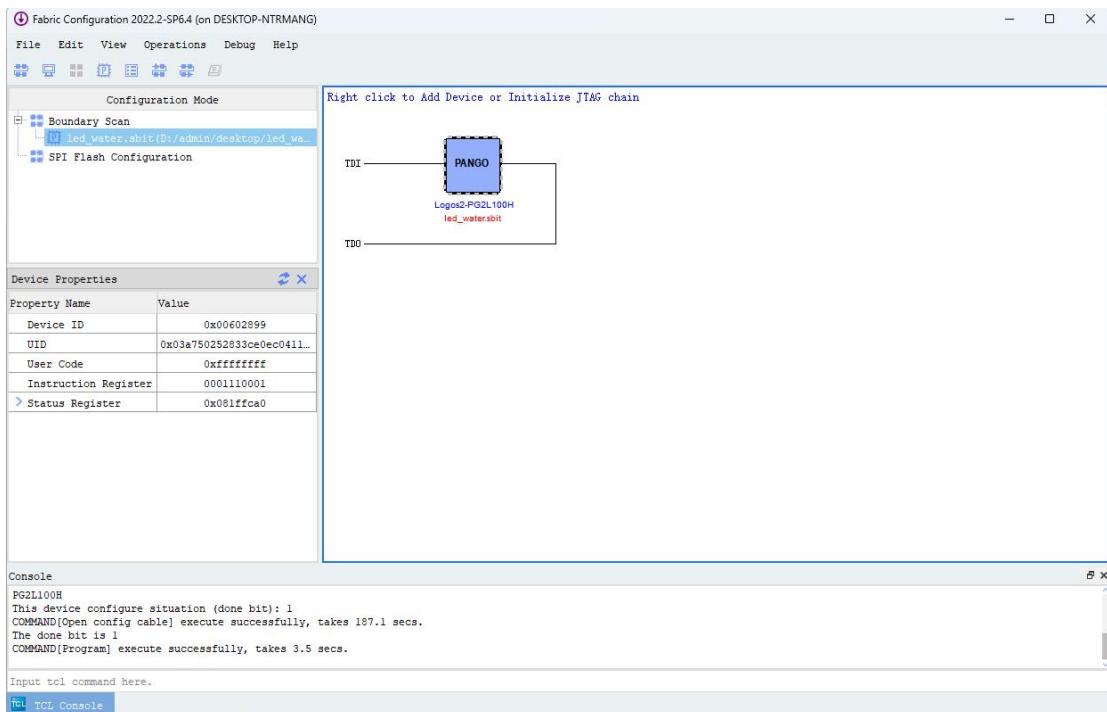

打开 Configuration 后直接选择 Scan Device 直接进行扫描 Jtag 链操作, 初始化链成功, 会将链上扫描到的所有器件显示于工作区内, 并在器件属性窗口显示当前器件的器件信息, 并弹出对话显示能够为器件添加的配置文件;

图 7.7-31

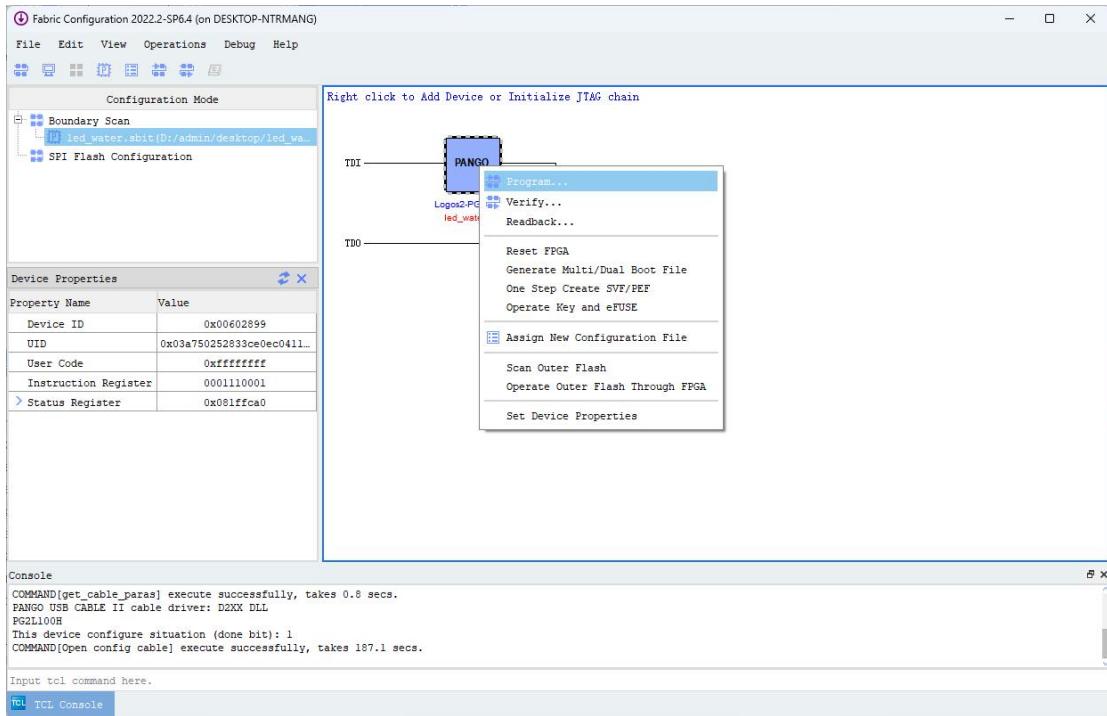

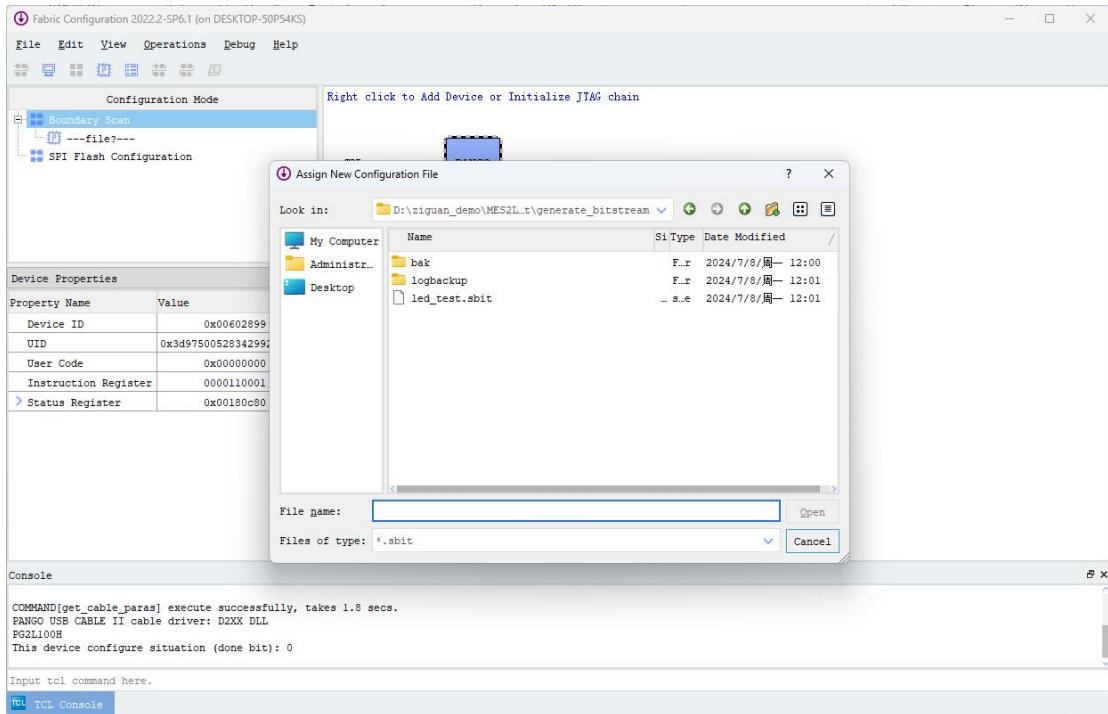

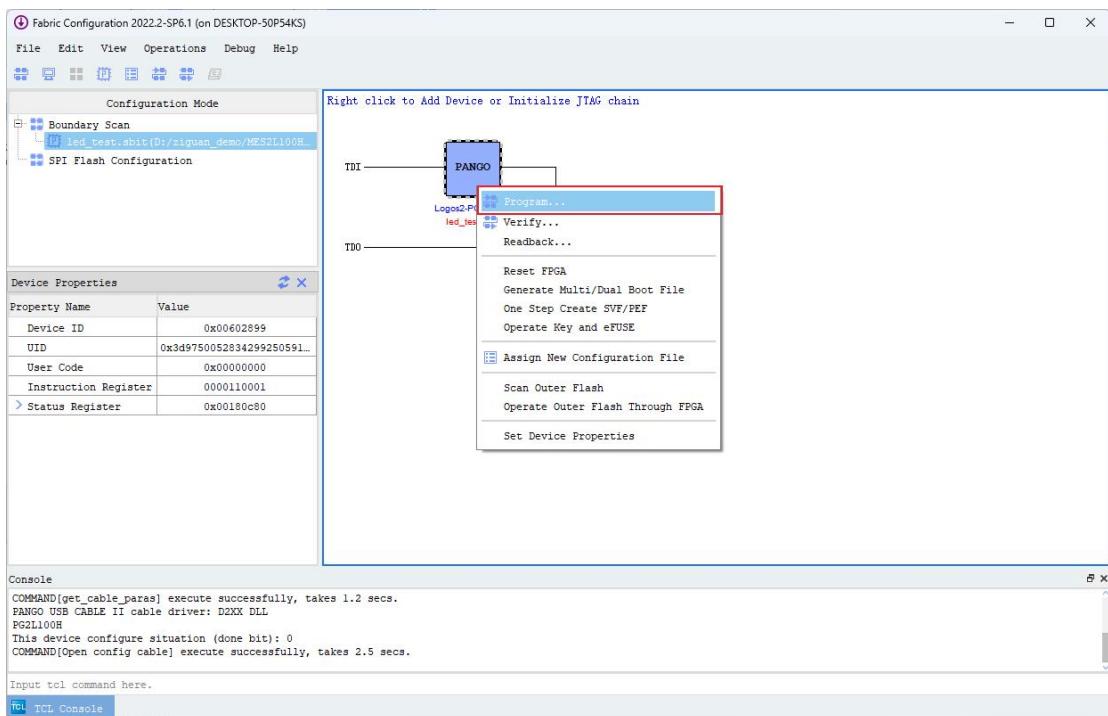

在对话框中选择位流文件, 添加该配置文件, 提示所载入文件的绝对路径并在信息栏中显示, 右键后点击 program 下载位流文件如下图所示:

图 7.7-32

下载位流文件成功如下图所示:

图 7.7-33

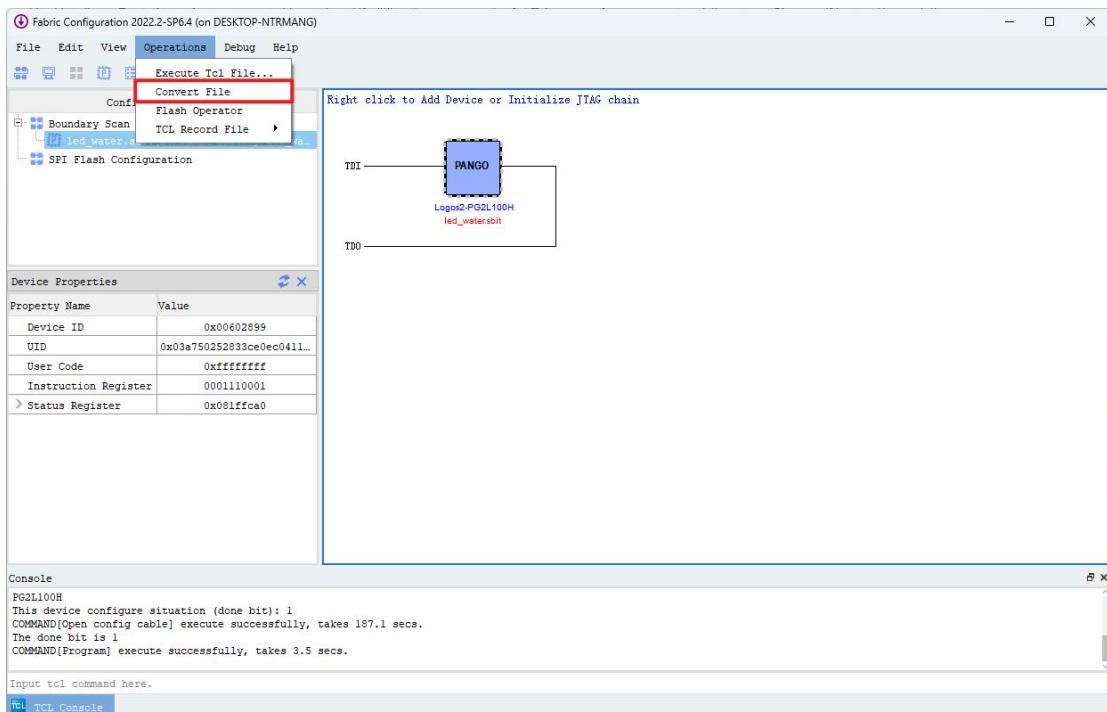

PG2L100H 板卡为 PG2L100H 的 FPGA 配置了一个外部 flash, 其中, 若需要将程序固化到板卡上需要将尾流文件转化为.sfc 文件。

首先点击 Configuration 页面的 Operations 选项的 Convert File 选项;

图 7.7-34

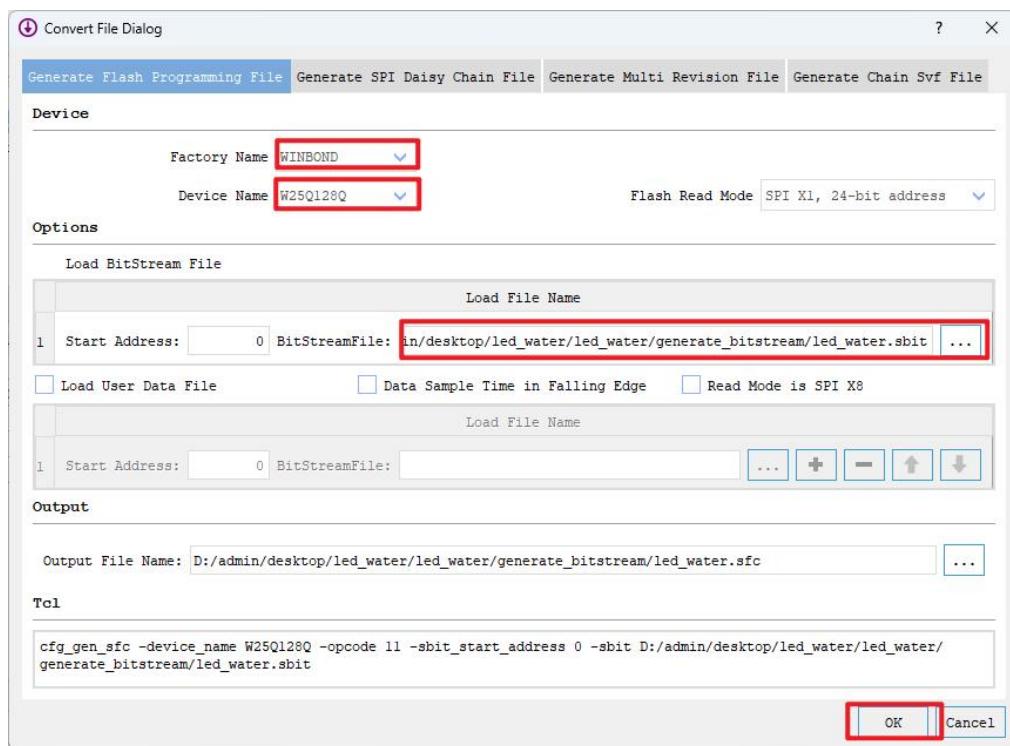

点击后会出现如下画面, 在 Generate Flash Programming File 页面选择对应的 Flash 器件的厂商名、型号、再在 BitStreamFile 位置选择位流文件的路径, 点击 OK。(若使用的 flash 器件不在可选的 flash 列表中, 需手

动添加对应 flash 型号, 操作步骤请参考开发板下载与固化相说明);

图 7.7-35

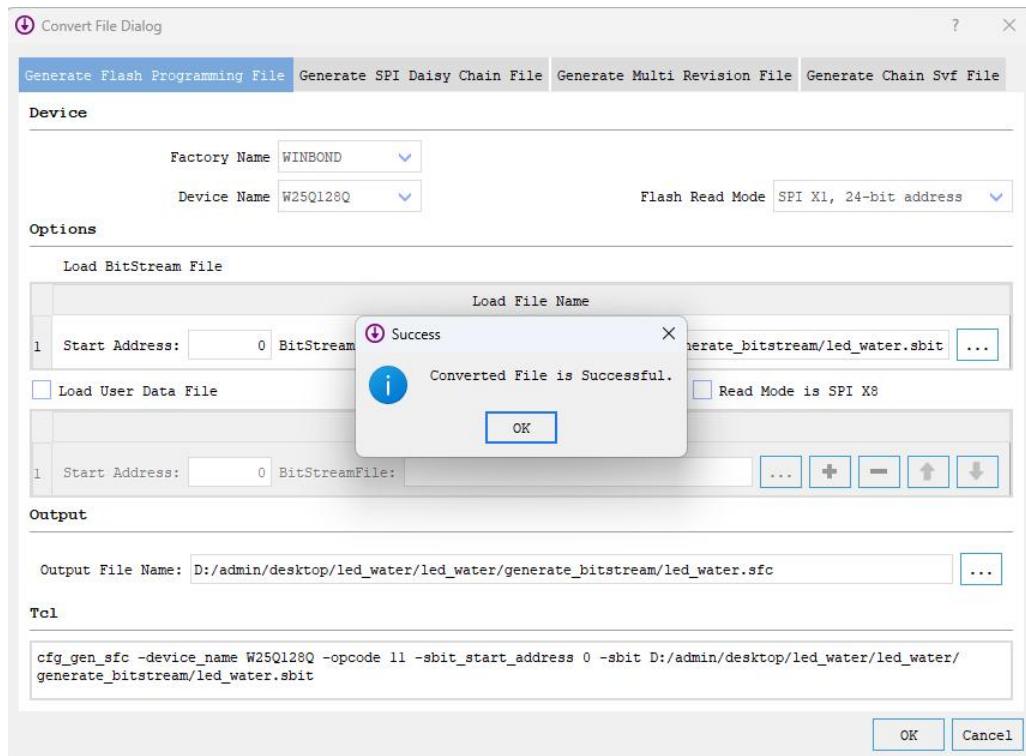

转化.sfc 文件成功后, 页面会如下图所示, 点击 OK;

图 7.7-36

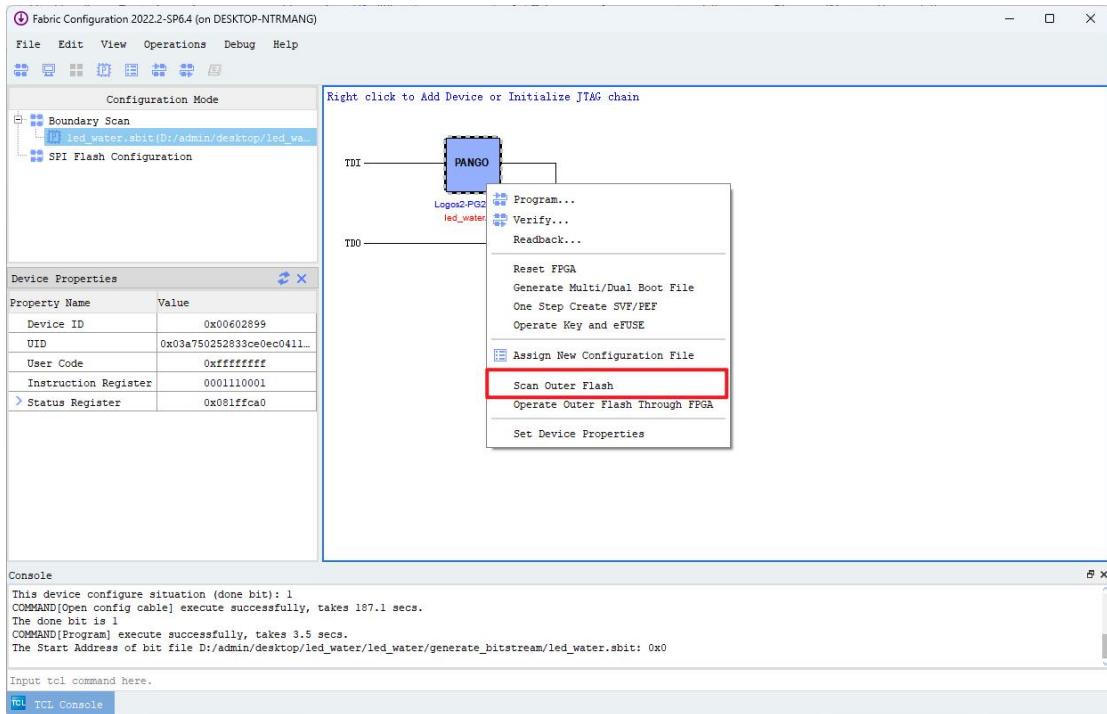

用户可通过右键下图位置, 点击 Scan Outer Flash;

图 7.7-37

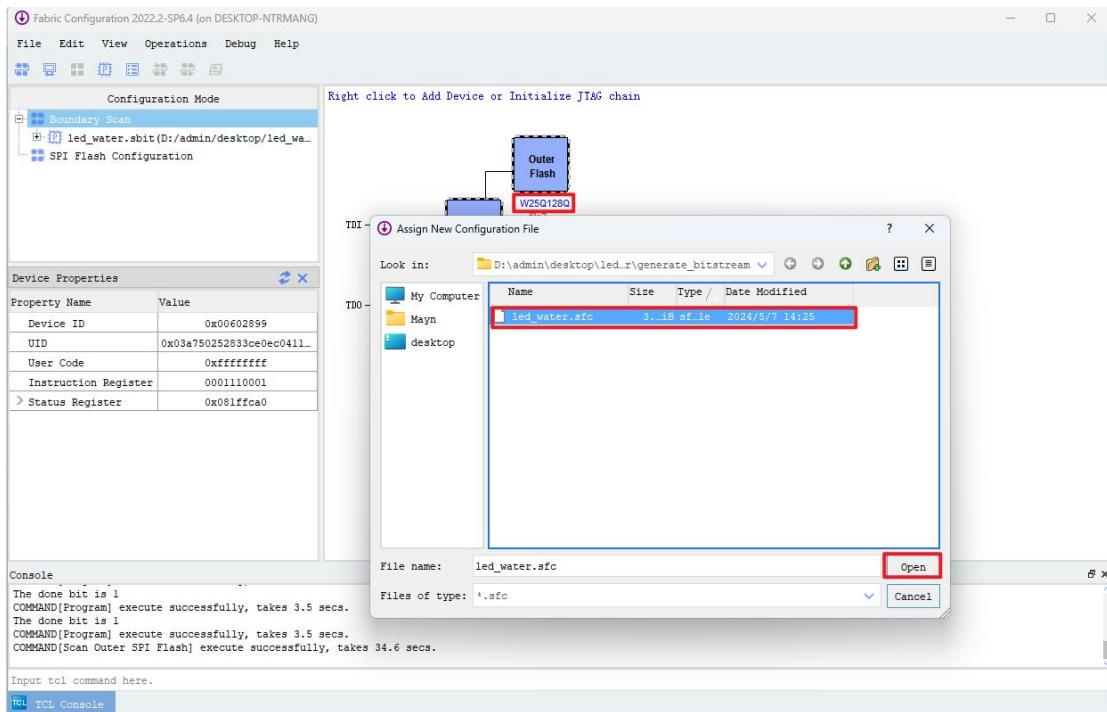

页面会显示板卡搭载的 Flash 的型号, 点击.sfc 文件, 点击 OPEN;

图 7.7-38

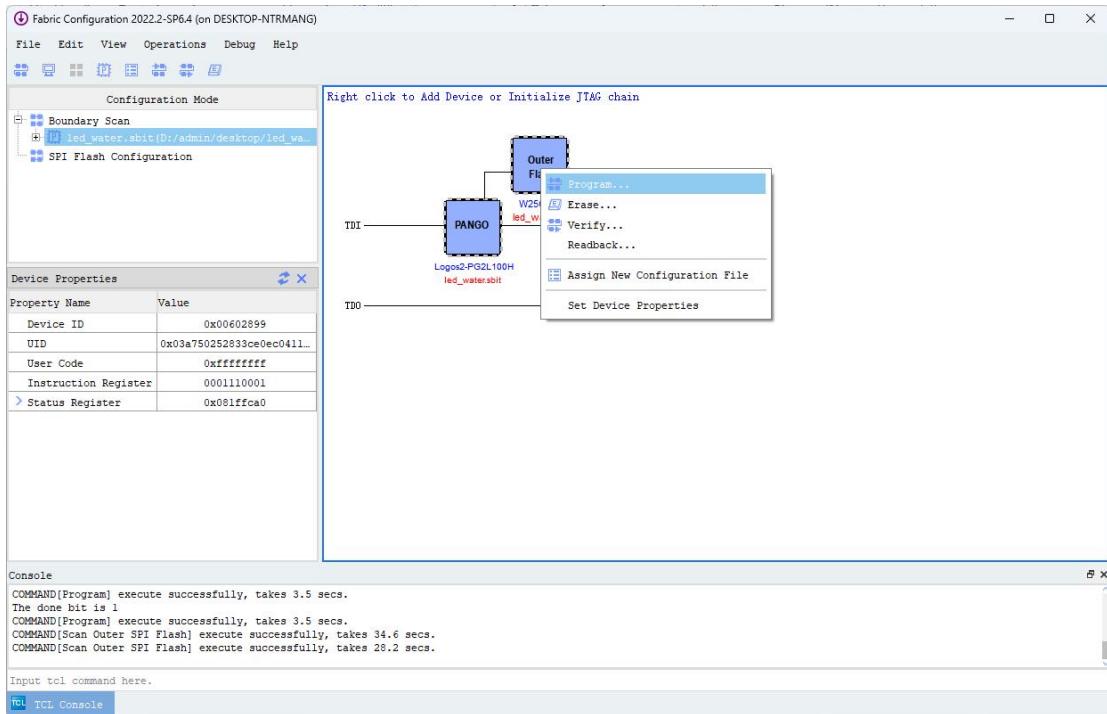

在下图位置点击鼠标右键后, 点击 Program;

图 7.7-39

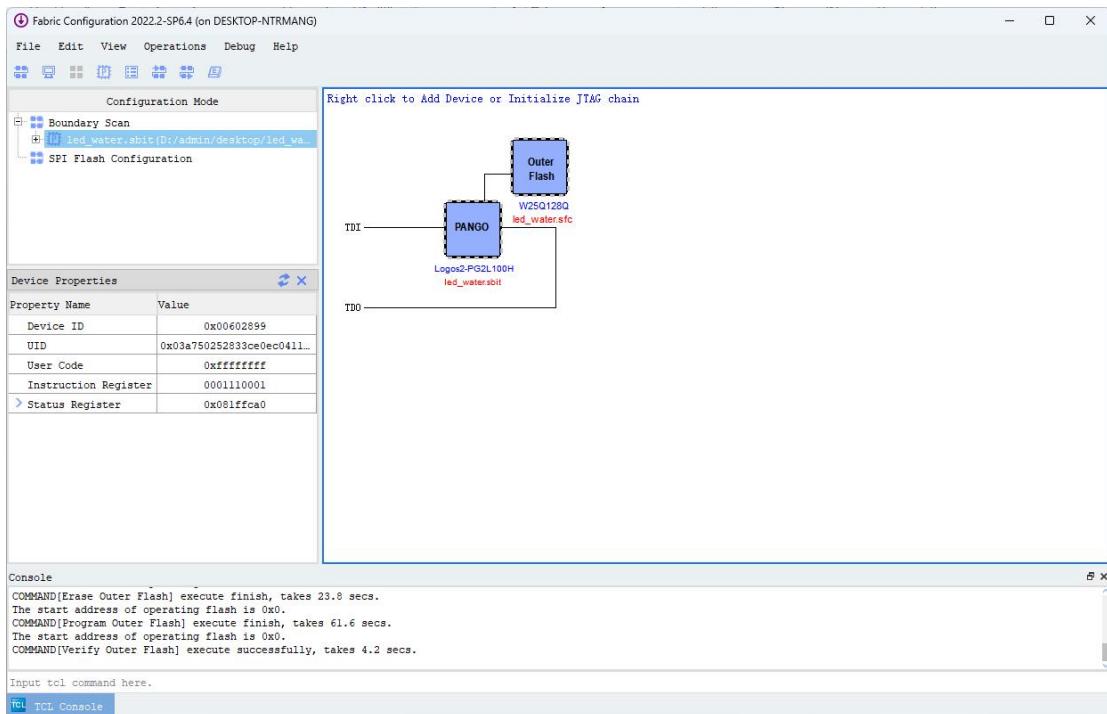

固化 Flash 成功如下图所示：

图 7.7-40

### 7.7.10. 上板验证

连接好电源和 jtag, 然后打开板卡上的电源;

```

File Edit View Project Process Tools Window Help

File Navigator Report Summary Project Directory 01_led_test.v

Sources Files

PG2L100H-6FBG676

Designs (1)

led_test (01_led_test.v)

Constraints (2)

led_test.fdf (D:/ziguang_demo/MES2L100Hv2,

led_test_syn.fic (D:/ziguang_demo/MES2L100Hv2)

Simulation (1)

tb_led_test (tb_led_test.v)

```

```

19 //////////////////////////////////////////////////////////////////

20

21

22 `define UD #1

23 //27MHZ T = 27MHZ 1秒钟 27_000_000个上升沿 0.5s 13_500_000个

24 // 0.1 27_000_000

25

26

27 module led_test

28 #(

29   parameter CNT_MAX = 26'd13_500_000

30 )

31 (

32   input  clk,

33   input  rstn,

34   output [7:0] led

35 );

36

37

38

39 //////////////////////////////////////////////////////////////////

```

图 7.7-41

点击 PDS 软件上方的下载按钮, 红框所示部分:

图 7.7-42

在弹出来的界面再点击如图红框部分:

图 7.7-43

点击后会自动搜索设备，如果连线没问题的话可以看到自动弹出一个界面来选择 sbit。然后选择 led\_test.sbit；

图 7.7-44

右键“芯片”，然后选择 program，等待烧录完成即可。接下来观察上板现象。

## 8. 基于紫光 FPGA 的 UART 串口通信

### 8.1. 实验简介

实验目的:

实现 FPGA 与 PC 之间的串口通信, 并使用 PDS 软件内置的在线调试工具验证收发数据的准确性。并根据接收到的不同数据去点亮开发板上的 LED 灯。

同时掌握在线 Debugger 工具的使用。

实验环境:

Window11

PDS2022.2-SP6.4

硬件环境:

MES2L676-100HP-MINI

### 8.2. 实验原理

#### 8.2.1. 串口原理

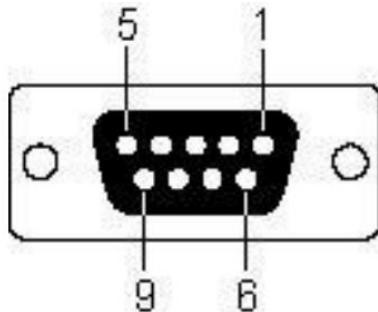

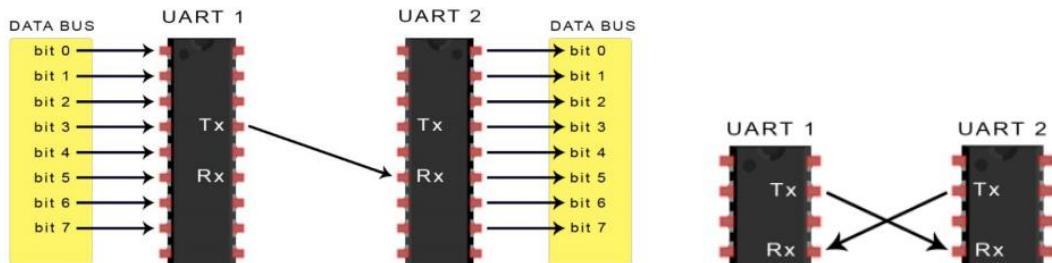

从图 8.2-1 我们可以看到标准串口接口是 9 根线, 具体含义如下:

图 8.2-1

数据线:

TXD (pin 3): 串口数据输出(Transmit Data)

RXD (pin 2): 串口数据输入(Receive Data)

握手:

RTS (pin 7): 发送数据请求(Request to Send)

CTS (pin 8): 清除发送(Clear to Send)

DSR (pin 6): 数据发送就绪(Data Send Ready)

DCD (pin 1): 数据载波检测(Data Carrier Detect)

DTR (pin 4): 数据终端就绪(Data Terminal Ready)

地线:

GND (pin 5): 地线

其它:

RI (pin 9): 铃声指示

通常我们用 RS232 串口仅用到了 9 根传输线中的三根: TxD, RxD, GND。但是对于数据传输, 双方必须对数据传输采用使用相同的波特率, 约定同样的传输模式 (传输架构, 握手条件 等)。尽管这种方法对于大多数应用已经足够, 但是对于接收方过载的情况这种使用受到限制。

RS232 的串口连接方式:

图 8.2-2

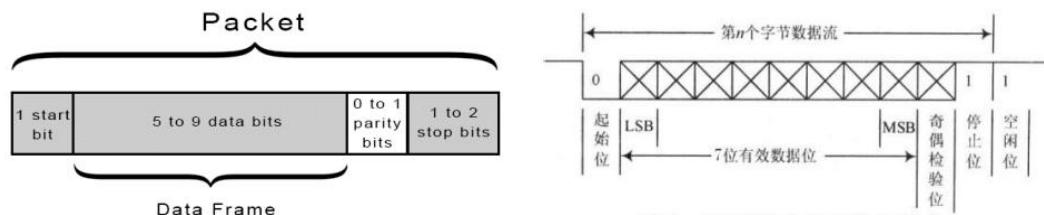

串口传输协议如下:

图 8.2-3

起始位: 先发出一个逻辑“0”信号, 表示传输字符的开始。

数据位: 可以是 5~8 位逻辑“0”或“1”。如 ASCII 码 (7 位), 扩展 BCD 码 (8 位)。LSB 表示低位, MSB 表示高位, 有效数据的传输顺序为低位在前高位在后。

校验位: 数据位加上这一位后, 使得“1”的位数应为偶数(偶校验)或奇数(奇校验)。

停止位: 它是一个字符数据的结束标志。可以是 1 位、1.5 位、2 位的高电平。

空闲位: 处于逻辑“1”状态, 表示当前线路上没有资料传送。

波特率: uart 中的波特率就可以认为是比特率, 即每秒传输的位数(bit)。一般选波特率都会有 9600, 19200, 115200 等选项。其实意思就是每秒传输这么多个比特位数(bit)。

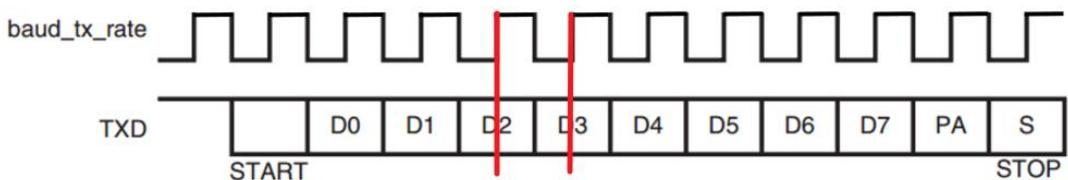

引入波特率的概念后可得到串口的传输节奏如下:

图 8.2-4

细心的话可以发现数据的传输都是在数据稳定后的中心时刻, 接收数据其实也是, 都是在中心时刻采集数据,

此时的数据是最稳定的。

### 8.2.2.串口发送字符

从前面串口协议中可以了解到串口每次传输可以以有 5~8bit 数据, 在计算机中字符通常用 ASCII 码 (7bit) 表示, 所以字符的发送可以用 ASCII 码发送。

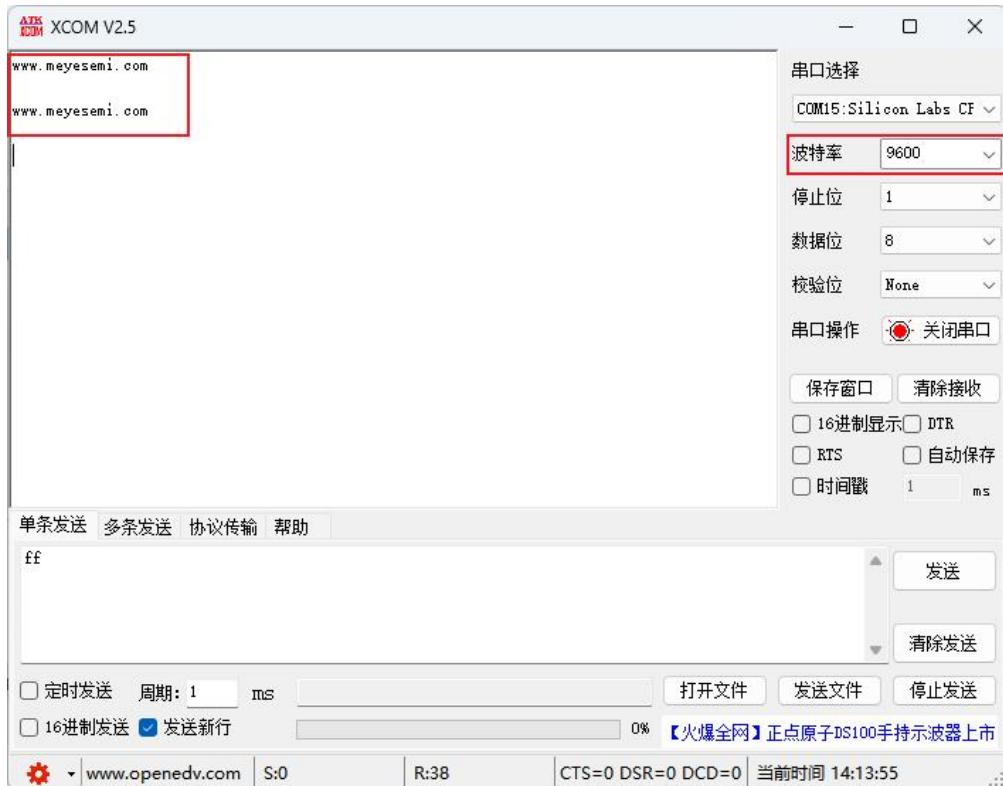

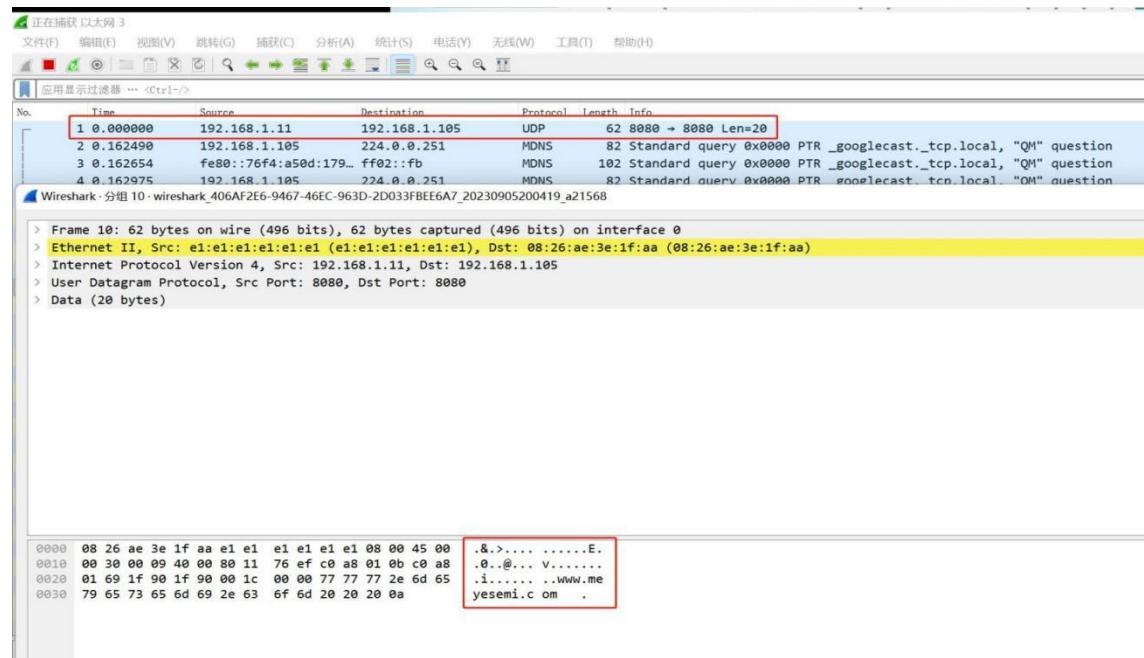

查询 ASCII 码表格可得到: “[www.meyesemi.com](http://www.meyesemi.com)” 用到的字符对应 ASCII 码;

```

8'h1  : write_data <= `UD 8'h77; // ASCII code is w

8'h2  : write_data <= `UD 8'h77; // ASCII code is w

8'h3  : write_data <= `UD 8'h77; // ASCII code is w

8'h4  : write_data <= `UD 8'h2E; // ASCII code is .

8'h5  : write_data <= `UD 8'h6D; // ASCII code is m

8'h6  : write_data <= `UD 8'h65; // ASCII code is e

8'h7  : write_data <= `UD 8'h79; // ASCII code is y

8'h8  : write_data <= `UD 8'h65; // ASCII code is e

8'h9  : write_data <= `UD 8'h73; // ASCII code is s

8'ha  : write_data <= `UD 8'h65; // ASCII code is e

8'hb  : write_data <= `UD 8'h6D; // ASCII code is m

8'hc  : write_data <= `UD 8'h69; // ASCII code is i

8'hd  : write_data <= `UD 8'h2E; // ASCII code is .

8'he  : write_data <= `UD 8'h63; // ASCII code is c

8'hf  : write_data <= `UD 8'h6F; // ASCII code is o

8'h10 : write_data <= `UD 8'h6D; // ASCII code is m

```

图 8.2-5

### 8.2.3.串口接收数据点灯

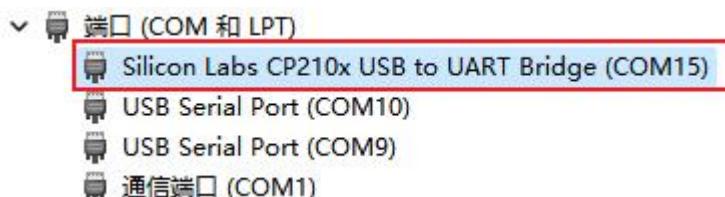

收到的数据最终转为 8bit 的并行数据, rx\_data, 而开发板上刚好也有 8 个 led 灯。1 表示亮, 0 表示灭, 那么 8 个 LED 灯就等同于 8bit 的变量。可以用二进制来表示, 例如要全亮, 那就是 8'b1111\_1111, 因此我们往 FPGA 发送串口数据时, 可以通过 16 进制的方式来发送, 例如我要点亮 LED1 和 LED5, 那就发送 8'b0001\_0001, 转为 16 进制就是 8'h11。所以可以根据该规律去点亮开发板上的每一个灯。

## 8.3. 接口列表

uart\_top.v 模块是整个工程的顶层模块

| 端口      | I/O    | 位宽 | 描述          |

|---------|--------|----|-------------|

| clk     | input  | 1  | 系统时钟, 27MHZ |

| uart_rx | input  | 1  | 串口接收总线      |

| led     | output | 8  | led 灯信号     |

| uart_tx | output | 1  | 串口发送总线      |

uart\_data\_gen.v 模块 是生成要发送的串口数据。

| 端口            | I/O    | 位宽 | 描述                         |

|---------------|--------|----|----------------------------|

| clk           | input  | 1  | 系统时钟, 27MHZ                |

| read_data     | input  | 8  | 预留的 8bit 串口接收数据信号, 可作串口回环。 |

| tx_busy       | input  | 1  | 1: 表示正在发送 0: 表示空闲          |

| write_max_num | input  | 8  | 发送的字符的个数                   |

| write_data    | output | 8  | 待发送的数据                     |

| write_en      | output | 1  | 串口数据有效信号                   |

uart\_tx.v 模块, 主要完成串口发送功能。将要发送到 PC 的 8bit 并行数据转为一个波特周期发送一个 bit。

| 端口             | I/O    | 位宽        | 描述                |

|----------------|--------|-----------|-------------------|

| <b>BPS_NUM</b> | /      | <b>16</b> | <b>波特率分频系数</b>    |

| clk            | input  | 1         | 系统时钟, 27MHZ       |

| tx_data        | input  | 8         | 待串口发送的数据          |

| tx_pluse       | input  | 1         | 发送模块的触发信号, 一个脉冲信号 |

| uart_tx        | output | 1         | 串口发送总线            |

| tx_busy        | output | 1         | 1: 表示正在发送 0: 表示空闲 |

uart\_rx.v 模块, 主要完成串口接收功能, 将 PC 发送到 FPGA 的串行的 8bit 数据转为并行的 8bit 数据给到用户使用。

| 端口             | I/O    | 位宽        | 描述             |

|----------------|--------|-----------|----------------|

| <b>BPS_NUM</b> | /      | <b>16</b> | <b>波特率分频系数</b> |

| clk            | input  | 1         | 系统时钟, 27MHZ    |

| uart_rx        | input  | 1         | 串口接收总线         |

| rx_data        | output | 8         | 接收到的 8bit 并行数据 |

| rx_en          | output | 1         | 接收数据使能信号       |

| rx_finish      | output | 1         | 接收完成信号         |

#### 8.4. 工程说明

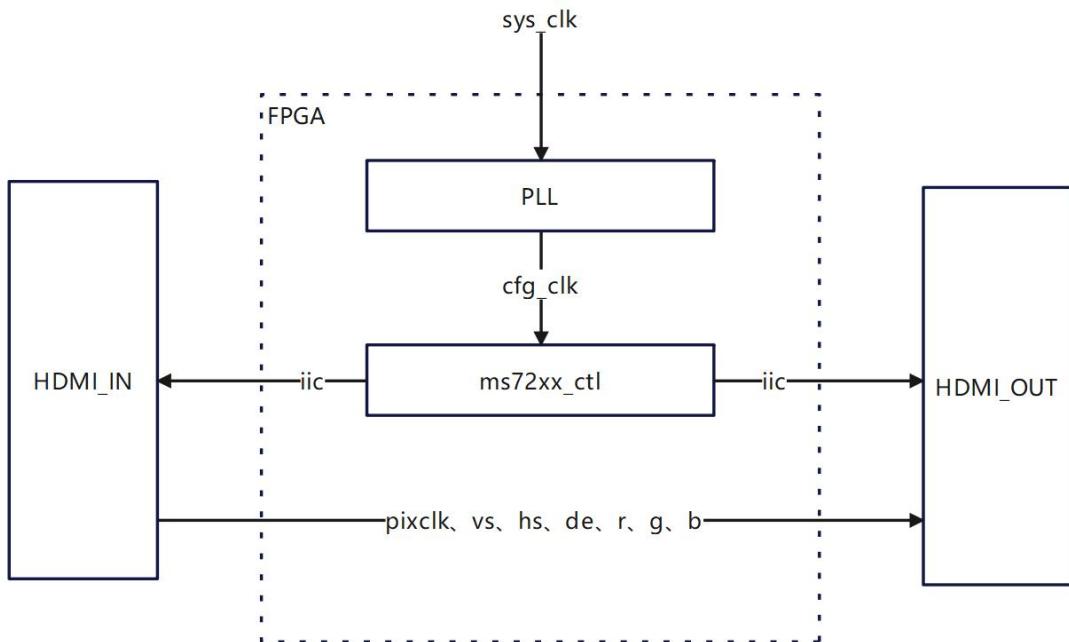

图 8.4-1

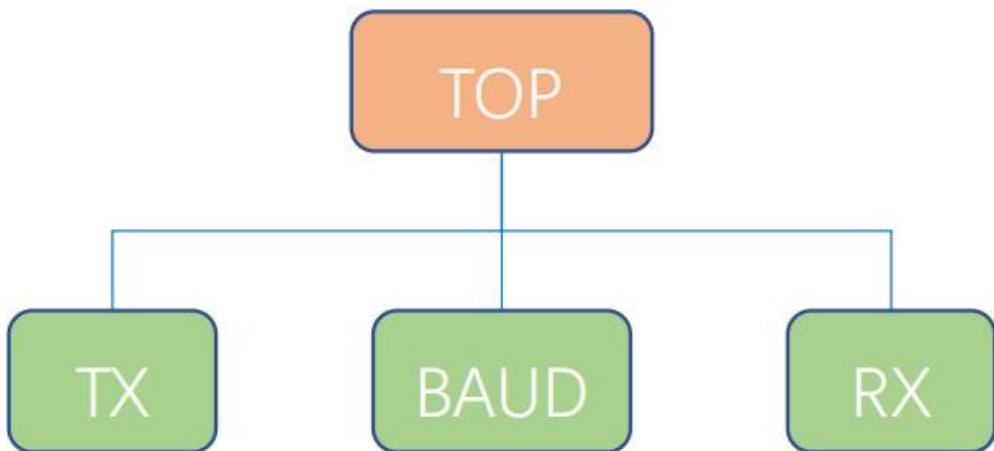

实验的架构如图 8.4-1 所示, 分为 TX(发送模块)、BAUD(波特率计算模块)、RX(接收模块)。而 TOP 模块是顶层, 例化了这三个模块。我们从原理上分析波特率的计算是一个计数器, 发射和接收可复用, 但是我们在设计时为保持 TX 或 RX 的完整性, 故将波特周期计数器集成在各自模块内部。

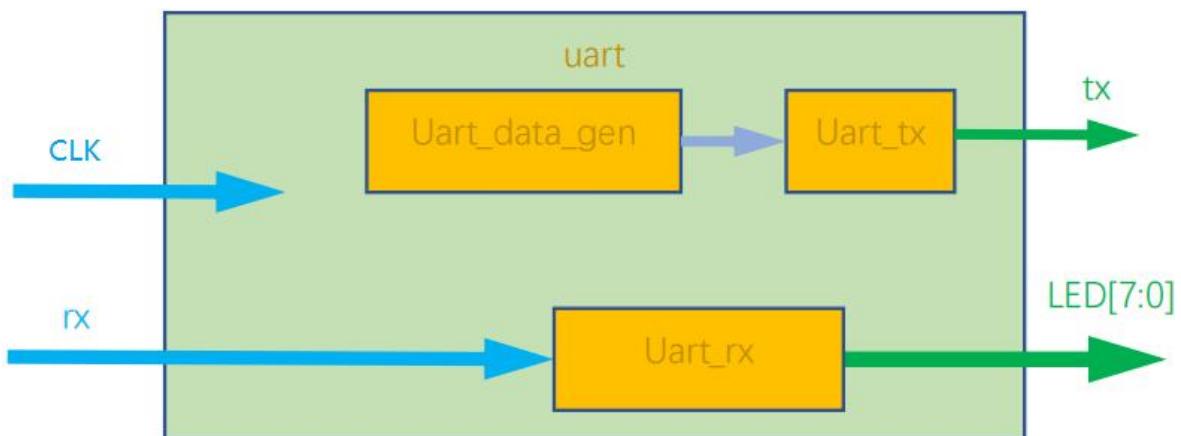

图 8.4-2

图 8.4-2 所示的 Uart\_data\_gen 模块是用来生成要发送的数据。即 “www.meyesemi.com” 这一串字符。生成后的数据给到 uart\_tx 模块让其发送到 PC。Uart\_rx 模块负责接收 PC 发来的数据, 并做解析, 然后点亮开发板上的 LED 灯。

#### 8.5. 代码模块说明

实现功能: 接收到一个发送命令信号时, 将 data[7:0] -> 依次发出{start,data[0:7],stop}共 10bit 数据 (无校验位, 停止位 1bit);

这里主要讲解代码的重点设计部分, 完整源码大家请参考工程源码, 然后结合文档一起理解比较方便。

代码的设计主要是通过 bit 计数与 baud 计数控制状态跳转, 在状态机中输出;

### 8.5.1.串口发送模块

```

always @ (posedge clk)

begin

if(tx_en)

begin

case(tx_state)

IDLE    : uart_tx <= `UD 1'h1;          //空闲状态输出高电平

SEND_START : uart_tx <= `UD 1'h0;       //start 状态发送一个波特周期的低电平

SEND_DATA :                      //发送状态每个波特周期发送一个 bit;

begin

case(tx_bit_cnt)

3'h0 : uart_tx <= `UD tx_data[0];

3'h1 : uart_tx <= `UD tx_data[1];

3'h2 : uart_tx <= `UD tx_data[2];

3'h3 : uart_tx <= `UD tx_data[3];

3'h4 : uart_tx <= `UD tx_data[4];

3'h5 : uart_tx <= `UD tx_data[5];

3'h6 : uart_tx <= `UD tx_data[6];

3'h7 : uart_tx <= `UD tx_data[7];

default: uart_tx <= `UD 1'h1;

endcase

end

SEND_STOP : uart_tx <= `UD 1'h1;      //发送停止状态 输出 1 个波特周期高电平

default   : uart_tx <= `UD 1'h1;      // 其他状态默认与空闲状态一致, 保持高电平输出

endcase

end

else

uart_tx <= `UD 1'h1;

end

```

在代码的第 5 行中有个 tx\_state 的变量, 一共有四个状态 IDLE(空闲状态)、SEND\_START(开始发送状态)、SEND\_DATA(发送数据状态)、SEND\_STOP(发送停止状态)。根据我们的串口发送协议。在 IDLE 状态下就直接保持 uart\_tx 总线为高电平即可。在

SEND\_START 状态下发送起始为, 一个波特周期的低电平, 之后跳转到 SEND\_DATA 状态, 发送 8bit 数据, 通过 tx\_bit\_cnt 来计数一共发了多少个 bit, tx\_bit\_cnt 从 0 计数到 7, 一共发送 8bit 数据, 需要注意的是, 发送时先把 tx\_data 的低位发出去。发送完 8bit 数据后跳转到 SEND\_STOP 状态, 输出一个波特周期的高电平, 表示停止。至此就完成了一次串口数据的发送。

下面的这两个 always 块主要完成波特率的生成, 在串口接收模块里也有相同的代码, 故在接收模块里不再讲解。

```

always @ (posedge clk)

begin

if(!tx_en)

tx_bit_cnt  <= `UD 3'h0;

else if((tx_bit_cnt == 3'h7) && (clk_div_cnt == BPS_NUM))

tx_bit_cnt  <= `UD 3'h0;

else if((tx_state == SEND_DATA) && (clk_div_cnt == BPS_NUM))

tx_bit_cnt  <= `UD tx_bit_cnt + 3'h1;

else

tx_bit_cnt  <= `UD tx_bit_cnt;

end

always @ (posedge clk)

begin

if(clk_div_cnt == BPS_NUM || (~tx_pluse_reg & tx_pluse))

clk_div_cnt  <= `UD 16'h0;

else

clk_div_cnt  <= `UD clk_div_cnt + 16'h1;

end

```

代码 1-11 行完成 tx\_bit\_cnt 的计数, 代码 12-18 行, 完成波特周期的计数, clk\_div\_cnt 是用来对我们输入进来的 50MHZ 的时钟进行分频, 以此来得到波特周期。其中 BPS\_NUM 的值根据不同的波特率会有不同的结果, 默认是 115200, 所以  $BPS\_NUM = 50\text{MHz}/115200 \approx 434$ 。计算公式为  $BPS\_NUM = CLK/BAUD\_RATE$ 。需要注意的是, 第 14 行的判断条件, clk\_div\_cnt 的清 0 除了每次计数到 BPS\_NUM 后需要清 0 之外, 当发送使能的上升沿到来时, 我们也需要清 0。tx\_pluse 实际是发送使能信号, tx\_pluse\_reg 是 tx\_pluse 打一拍后的信号,  $\sim tx\_pluse\_reg \& tx\_pluse$  表示是获取 tx\_pluse 的上升沿。所以, 该条件表示我们要开始发送数据了, 为了能够正常计数波特周期, 故要把 clk\_div\_cnt 清 0, 让其重新计数。

代码第三行, 当 tx\_en 为低电平时, 表示不处于发送状态, 所以一直置 0。代码第 5 行, 当 tx\_bit\_cnt==7 且 clk\_div\_cnt==BPS\_NUM 时, 把 tx\_bit\_cnt 清空, 因为此时已经发送了 8 个 bit 的数据。代码第 7 行, 在发送状态下, 每到来一个波特周期就让 tx\_bit\_cnt 不断+1。其余情况下, tx\_bit\_cnt 保持不变。需要注意的是, 波特率在发送模块和接收模块里都是一样的, 故接收模块将不讲解这一部分。

### 8.5.2. 串口接收模块

串口接收模块是发送模块的逆过程, 设计思路区别不大, 但是有如下几点需要注意:

1. 接收开始信号, 当 rx 下降沿到来后保持几个时钟周期的低电平, 表明进入接收 start;

2. 接收数据提取位置, 在前面讲发送的时候都是在波特周期开始的位置变更数据, 但是接收数据在提取时需要在 rx 稳定时刻取数, 也就是在波特周期的中间位置取数;

3. 最终输出数据锁存, 在最后 1bit 存入寄存器后需要对接收数据锁存, 并在之后需要给出数据使能信号, 表示输出数据有效;

串口接收代码的重点部分如下:

```

//状态机状态跳转条件及跳转规律

always @ (*)

begin

case(rx_state)

IDLE      :

begin

if(start)                      //监测到 start 信号到来, 下一状态跳转到 start 状态

rx_state_n = RECEIV_START;

else

rx_state_n = rx_state;

end

RECEIV_START   :

begin

if(clk_div_cnt == BPS_NUM)      //已完成接收 start 标志信号

rx_state_n = RECEIV_DATA;

else

rx_state_n = rx_state;

end

RECEIV_DATA    :

begin

if(rx_bit_cnt == 3'h7 && clk_div_cnt == BPS_NUM) //已完成 8bit 数据的传输

rx_state_n = RECEIV_STOP;

else

rx_state_n = rx_state;

end

RECEIV_STOP    :

begin

if(clk_div_cnt == BPS_NUM)      //已完成接收 stop 标志信号

rx_state_n = RECEIV_END;

else

rx_state_n = rx_state;

end

RECEIV_END    :

```

```

begin

if(!uart_rx_1d) //数据线重新被拉低, 表示新数据传输又发送 start 标志信号, 需要跳转到 start

状态

rx_state_n = RECEIV_START;

else //没有其他状况出现时, 回到空闲状态, 等待 start 信号的到来

rx_state_n = IDLE;

end

default : rx_state_n = IDLE;

endcase

end

// 状态机输出

always @ (posedge clk)

begin

case(rx_state)

IDLE ,

RECEIV_START : //在空闲和 start 状态时将接收数据缓冲寄存器和数据使能置位;

begin

rx_en <= `UD 1'b0;

rx_data_reg <= `UD 8'h0;

end

RECEIV_DATA :

begin

if(clk_div_cnt == BPS_NUM[15:1]) //在一个波特周期的中间位置取数据线上传输的数据;

rx_data_reg <= `UD {uart_rx , rx_data_reg[7:1]}; //以循环右移的方式将 uart_rx 数据填入

缓存寄存器的最高位 (Uart 传输低位在前, 最后一个 bit 刚好是最高位)

end

RECEIV_STOP :

begin

rx_en <= `UD 1'b1; // 输出使能信号, 表示最新的数据输出有效

rx_data <= `UD rx_data_reg; // 将缓冲寄存器的值赋值给输出寄存器

end

RECEIV_END :

begin

rx_data_reg <= `UD 8'h0;

end

endcase

end

```

```

default: rx_en <= `UD 1'b0;

endcase

end

```

代码的 1-42 行主要完成 rx\_state 的状态跳转。一共有 5 个状态。IDLE(空闲状态)、RECEIV\_START(接收开始状态)、RECEIV\_DATA(接收数据状态)、RECEIV\_stop(停止接收状态)、RECEIV\_END(接收结束状态)。在 IDLE 状态下, 等待 start 信号到来, 一旦 start 信号拉高, 跳转到 RECEIV\_START 状态。在 RECEIV\_START 状态下经过一个波特周期后就跳转到 RECEIV\_DATA 状态, 之后经过 8 个波特周期, 即接收 8bit 数据后再跳转到 RECEIV\_STOP 状态。在 RECEIV\_STOP 下, 等待一个波特周期后跳转到 RECEIV\_END 状态, 整个接收流程到此结束。

接下来查看代码的 45-70 行, 主要执行 rx\_state 在不同状态下的逻辑操作。在 IDLE 和 RECEIV\_START 状态下都将接收使能和 rx\_data\_reg(接收数据缓存)置 0, 等待接收数据到达。在 RECEIV\_DATA 状态下, 注意判断条件是 clk\_div\_cnt==BPS\_NUM[15:1], 在前面说过, 我们要在中心时刻采样数据才是最稳定的, 所以 BPS\_NUM[15:1] 其实就是 BPS\_NUM>>1, 即左移 1 位, 就是除以 2。所以该状态就是每次到达波特周期的中心时刻就把数据给到 rx\_data\_reg 进行缓存, 而 rx\_data\_reg <= {uart\_rx,rx\_data\_reg[7:1]} 则是将进来的 uart 数据不断右移, 最后的结果就是最先进的数据会放在低位。因为我们发送的时候也是先把最低位的数据先发出去, 所以这里就是把最先收到的数据放到低位, 这样就和发送的数据一一对应。在 RECEIV\_STOP 状态下, 拉高 rd\_en 信号, 表示接收的数据有效, 并将 rx\_data\_reg 的值赋值给 rx\_data(输出寄存器), 所以这个时刻下, rx\_data 和 rd\_en 是同步的, 因此读者要正确使用接收的数据话可以用 rd\_en 作为有效条件。在 RECEIV\_END 状态下, 将 rx\_data\_reg 清空。

而波特率生成模块都集成在模块内部, 并且和发送模块的一模一样, 故不再讲解。

### 8.5.3. 工程及现象

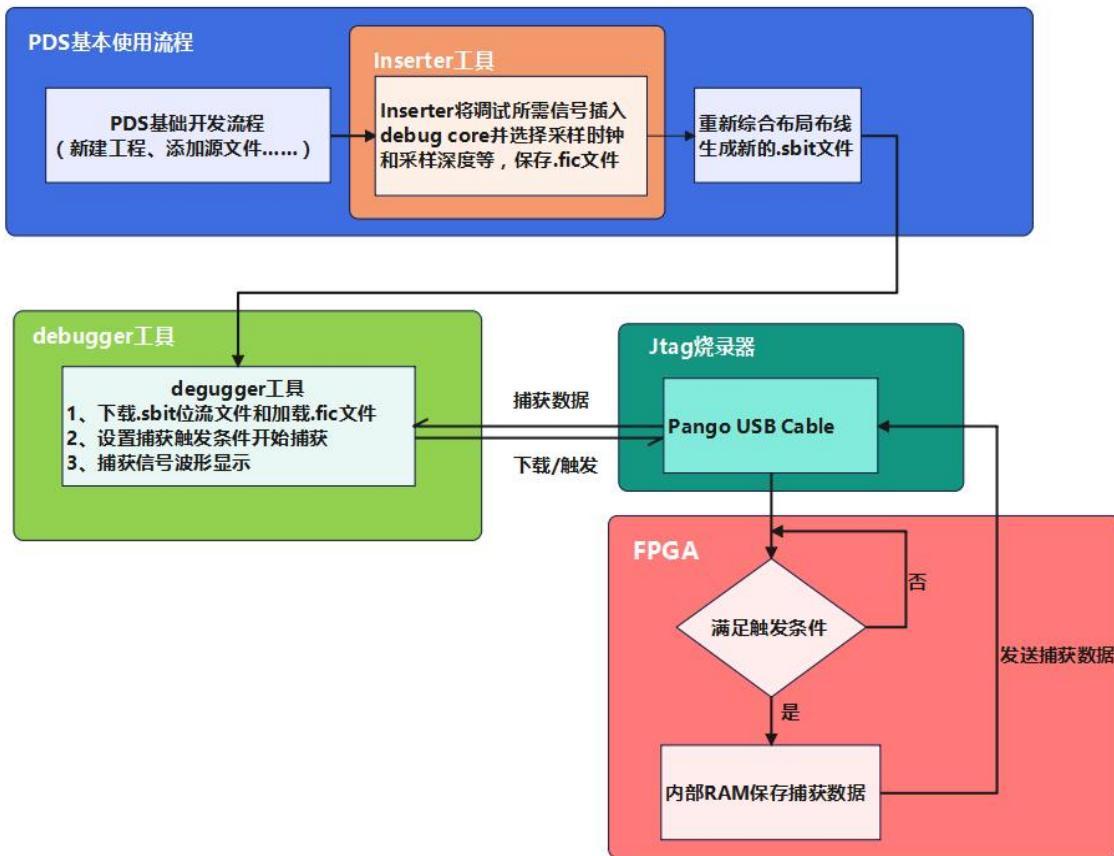

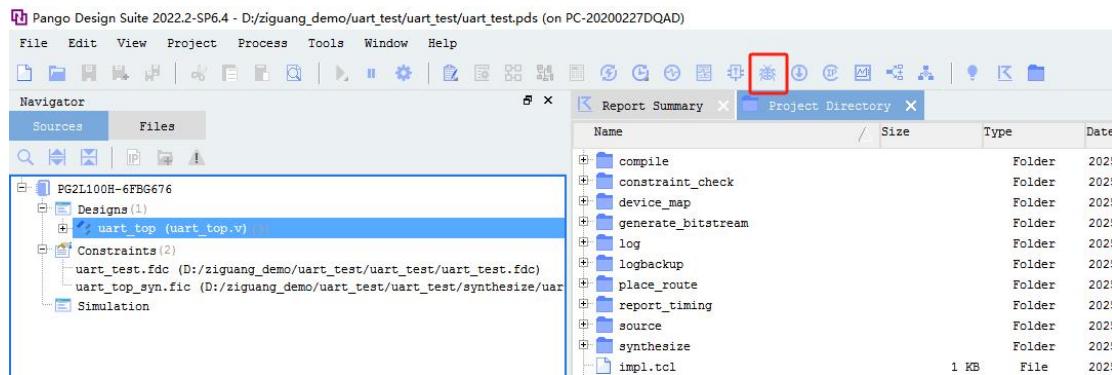

通过使用在线 Debugger 工具来抓取收到的串口数据, 并进行对比, 比较收到的和我们发送的是否一致。

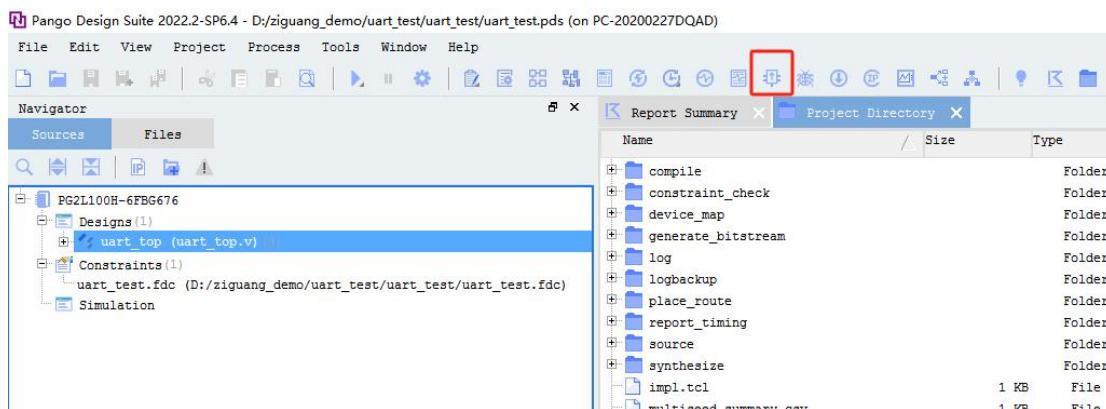

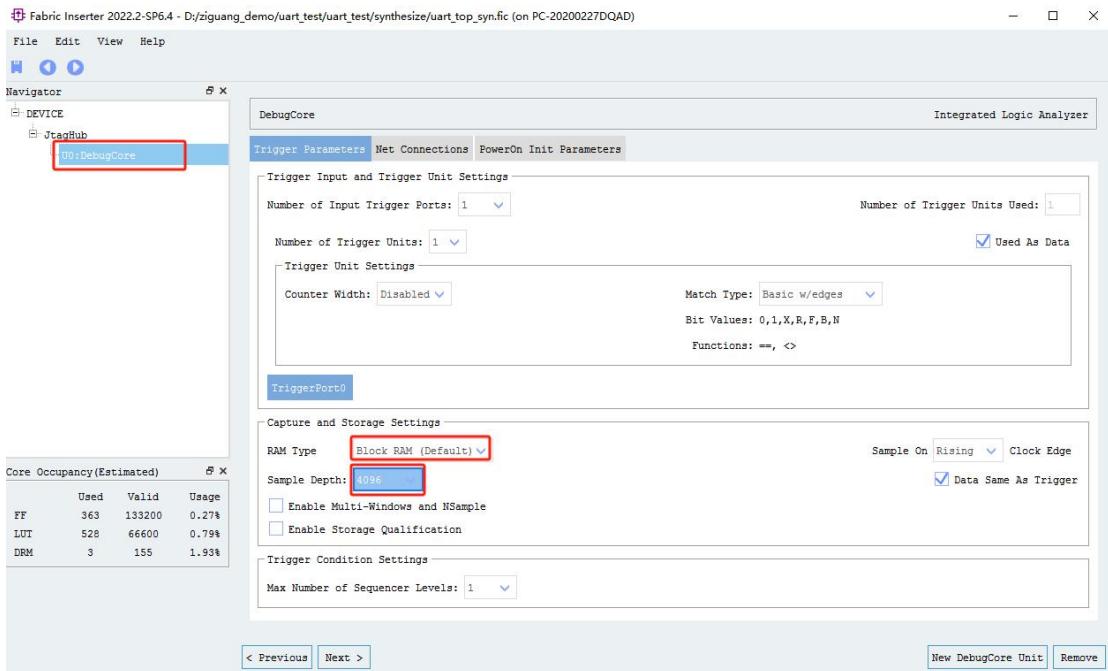

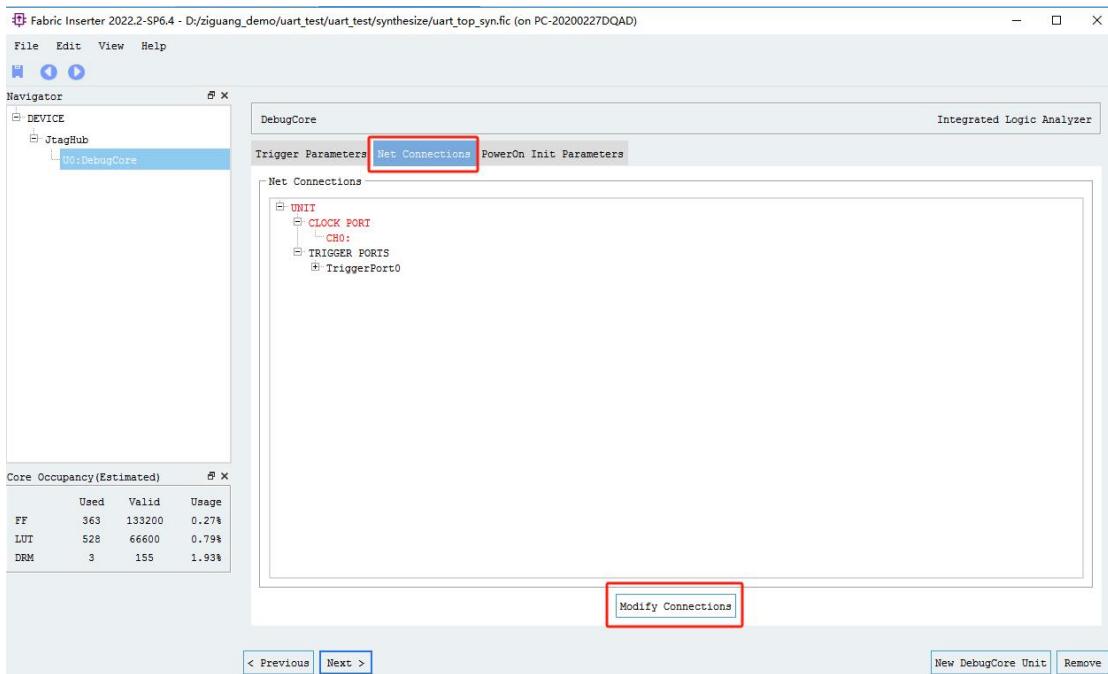

打开 PDS 上方工具栏的 Insert 工具, 如图所示:

图 8.5-1

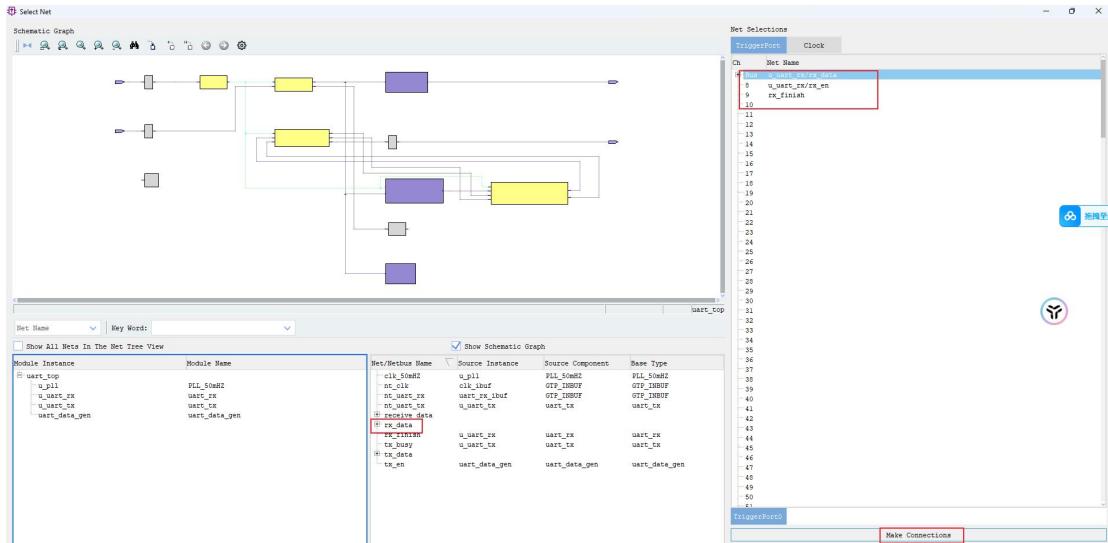

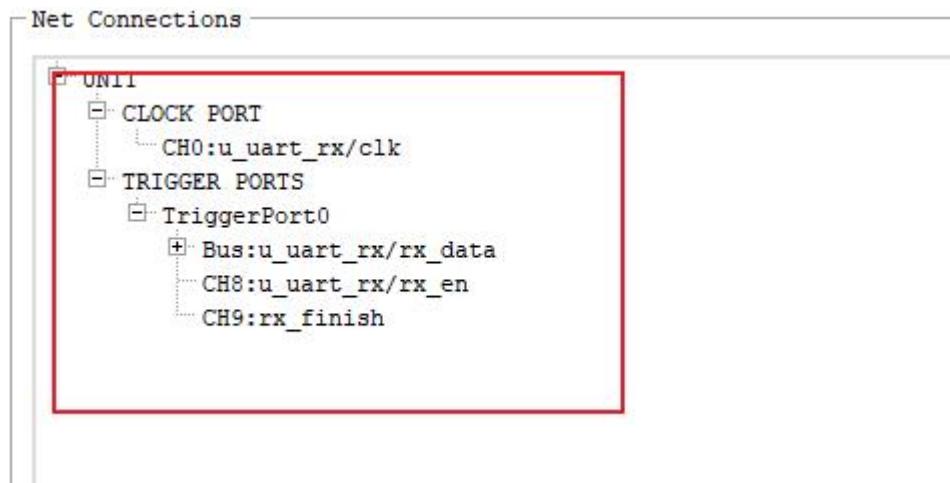

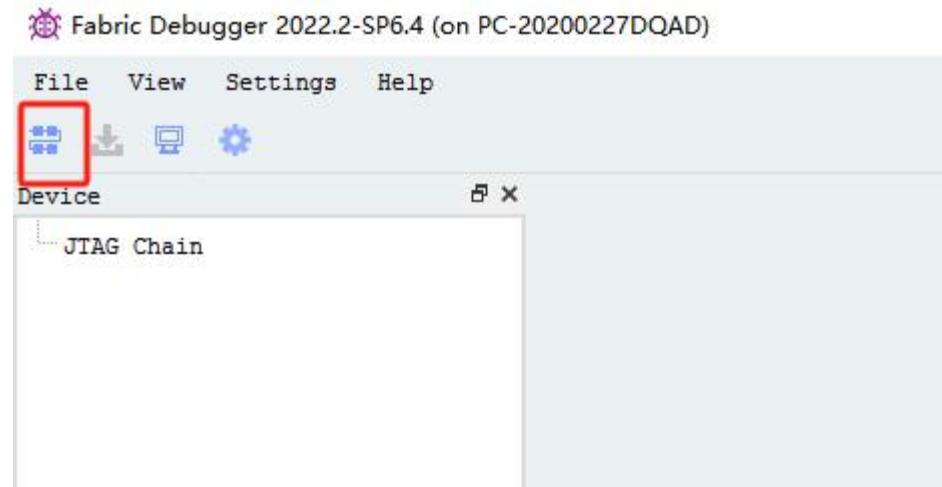

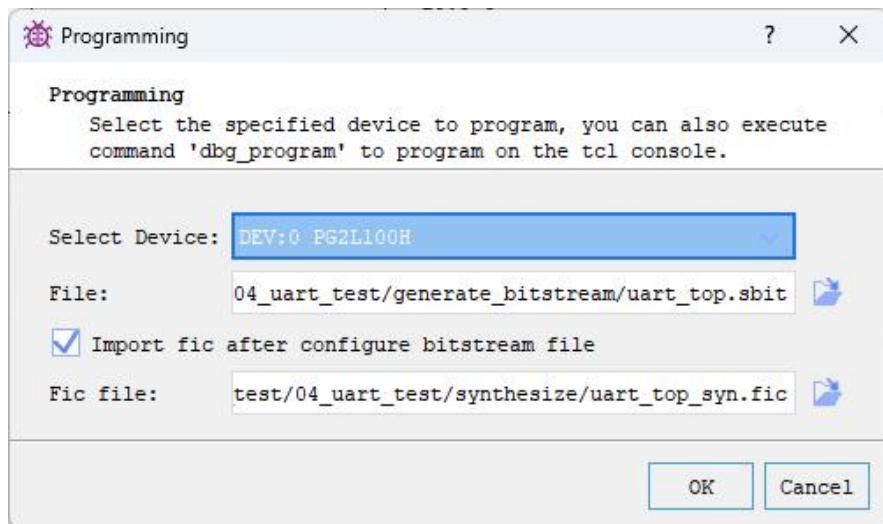

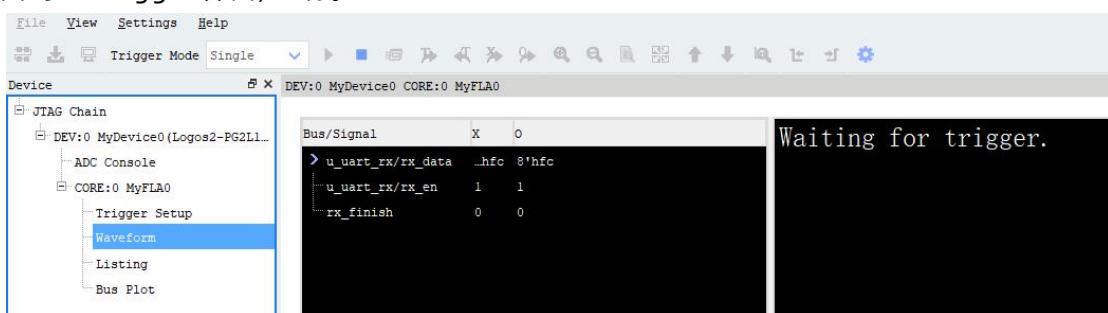

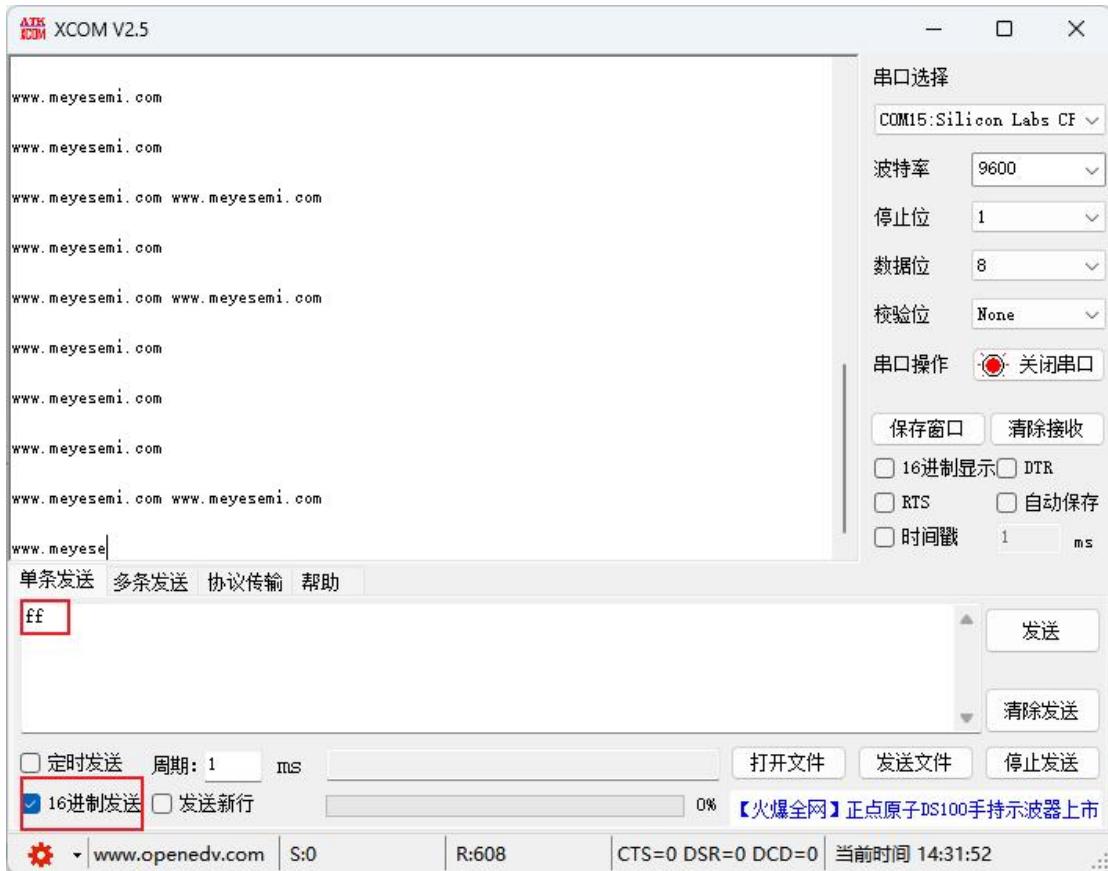

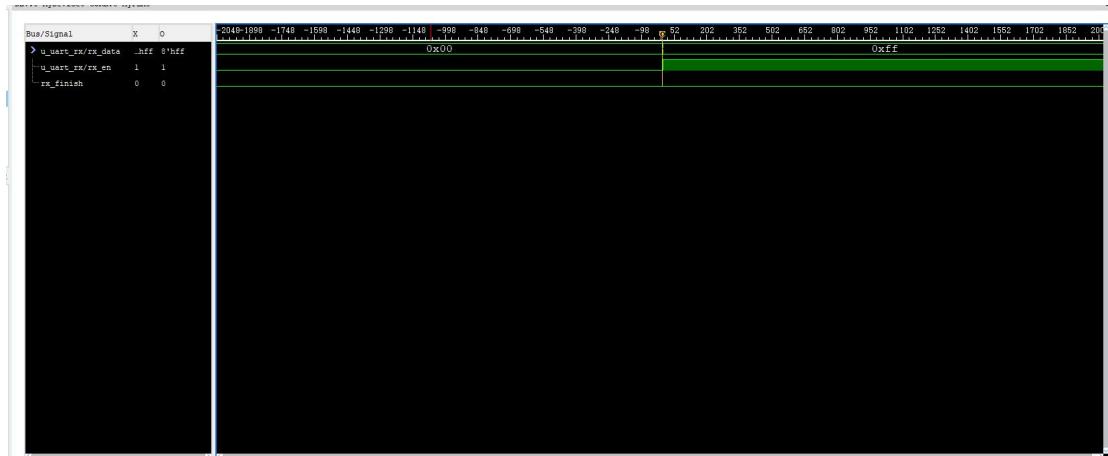

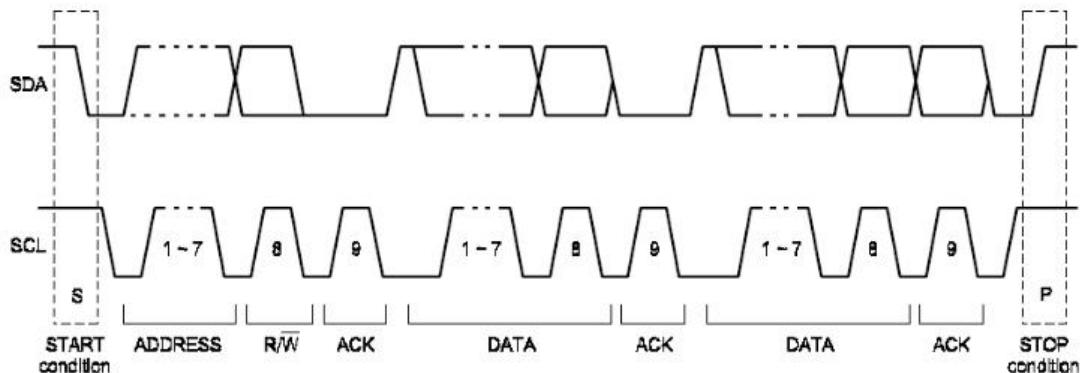

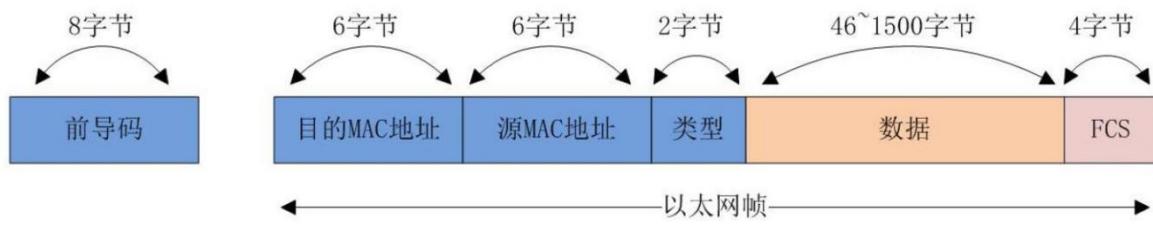

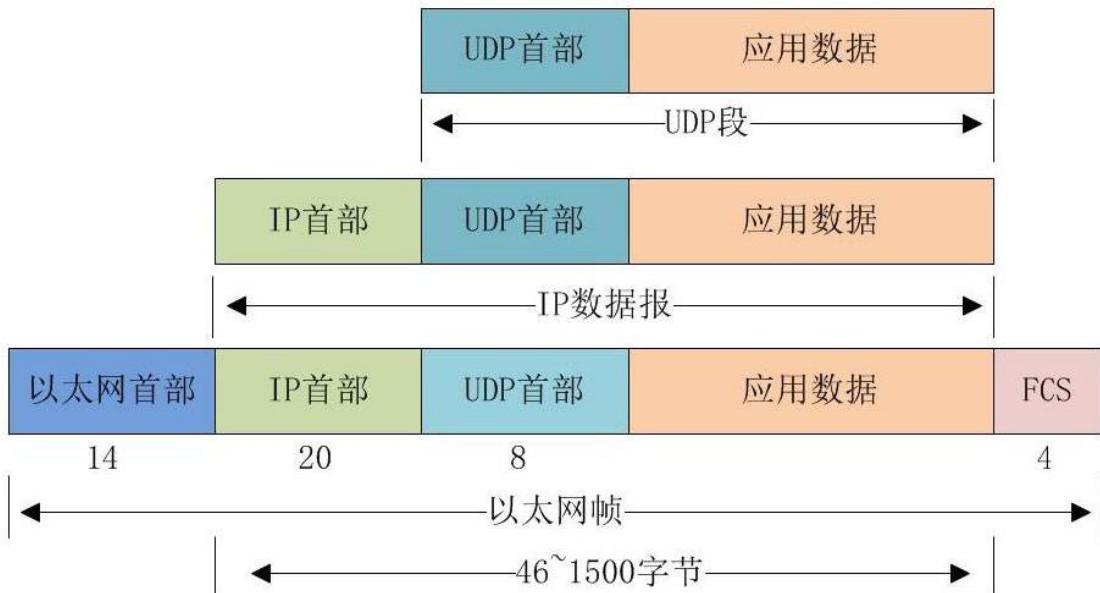

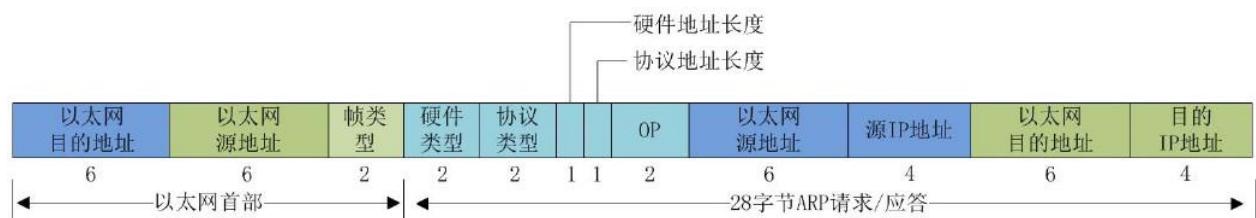

图 8.5-2