# MES2T900-390HP 硬件使用手册

硬件使用手册版本 : v1.1

时间 : 2025-04-24

公司 : 深圳市小眼睛科技有限公司

客服微信 : 17665247134

qq 群 : 808770961

淘宝店铺 : 小眼睛半导体

邮箱 : support@meyesemi.com

公司网址 : www.meyesemi.com

微信公众号 :

抖音 :

视频号 :

## 目录

|                          |        |

|--------------------------|--------|

| 1、开发系统介绍 .....           | - 1 -  |

| 1.1、 开发系统概述 .....        | - 1 -  |

| 1.2、 开发系统简介 .....        | - 2 -  |

| 1.2.1、 开发系统外设资源 .....    | - 2 -  |

| 1.2.2、 开发系统功能框图 .....    | - 3 -  |

| 2、核心板 .....              | - 5 -  |

| 2.1、核心板概述 .....          | - 5 -  |

| 2.2、系统描述 .....           | - 6 -  |

| 2.2.1、FPGA .....         | - 6 -  |

| 2.2.2、电源接口 .....         | - 7 -  |

| 2.2.3、时钟 .....           | - 9 -  |

| 2.2.4、上电 IO Status ..... | - 11 - |

| 2.2.5、JTAG 接口 .....      | - 11 - |

| 2.2.6、DDR4 .....         | - 12 - |

| 2.2.7、QSPI Flash .....   | - 16 - |

| 2.2.8、扩展 IO .....        | - 17 - |

| 3、扩展底板 .....             | - 18 - |

| 3.1、扩展底板简介 .....         | - 18 - |

| 3.2、外接接口通信 .....         | - 19 - |

| 3.2.1、网口 .....           | - 19 - |

| 3.2.4、PCIe x8 接口 .....   | - 20 - |

| 3.2.5、串口 .....           | - 22 - |

| 3.2.6、JTAG .....         | - 23 - |

| 3.3、HDMI .....           | - 24 - |

| 3.3.1、HDMI 输入接口 .....    | - 24 - |

| 3.3.2、HDMI 输出接口 .....    | - 27 - |

| 3.4、按键/指示灯/存储接口 .....    | - 29 - |

|                           |        |

|---------------------------|--------|

| 3.4.1、按键 .....            | - 29 - |

| 3.4.2、LED 灯 .....         | - 30 - |

| 3.4.3、EEPROM .....        | - 31 - |

| 3.4.4、PMOD 接口 .....       | - 32 - |

| 3.5、时钟 .....              | - 33 - |

| 3.5.1、125MHz 有源差分晶振 ..... | - 33 - |

| 3.6、FMC 连接器 .....         | - 34 - |

| 3.7、外接风扇 .....            | - 43 - |

| 3.8、供电电源 .....            | - 44 - |

| 3.9、底板尺寸图 .....           | - 46 - |

# 1、开发系统介绍

## 1.1、开发系统概述

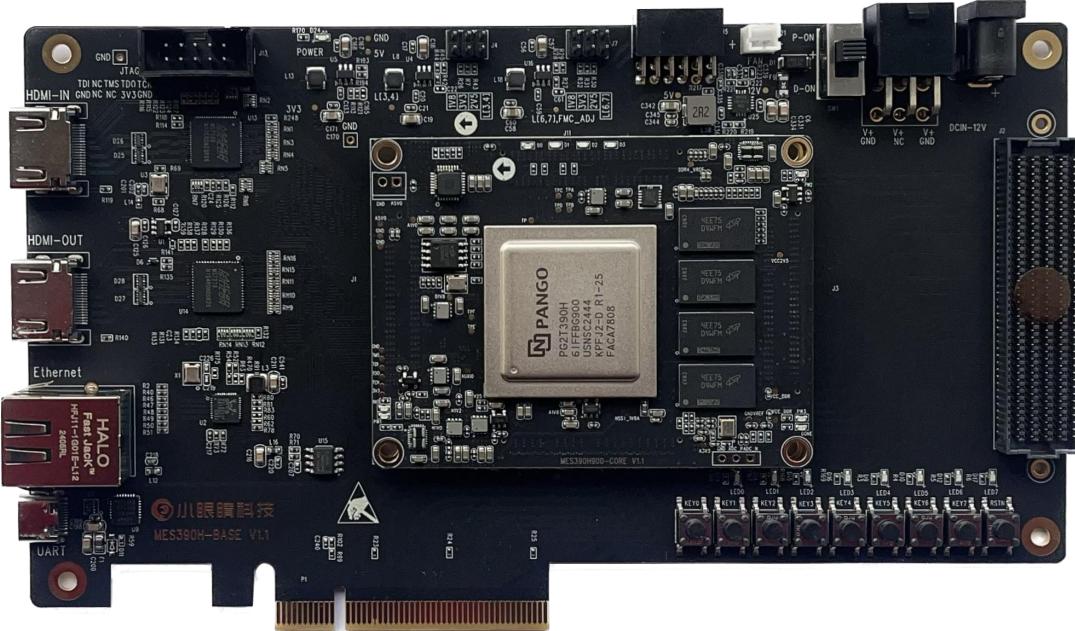

MES2T900-390HP 开发板采用紫光同创 Titan2 系列 FPGA，型号：PG2T390H-6IFFBG900。开发板采用核心板+扩展板结构，核心板与扩展板之间使用高速板对板连接器进行连接，核心板侧连接器型号：LB3524-G120P-WOR，扩展板侧连接器型号：LB3524-G120S-WOR。

核心板主要由 FPGA+4 颗 DDR4+2 颗 FLASH+电源及复位组成，承担了 FPGA 最小系统运行及高速数据处理及存储功能。FPGA 选用紫光同创 28nm 工艺 FPGA (Titan2 : PG2T390H-6IFFBG900) ; PG2T390H 与 DDR4 在数据交互时时钟频率最高可达 1866Mbps, 四颗 DDR4 数据位宽共 64bit, 因此数据带宽可达 (1866Mbps\*64) , 充分满足高速多路数据存储的需求；另外 PG2T390H FPGA 带有 16 路 HSST 高速收发器，每路速度高达 12.5Gbps, 非常适用于光纤通信与 PCIe 通信；核心板上的两颗 FLASH 采用，主要用于存储 FPGA 配置文件。

底板为核心板扩展了丰富的外围接口，其中包括 HDMI 输出接口、HDMI 输入接口、网口、串口，FMC 接口、PCIe 接口，PMOD 接口，并配置了按键、LED 灯、EEPROM 器件。

## 1.2、开发系统简介

### 1.2.1、开发系统外设资源

|            |    |                    |    |

|------------|----|--------------------|----|

| HDMI 输出接口  | *1 | PCIe 接口            | *1 |

| PMOD 接口    | *1 | 10/100/1000M 以太网接口 | *1 |

| 按键         | *8 | Jtag 调试接口          | *1 |

| USB 转 UART | *1 | LED 灯              | *8 |

| HDMI 输入接口  | *1 | FMC 连接器            | *1 |

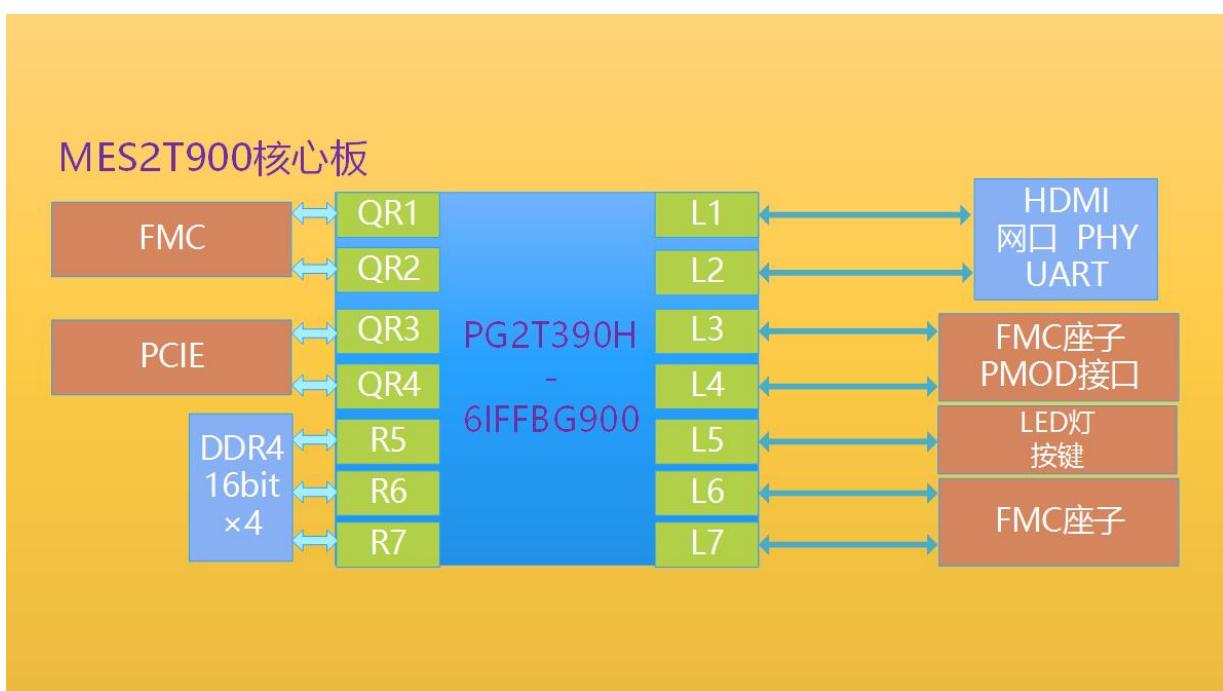

### 1.2.2、开发系统功能框图

综上所述，MES2T900-390HP 开发平台所能实现的功能描述如下所示：

➤ Titan2 FPGA 核心板

由 PG2T390H-6IFFBG900+4 片 512MB DDR4 + 2 片 128Mb QSPI FLASH 组成。

➤ 10/100M/1000M 以太网 RJ-45 接口 \*1

网口 PHY 芯片采用 RTL8211F, RTL8211F 支持 10/100M/1000Mbps 网络传输数据率；支持全双工工作模式及数据率自适应。

➤ PCIe X8 接口 \* 1

支持 PCI Express 2.0 标准，提供 PCIe X8 高速数据传输接口，单通道通信速率可高达 5GBaud。

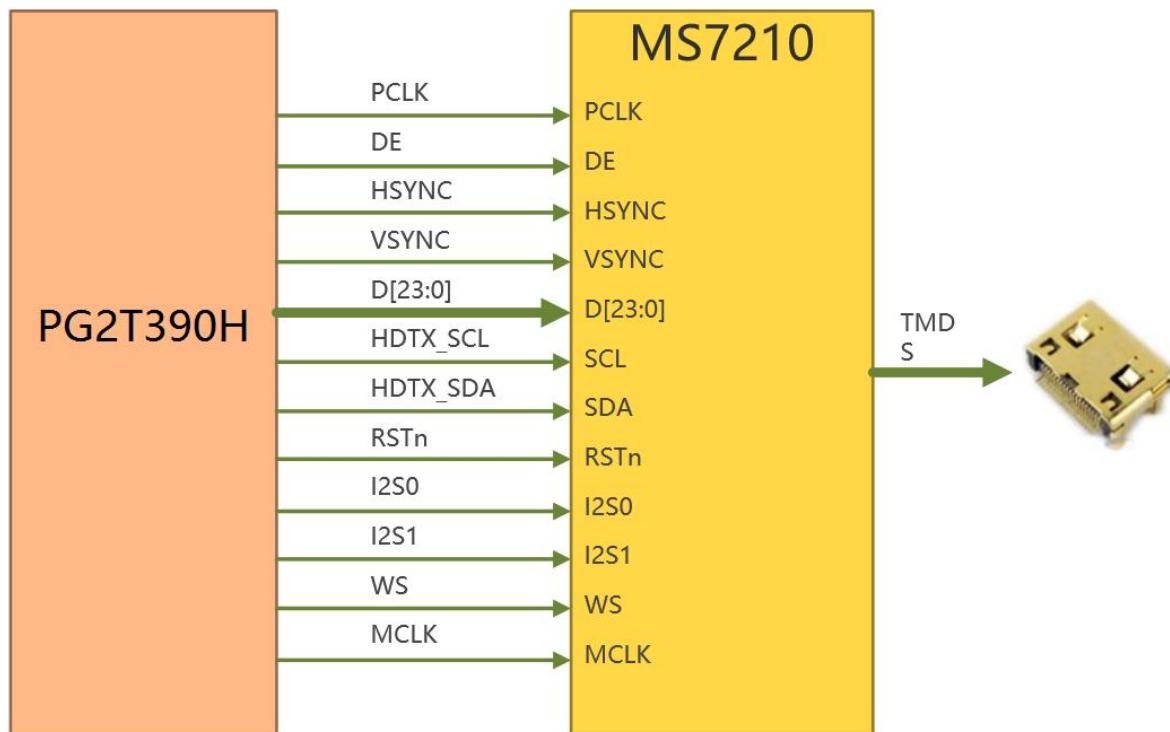

➤ HDMI 输出 \* 1

选用了国产宏晶微公司的 MS7210 HDMI 发送芯片，兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz, 最高采样率达到 300MHz；支持 HBR 音频。

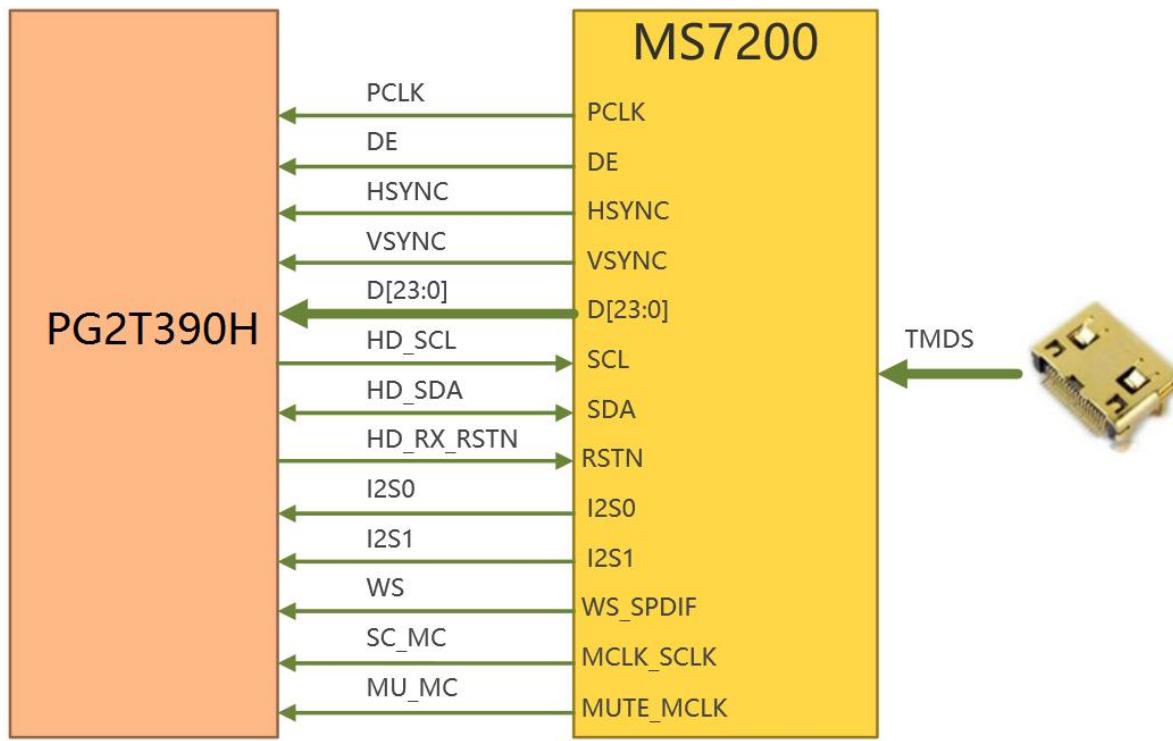

➤ HDMI 输入 \* 1

选用了国产宏晶微公司的 MS7200 HDMI 接收芯片，兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz, 最高采样率达到 300MHz；支持 HBR 音频。

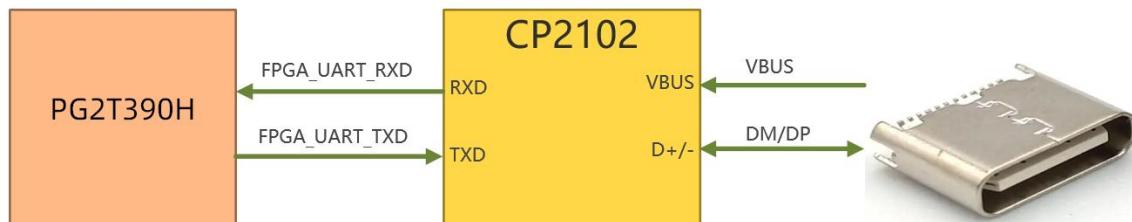

➤ USB 转串口 \* 1

用于与电脑进行串口通信，方便用户进行调试。串口芯片采用 Silicon Labs 的 USB-UART 芯片: CP2102-GMR , USB 接口采用 USB Type C 接口。

➤ PMOD

一个 PMOD 标准接口。

- EEPROM

板载一片 IIC 接口的 EEPROM : AT24C02 ;

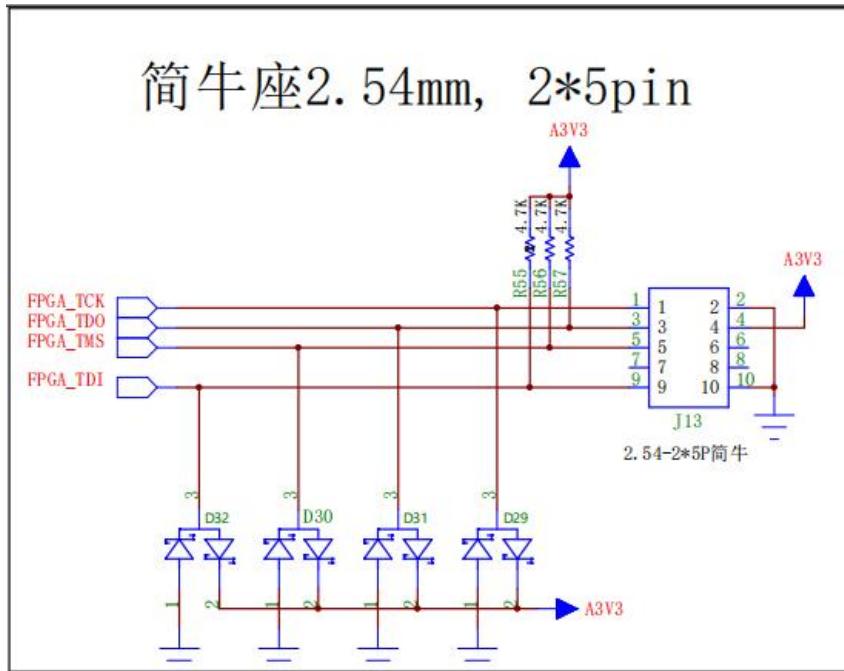

- JTAG 接口

10 针 2.54mm 间距的双排排针口，用于 FPGA 程序的下载和调试。

- LED 灯

8 个用户发光二极管；

- 按键

8 个用户按键，1 个复位按键；

- FMC 扩展口

FMC 扩展口共扩展 84 对差分 IO, 1 路 I2C 总线信号, 8 路 HSSTLP 高速串行数据收发信号以及为 HSSTLP 提供的 2 路参考时钟。

## 2、核心板

### 2.1、核心板概述

MES2T900-390HP 核心板是“小眼睛科技”基于多年 FPGA 开发经验，采用紫光同创 Titan2 系列 PG2T390H-6IFFBG900 作为主控芯片而开发的全新国产高性能 FPGA 核心板，具有高数据带宽、高存储容量的特点，适用于视频图像处理、高速数据采集、工业控制等多元应用场景。

MES2T900-390HP 核心板使用了 4 片 DDR4 芯片，DDR4 总容量 16Gbit，组合数据总线宽度为 64bit，最高速率支持 1866Mbps，满足用户高带宽的数据处理需求。

MES2T900-390HP 核心板扩展出 16 对 HSST TX/RX 信号，用于 PCIe 通信、FMC 接

口通信。在满足用户需求的同时，FPGA 芯片到接口之间走线做了等长和差分处理，非常适合二次开发。

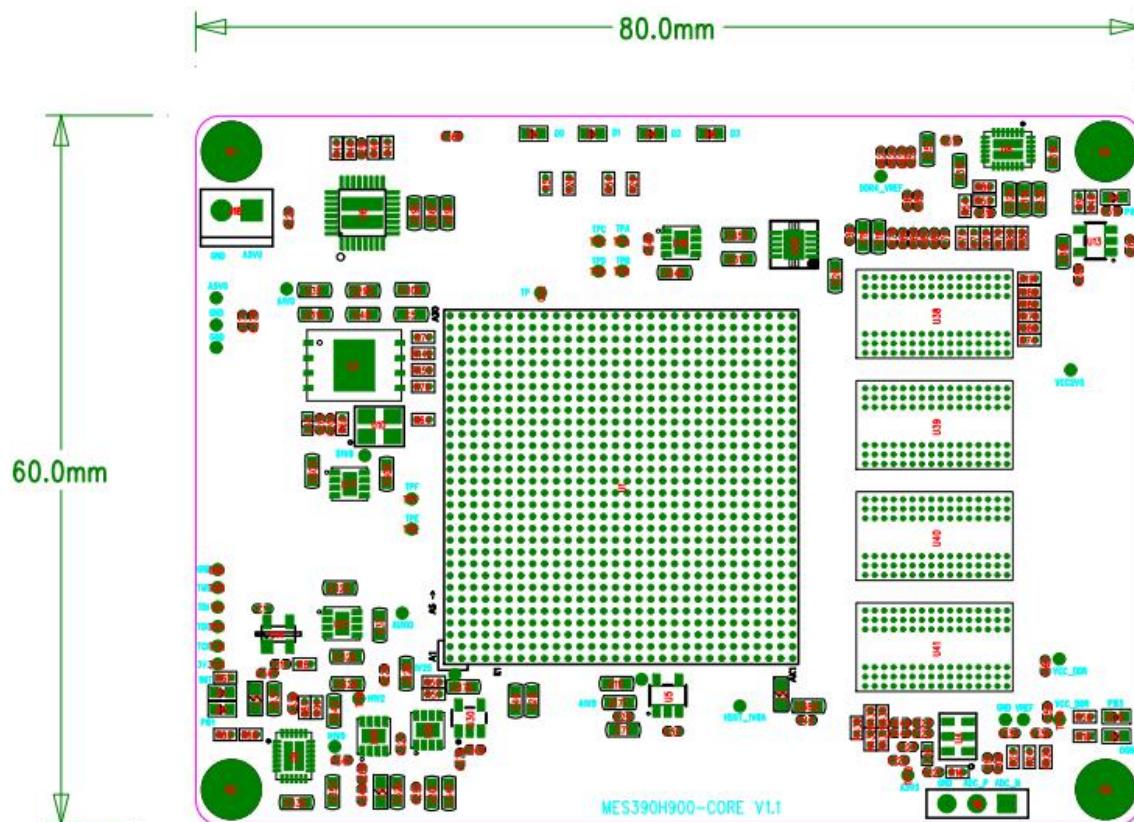

MES2T900-390HP 核心板尺寸结构图如下图所示：

MES2T900-390HP 核心板尺寸结构图

## 2.2、系统描述

### 2.2.1、FPGA

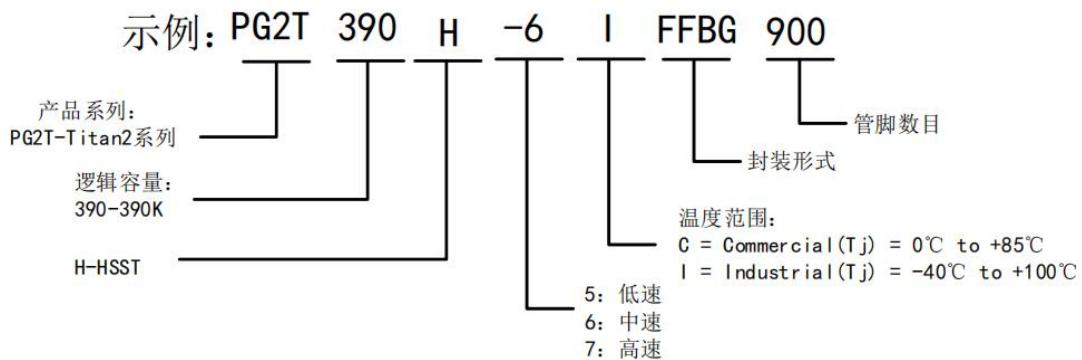

FPGA 的型号为 PG2T390H-6I<sup>L</sup>FBG900，属于紫光同创 Titan2 系列产品，速度等级为 6，温度范围：工业级（-40~100C°），FBB 封装，管脚数目：900

紫光同创 Titan2 系列 FPGA 产品型号的编号内容及意义：

Titan2 系列 FPGA 产品型号的编号内容及意义

PG2T390H-6IFFBG900 主要参数如下表所示：

PG2T390H-6IFFBG900 主要参数

| 资源     |                  | 参数                    |

|--------|------------------|-----------------------|

| 逻辑资源   | 触发器 (FF)         | 487200                |

|        | LUT6             | 243600                |

|        | 等效 LUT4          | 68160                 |

| RAM 资源 | 分布式 RAM (Kbit)   | 4712                  |

|        | 块 RAM 数量 (36K/块) | 480                   |

|        | 块 RAM (Kbit)     | 17280                 |

| 时钟资源   | GPLL             | 10                    |

|        | PPLL             | 10                    |

| 硬核资源   | APM (25*18 乘法器)  | 840                   |

|        | HSST (12.5G)     | 16                    |

|        | PCIE Gen3×8      | 1                     |

| IO 资源  | 用户 IO            | HR_IO(350),HP_IO(150) |

## 2.2.2、电源接口

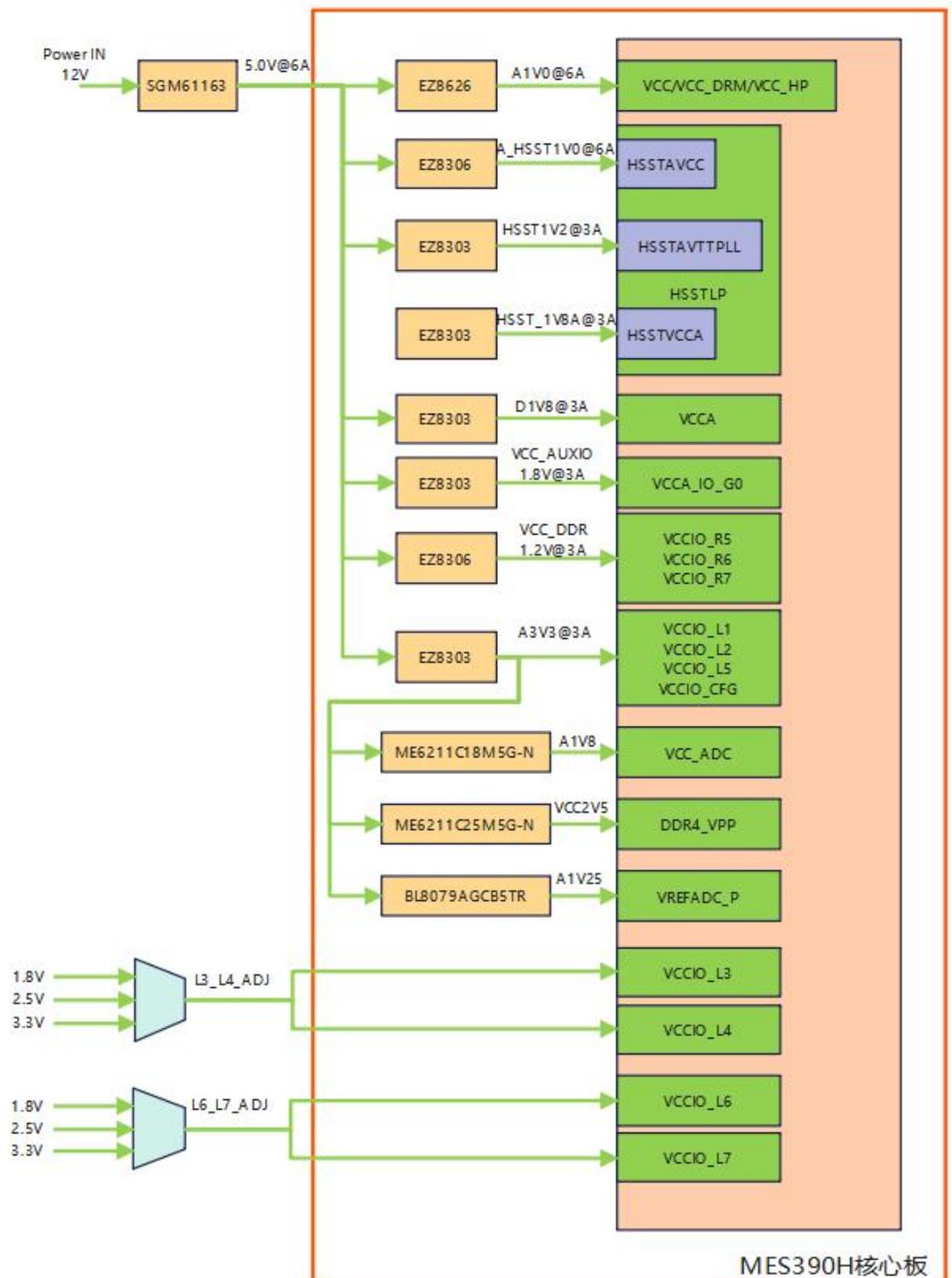

MES2T900-390HP 核心板供电电压为 VCCIN，输入电压为 5V，需通过板对板连接器供电，连接底板时通过底板供电。板上的电源设计示意图如下图所示：

板上的电源设计示意图

各主要电源的功能如下表所示：

| 电源   | 功能用途       |

|------|------------|

| 5.0V | 板对板连接座输入电源 |

|           |                                        |

|-----------|----------------------------------------|

| A1V0      | PG2T390H 内核逻辑电源、DRM 电源、HPIO 区域电源       |

| A_HSST1V0 | PG2T390H HSST 收发器内核电源                  |

| A_HSST1V0 | PG2T390H HSST 锁相环电源                    |

| HSST_1V8A | PG2T390H HSST 辅助电源                     |

| VCC_DDR   | DDR4 供电电压及 Bank R5、Bank R6、Bank R7 电源； |

| D1V8      | VCCA 辅助电源                              |

| A1V8      | VCCADC 电源                              |

| VCC2V5    | DDR4 VPP 电源                            |

| A1V25     | VREFADC_P 电源                           |

## 2.2.3、时钟

MES2T900-390HP 核心板上配有 1 个有源差分晶振，1 个单端 27MHz 晶振，1 个单端 50MHz 晶振。差分晶振用于 DDR4 的参考时钟输入，单端晶振用于 FPGA 的系统时钟源。

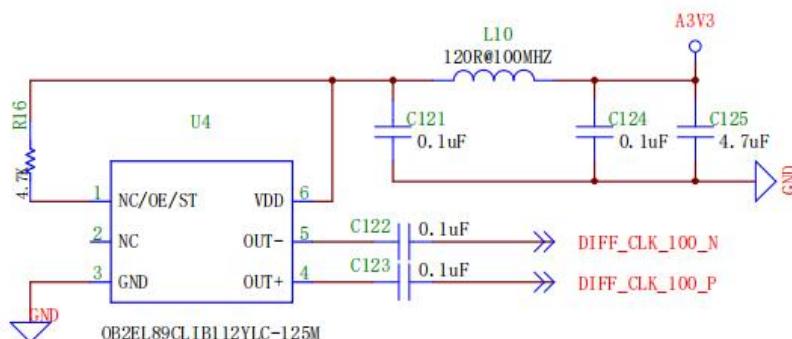

### 2.2.3.1、125MHz 差分晶振

下图中 U4 为 125MHz 有源差分晶振，此时钟为 DDR4 提供输入参考时钟，晶振输出到 FPGA DDR4 信号所在 BANK 上。

核心板 125MHz 有源差分晶振

具体的管脚约束如下表所示：

| 信号             | 描述        | PG2T390H-900 管脚 |

|----------------|-----------|-----------------|

| GCLK_DDR_100_P | DDR4 参考时钟 | AD12            |

| GCLK_DDR_100_N |           | AD11            |

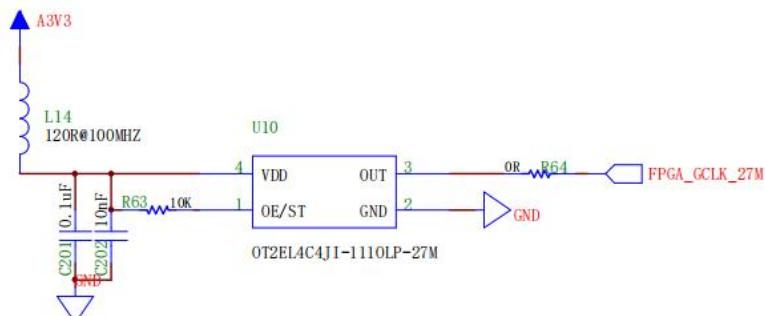

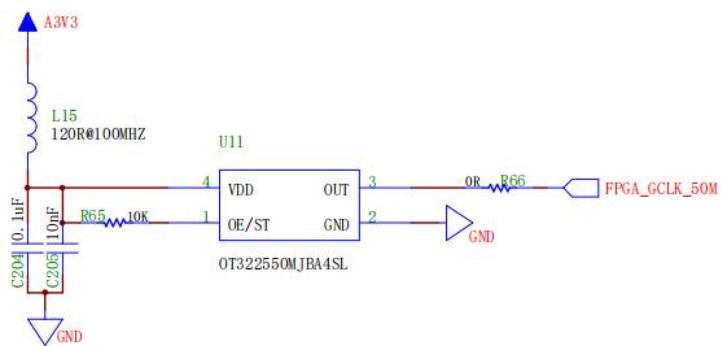

### 2.2.3.2、单端时钟

下图 U10 为 27MHz 有源晶振电路，U11 为 50MHz 有源晶振电路，此时中连接至 FPGA 内部的全局时钟管脚上，可为 FPGA 提供输入参考时钟。

核心板 27MHz 有源晶振电路

核心板 50MHz 有源晶振电路

具体的管脚约束如下表所示：

| 信号            | 描述          | PG2T390H-900 管脚 |

|---------------|-------------|-----------------|

| FPGA_GCLK_27M | FPGA 输入参考时钟 | F20             |

| FPGA_GCLK_50M | FPGA 输入参考时钟 | T26             |

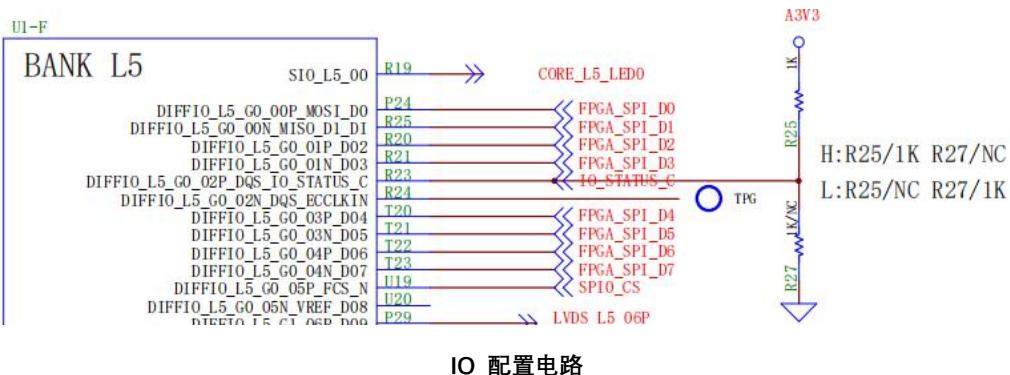

## 2.2.4、上电 IO Status

在 Titan2 器件上有一个功能复用 IO，控制从上电完成后到进入用户模式之前中所有用户 IO 的弱上拉电阻是否使能。此管脚在配置之前或是配置过程中，该引脚不允许悬空，此 IO 在上电后的对应功能如下：

- (1) “0”，使能所有用户 IO 内部上拉电阻。

- (2) “1”，不使能所有用户 IO 内部上拉电阻。

MES2T900-390HP 核心板将此管脚的功能默认接 A3V3，用户可根据需求，自行焊接电阻选择上电后初始的 IO 状态；

功能电路如下：

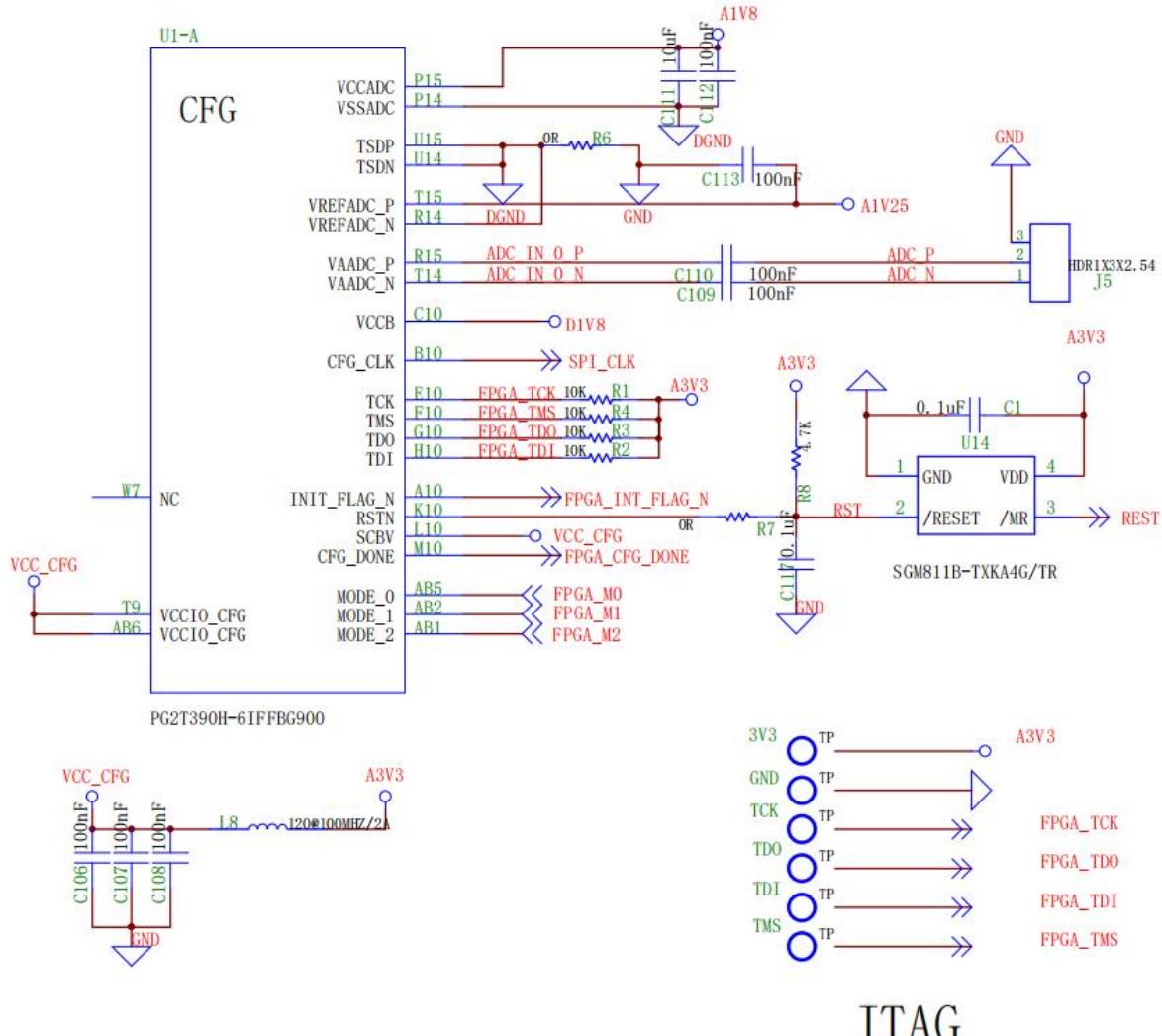

## 2.2.5、JTAG 接口

MES2T900-390HP 核心板正面左上角预留 JTAG 触点，可在没有底板的情况下调试核心板。FPGA 的 JTAG 信号通过高速板对板连接器与底板 JTAG 接口相连，用于下载

FPGA 程序或者固化程序到 FLASH。

JTAG 接口电路

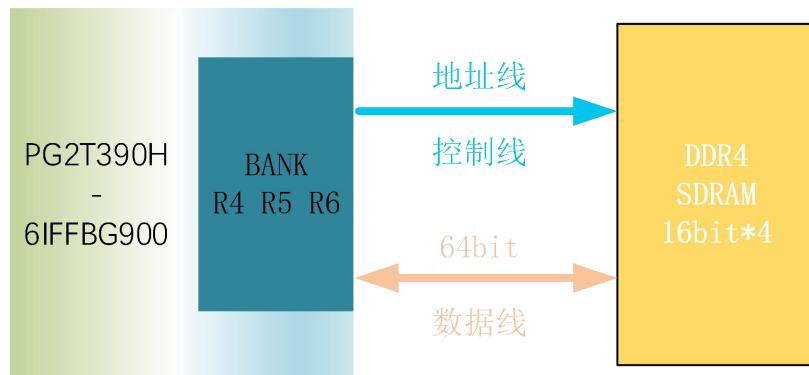

## 2.2.6、DDR4

MES2T900-390HP 核心板配了 4 个 8Gbit (512MB) 的 DDR4 芯片 (共计 32Gbit) ,

DDR 的总线数据宽度共 64bit, DDR4 型号选择为 Micron 公司 MT40A512M16LY-062EIT:E。

DDR4 SDRAM 的最高数据速率可达 1866Mbps。该 DDR4 存储系统直接连接到了 FPGA 的 R5、R6, R7, DDR4 SDRAM 的硬件连接示意图如下图所示：

DDR4 SDRAM 的硬件连接示意图

具体的管脚分配如下表所示：

| 信号名称          | PG2T390H-900 管脚 | 信号名称         | PG2T390H-900 管脚 |

|---------------|-----------------|--------------|-----------------|

| ddr4_addr[0]  | AH11            | ddr4_ba[0]   | AD9             |

| ddr4_addr[1]  | AA12            | ddr4_ba[1]   | AB12            |

| ddr4_addr[2]  | AB9             | ddr4_ba[2]   | AD8             |

| ddr4_addr[3]  | AC12            | ddr4_ck_n    | AF11            |

| ddr4_addr[4]  | AF10            | ddr4_ck_p    | AE11            |

| ddr4_addr[5]  | AA10            | ddr4_cke     | AJ9             |

| ddr4_addr[6]  | AB8             | ddr4_act_b   | AH9             |

| ddr4_addr[7]  | AA11            | ddr4_alert_1 | AK14            |

| ddr4_addr[8]  | AC9             | ddr4_alert_2 | AK11            |

| ddr4_addr[9]  | Y11             | ddr4_alert_3 | AK10            |

| ddr4_addr[10] | AE8             | ddr4_alert_4 | AK9             |

| ddr4_addr[11] | AA8             | ddr4_par     | Y10             |

| ddr4_addr[12] | AC10            | ddr4_reset_b | AK13            |

| ddr4_addr[13] | AA13            | ddr4_odt     | AG9             |

|               |      |  |             |      |

|---------------|------|--|-------------|------|

| ddr4_addr[14] | AE9  |  | ddr4_cs_b   | AE10 |

| ddr4_addr[15] | AB10 |  |             |      |

| ddr4_addr[16] | AC11 |  |             |      |

|               |      |  |             |      |

| ddr4_dm[0]    | AF15 |  | ddr4_dm[4]  | AC4  |

| ddr4_dm[1]    | AF17 |  | ddr4_dm[5]  | AE1  |

| ddr4_dm[2]    | AB18 |  | ddr4_dm[6]  | AJ2  |

| ddr4_dm[3]    | AB15 |  | ddr4_dm[7]  | AK4  |

| ddr4_dq[0]    | AG15 |  | ddr4_dq[32] | AC2  |

| ddr4_dq[1]    | AE16 |  | ddr4_dq[33] | AC5  |

| ddr4_dq[2]    | AK15 |  | ddr4_dq[34] | AD3  |

| ddr4_dq[3]    | AJ17 |  | ddr4_dq[35] | AE6  |

| ddr4_dq[4]    | AG14 |  | ddr4_dq[36] | AC1  |

| ddr4_dq[5]    | AH17 |  | ddr4_dq[37] | AD6  |

| ddr4_dq[6]    | AH15 |  | ddr4_dq[38] | AD4  |

| ddr4_dq[7]    | AK16 |  | ddr4_dq[39] | AC7  |

| ddr4_dq[8]    | AE19 |  | ddr4_dq[40] | AF1  |

| ddr4_dq[9]    | AJ19 |  | ddr4_dq[41] | AF6  |

| ddr4_dq[10]   | AG18 |  | ddr4_dq[42] | AF2  |

| ddr4_dq[11]   | AH19 |  | ddr4_dq[43] | AE4  |

| ddr4_dq[12]   | AF18 |  | ddr4_dq[44] | AE3  |

| ddr4_dq[13]   | AG19 |  | ddr4_dq[45] | AE5  |

|               |      |               |      |

|---------------|------|---------------|------|

| ddr4_dq[14]   | AG17 | ddr4_dq[46]   | AF3  |

| ddr4_dq[15]   | AK19 | ddr4_dq[47]   | AF5  |

| ddr4_dq[16]   | AC17 | ddr4_dq[48]   | AJ3  |

| ddr4_dq[17]   | AC19 | ddr4_dq[49]   | AJ4  |

| ddr4_dq[18]   | AD17 | ddr4_dq[50]   | AK1  |

| ddr4_dq[19]   | AD18 | ddr4_dq[51]   | AH4  |

| ddr4_dq[20]   | AB17 | ddr4_dq[52]   | AH2  |

| ddr4_dq[21]   | AB19 | ddr4_dq[53]   | AH5  |

| ddr4_dq[22]   | AD16 | ddr4_dq[54]   | AJ1  |

| ddr4_dq[23]   | AE18 | ddr4_dq[55]   | AH6  |

| ddr4_dq[24]   | AA15 | ddr4_dq[56]   | AG7  |

| ddr4_dq[25]   | AA17 | ddr4_dq[57]   | AJ8  |

| ddr4_dq[26]   | AE15 | ddr4_dq[58]   | AK5  |

| ddr4_dq[27]   | AA16 | ddr4_dq[59]   | AK8  |

| ddr4_dq[28]   | AC14 | ddr4_dq[60]   | AF7  |

| ddr4_dq[29]   | Y16  | ddr4_dq[61]   | AF8  |

| ddr4_dq[30]   | AD14 | ddr4_dq[62]   | AJ6  |

| ddr4_dq[31]   | Y15  | ddr4_dq[63]   | AK6  |

| ddr4_dqs_p[0] | AH16 | ddr4_dqs_n[0] | AJ16 |

| ddr4_dqs_p[1] | AJ18 | ddr4_dqs_n[1] | AK18 |

| ddr4_dqs_P[2] | Y19  | ddr4_dqs_n[2] | Y18  |

|               |      |               |      |

|---------------|------|---------------|------|

| ddr4_dqs_P[3] | AC16 | ddr4_dqs_n[3] | AC15 |

| ddr4_dqs_p[4] | AD2  | ddr4_dqs_n[4] | AD1  |

| ddr4_dqs_p[5] | AG4  | ddr4_dqs_n[5] | AG3  |

| ddr4_dqs_p[6] | AG2  | ddr4_dqs_n[6] | AH1  |

| ddr4_dqs_p[7] | AH7  | ddr4_dqs_n[7] | AJ7  |

| ddr4_ck_p     | AE11 | ddr4_ck_n     | AF11 |

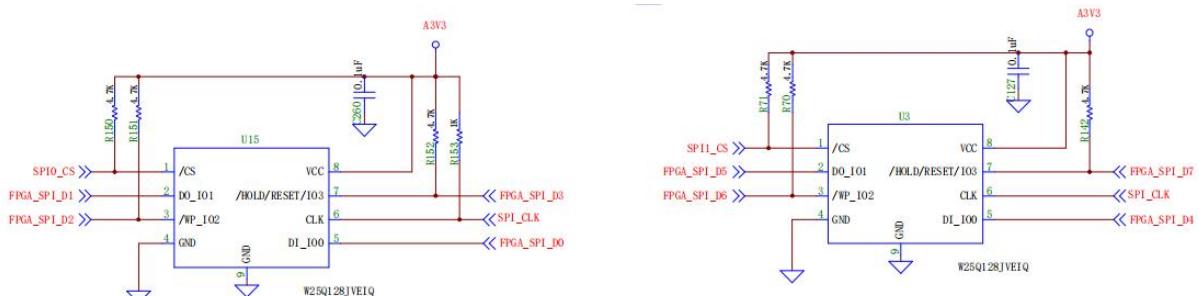

## 2.2.7、QSPI Flash

MES2T900-390HP 核心板采用两片 winbond 公司的 4 位 SPI (QSPI) 串行 Nor 闪存 W25Q128JVETIQ 或者 XT25BF128FSSIGU-W，容量共 256Mb，最高支持 8bit 模式。

两颗 QSPI FLASH (U15、U3) 的电路连接如下：

QSPI FLASH 电路

QSPI Flash 管脚分配如下：

| 信号          | 描述        | PG2T390H-900 管脚 |

|-------------|-----------|-----------------|

| SPI_CLK     | 串行数据时钟    | B10             |

| SPI0_CS     | U15 片选    | U19             |

| FPGA_SPI_D0 | U15 数据位 0 | P24             |

| FPGA_SPI_D1 | U15 数据位 1 | R25             |

| FPGA_SPI_D2 | U15 数据位 2 | R20             |

|             |           |     |

|-------------|-----------|-----|

| FPGA_SPI_D3 | U15 数据位 3 | R21 |

| SPI1_CS     | U3 片选     | M25 |

| FPGA_SPI_D4 | U3 数据位 4  | T20 |

| FPGA_SPI_D5 | U3 数据位 5  | T21 |

| FPGA_SPI_D6 | U3 数据位 6  | T22 |

| FPGA_SPI_D7 | U3 数据位 7  | T23 |

## 2.2.8、扩展 IO

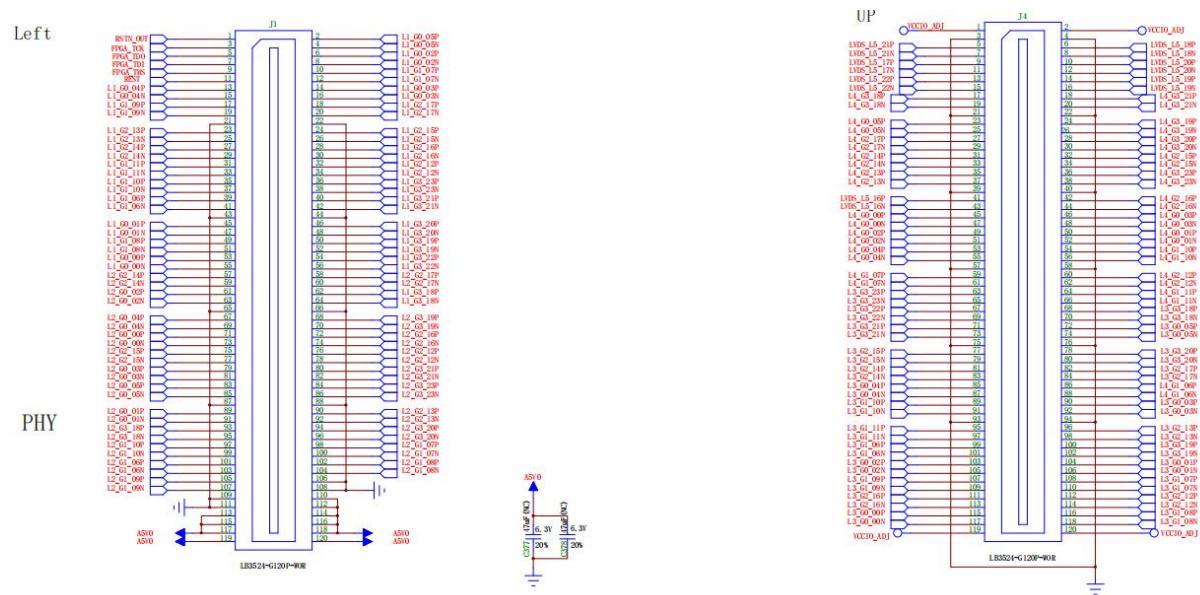

MES2T900-390HP 核心板背面共有 4 个 120pin 高速扩展口 J1/J2/J3/J4，核心板侧

连接器型号：LB3524-G120P-WOR，扩展板侧连接器型号：LB3524-G120S-WOR。,

FPGA 的 IO 通过 4 个扩展口与底板连接，实现高速数据通信。

扩展口 IO

Right

### 3、扩展底板

### 3.1、扩展底板简介

通过前面开发系统的介绍可知，扩展底板的外设资源如下：

|                    |    |            |    |

|--------------------|----|------------|----|

| HDMI 输出接口          | *1 | 按键         | *8 |

| PMOD 接口            | *1 | USB 转 UART | *1 |

| HDMI 输入接口          | *1 | Jtag 调试接口  | *1 |

| 10/100/1000M 以太网接口 | *1 | LED 灯      | *8 |

| PCIe 接口            | *1 | FMC 连接器    | *1 |

## 3.2、外接接口通信

### 3.2.1、网口

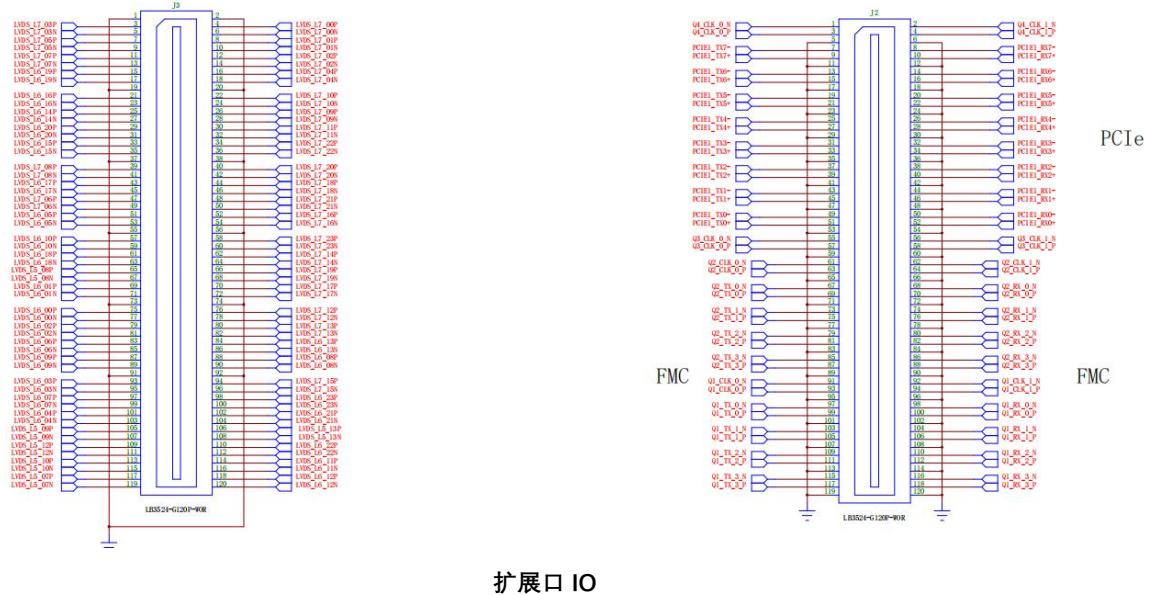

MES2T900-390HP 开发板使用 Realtek RTL8211F PHY 实现了一个 10/100/1000 以太网端口，用于网络连接。该器件工作电压为支持 2.5V、3.3V。PHY 连接到 BANK L3，并通过 RGMII 接口连接到 MES2T900-390HP。RJ-45 连接器是 HFJ11-1G01E-L12RL，具有集成的自动缠绕磁性元件，可提高性能、质量和可靠性。RJ-45 有两个状态指示灯 LED，用于指示流量和有效链路状态。

下图为 MES2T900-390HP 开发板上的网口连接框图。

网口连接框图

具体的管脚分配如下所示：

| 信号名称       | 描述    | PG2T390H-900 管脚 | RTL8211 Pin |

|------------|-------|-----------------|-------------|

| PHY0_RXC   | 接收时钟线 | D12             | 27          |

| PHY0_RXCTL | 接收控制线 | B14             | 26          |

|              |            |     |    |

|--------------|------------|-----|----|

| PHY0_RXD[3]  | 接收数据线 3    | E11 | 22 |

| PHY0_RXD[2]  | 接收数据线 2    | A11 | 23 |

| PHY0_RXD[1]  | 接收数据线 1    | A12 | 24 |

| PHY0_RXD[0]  | 接收数据线 0    | D13 | 25 |

| PHY0_TXC     | 发送时钟线      | F11 | 20 |

| PHY0_TXCTL   | 发送控制线      | C11 | 19 |

| PHY0_TXD[3]  | 发送数据线 3    | J12 | 15 |

| PHY0_TXD[2]  | 发送数据线 2    | K13 | 16 |

| PHY0_TXD[1]  | 发送数据线 1    | J13 | 17 |

| PHY0_TXD[0]  | 发送数据线 0    | D11 | 18 |

| PHY0_MDC     | 控制总线时钟     | L13 | 13 |

| PHY0_MDIO    | 控制总线数据     | J11 | 14 |

| PHY_RSTN_OUT | 复位控制线, 低有效 | L12 | 12 |

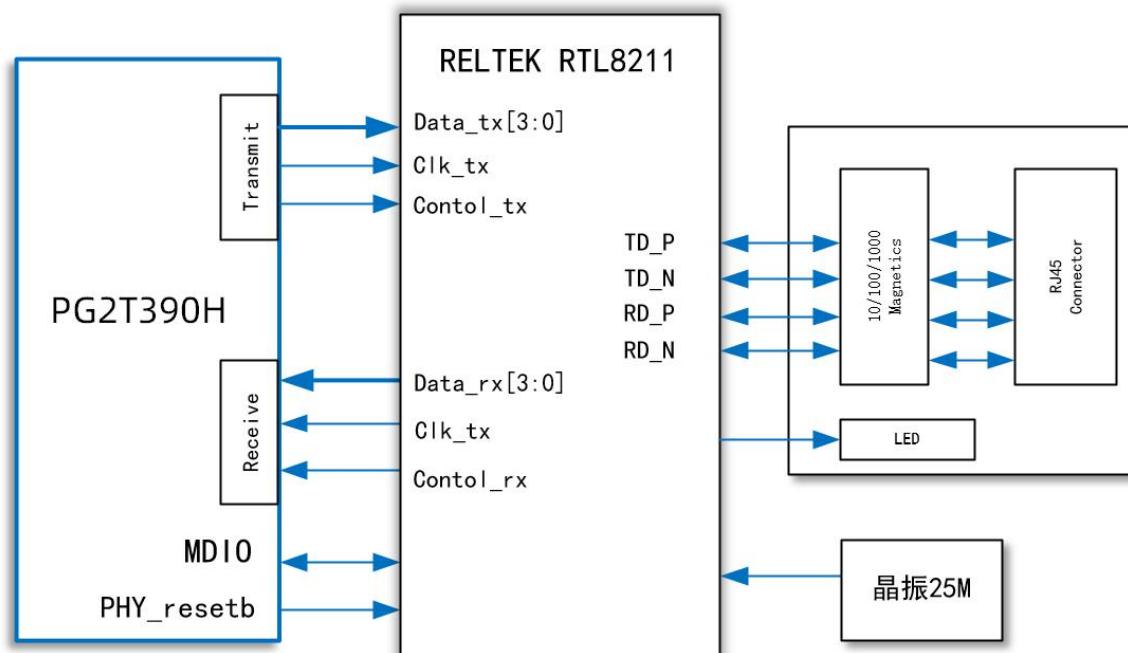

### 3.2.4、PCIe x8 接口

MES2T900-390HP 扩展底板上提供一个工业级高速数据传输 PCIe x8 接口，PCIE 卡的外形尺寸符合标准 PCIe 卡电气规范要求, 可直接在普通 PC 的 x8 PCIe 插槽上使用。

PCIe 接口的收发信号直接跟 FPGA 的 HSST 收发器相连接, 四通道的 TX 信号和 RX 信号都是以差分信号方式连接到 FPGA, Max Link Speed 可高达 8GT/s。PCIe 的参考时钟由 PC 的 PCIe 插槽提供给开发板, 参考时钟频率为 100Mhz。

TX 发送信号和参考时钟 CLK 信号用 AC 耦合模式连接。

PCIe 设计示意图

MES2T900-390HP 与 PCIe 卡槽的管脚连接如下表所示。

| 信号名称      | 描述                 | PG2T390H-900 管脚 |

|-----------|--------------------|-----------------|

| PCIE_TX0P | PCIe 通道 0 数据发送 P 端 | L4              |

| PCIE_TX0N | PCIe 通道 0 数据发送 N 端 | L3              |

| PCIE_RX0P | PCIe 通道 0 数据接收 P 端 | M6              |

| PCIE_RX0N | PCIe 通道 0 数据接收 N 端 | M5              |

| PCIE_TX1P | PCIe 通道 1 数据发送 P 端 | M2              |

| PCIE_TX1N | PCIe 通道 1 数据发送 N 端 | M1              |

| PCIE_RX1P | PCIe 通道 1 数据接收 P 端 | P6              |

| PCIE_RX1N | PCIe 通道 1 数据接收 N 端 | P5              |

| PCIE_TX2P | PCIe 通道 2 数据发送 P 端 | N4              |

| PCIE_TX2N | PCIe 通道 2 数据发送 N 端 | N3              |

| PCIE_RX2P | PCIe 通道 2 数据接收 P 端 | R4              |

| PCIE_RX2N | PCIe 通道 2 数据接收 N 端 | R3              |

|            |                    |     |

|------------|--------------------|-----|

| PCIE_TX3P  | PCIe 通道 3 数据发送 P 端 | P2  |

| PCIE_TX3N  | PCIe 通道 3 数据发送 N 端 | P1  |

| PCIE_RX3P  | PCIe 通道 3 数据接收 P 端 | T6  |

| PCIE_RX3N  | PCIe 通道 3 数据接收 N 端 | T5  |

| PCIE_TX4P  | PCIe 通道 4 数据发送 P 端 | T2  |

| PCIE_TX4N  | PCIe 通道 4 数据发送 N 端 | T1  |

| PCIE_RX4P  | PCIe 通道 4 数据接收 P 端 | V6  |

| PCIE_RX4N  | PCIe 通道 4 数据接收 N 端 | V5  |

| PCIE_TX5P  | PCIe 通道 5 数据发送 P 端 | U4  |

| PCIE_TX5N  | PCIe 通道 5 数据发送 N 端 | U3  |

| PCIE_RX5P  | PCIe 通道 5 数据接收 P 端 | W4  |

| PCIE_RX5N  | PCIe 通道 5 数据接收 N 端 | W3  |

| PCIE_TX6P  | PCIe 通道 6 数据发送 P 端 | V2  |

| PCIE_TX6N  | PCIe 通道 6 数据发送 N 端 | V1  |

| PCIE_RX6P  | PCIe 通道 6 数据接收 P 端 | Y6  |

| PCIE_RX6N  | PCIe 通道 6 数据接收 N 端 | Y5  |

| PCIE_TX7P  | PCIe 通道 7 数据发送 P 端 | Y2  |

| PCIE_TX7N  | PCIe 通道 7 数据发送 N 端 | Y1  |

| PCIE_RX7P  | PCIe 通道 7 数据接收 P 端 | AA4 |

| PCIE_RX7N  | PCIe 通道 7 数据接收 N 端 | AA3 |

| PCIE_PERST | PCIe 的复位引脚         | L17 |

| PCIE_WAKE  | PCIe 的唤醒引脚         | L18 |

| PCIE_CLKP  | PCIe 的参考时钟 P 端     | L8  |

| PCIE_CLKN  | PCIe 的参考时钟 N 端     | L7  |

### 3.2.5、串口

MES2T900-390HP 扩展底板上集成了一路 USB 转串口模块，采用的 USB-UART 芯

片是 CP2102，USB 接口采用 USB Type C 接口，可用 USB Type C 线连接到 PC 端进行串口数据通信。

USB Uart 电路设计的示意图如下图所示：

具体的管脚分配如下：

| 信号            | 描述        | PG2T390H-900 管脚 |

|---------------|-----------|-----------------|

| FPGA_UART_RXD | UART 数据输入 | K11             |

| FPGA_UART_TXD | UART 数据输出 | L11             |

### 3.2.6、JTAG

MES2T900-390HP 扩展底板上的 JTAG 接口用于下载 FPGA 程序或者固化程序到 FLASH。为了减轻带电插拔造成对 FPGA 芯片的损坏，在设计上在 JTAG 信号位置添加了保护二极管来保证信号的电压在 FPGA 接受的范围，避免 FPGA 的损坏。

**提醒：通电的情况下，应避免插拔 JTAG 接口！**

JTAG 连接座原理图

### 3.3、HDMI

#### 3.3.1、HDMI 输入接口

HDMI 输入接口的实现，选用了国产宏晶微公司的 MS7200 HDMI 接收芯片，兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz，最高采样率达到 300MHz；MS7200 支持 YUV 和 RGB 之间的色彩空间转换，数字接口支持 YUV 及 RGB 格式输出。MS7200 不仅支持通过 IIS 总线或 SPDIF 传输高清音频，还支持高比特音频(HBR)音频，在 HBR 模式下，音频采样率最高为 768KHz。其中 MS7200 的 IIC 配置接口与 FPGA 的 IO 相连，通过 FPGA 的编程来对 MS7200 进行初始化和控制操作，MES2T900-390HP 开发板上将 MS7200 的 SA 管脚下拉到地，故 IIC 的 ID 地址为 0x56；HDMI 输入接口的硬件连接如下图所示。

HDMI 输入接口的硬件连接

具体的管脚分配如下所示：

| 信号         | 功能描述               | PG2T390H-900 管脚 |

|------------|--------------------|-----------------|

| HD_RX_PCLK | HDMI 显示图像像素时钟      | D17             |

| HD_RX_VS   | HDMI 显示图像帧同步信号     | G22             |

| HD_RX_HS   | HDMI 显示图像行同步信号     | C21             |

| HD_RX_DE   | HDMI 显示图像有效像素点使能信号 | D21             |

| HD_RX_D0   | HDMI 显示图像像素点数据位[0] | A21             |

| HD_RX_D1   | HDMI 显示图像像素点数据位[1] | A20             |

| HD_RX_D2   | HDMI 显示图像像素点数据位[2] | D19             |

| HD_RX_D3   | HDMI 显示图像像素点数据位[3] | E19             |

| HD_RX_D4   | HDMI 显示图像像素点数据位[4] | B19             |

| HD_RX_D5   | HDMI 显示图像像素点数据位[5] | C19             |

| HD_RX_D6   | HDMI 显示图像像素点数据位[6] | A18             |

| HD_RX_D7   | HDMI 显示图像像素点数据位[7] | B18             |

|             |                                 |     |

|-------------|---------------------------------|-----|

| HD_RX_D8    | HDMI 显示图像像素点数据位[8]              | D18 |

| HD_RX_D9    | HDMI 显示图像像素点数据位[9]              | B17 |

| HD_RX_D10   | HDMI 显示图像像素点数据位[10]             | C17 |

| HD_RX_D11   | HDMI 显示图像像素点数据位[11]             | A17 |

| HD_RX_D12   | HDMI 显示图像像素点数据位[12]             | A16 |

| HD_RX_D13   | HDMI 显示图像像素点数据位[13]             | F17 |

| HD_RX_D14   | HDMI 显示图像像素点数据位[14]             | G17 |

| HD_RX_D15   | HDMI 显示图像像素点数据位[15]             | C22 |

| HD_RX_D16   | HDMI 显示图像像素点数据位[16]             | D22 |

| HD_RX_D17   | HDMI 显示图像像素点数据位[17]             | H22 |

| HD_RX_D18   | HDMI 显示图像像素点数据位[18]             | H21 |

| HD_RX_D19   | HDMI 显示图像像素点数据位[19]             | E21 |

| HD_RX_D20   | HDMI 显示图像像素点数据位[20]             | F21 |

| HD_RX_D21   | HDMI 显示图像像素点数据位[21]             | B20 |

| HD_RX_D22   | HDMI 显示图像像素点数据位[22]             | C20 |

| HD_RX_D23   | HDMI 显示图像像素点数据位[23]             | G20 |

| HD_RX_SC_MC | MS7200 音频通道 I2S 的串行时钟信号         | K20 |

| HD_RX_MU_MC | MS7200 音频通道 I2S 的主时钟信号或 Mute 信号 | J19 |

| HD_RX_I2S1  | MS7200 音频通道 I2S 的数据通道 1         | K19 |

| HD_RX_I2S0  | MS7200 音频通道 I2S 的数据通道 0         | H19 |

| HD_RX_WS_SP | MS7200 音频通道 I2S 的位时钟            | H20 |

| HD_RX_INT   | MS7200 输出中断信号                   | F22 |

| HD_SCL      | MS7200 、 MS7210 控制通道 IIC 的时钟信号  | J17 |

| HD_SDA      | MS7200 、 MS7210 控制通道 IIC 的数据信号  | H17 |

| RSTN_OUT    | MS7200 、 MS7210 硬件复位信号，低电平有效    | E20 |

### 3.3.2、HDMI 输出接口

HDMI 输出接口的实现，选用了国产宏晶微公司的 MS7210 HDMI 发送芯片，兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。内置可编程 EDID 缓存，支持的最高分辨率高达 4K@30Hz，最高采样率达到 300MHz；MS7210 支持 YUV 和 RGB 之间的色彩空间转换，数字接口支持 YUV 及 RGB 格式输入；MS7210 的 IIS 接口不仅支持高清音频的传输，还支持高比特音频（HBR）音频，在 HBR 模式下，音频采样率最高为 768KHz。其中，MS7210 的 IIC 配置接口与 FPGA 的 IO 相连，通过 FPGA 的编程来对 MS7210 进行初始化和控制操作，MES2T900-390HP 开发板将 MS7210 的 SA 管脚上拉到电源电压，故 IIC 的 ID 地址为 0xB2；HDMI 输出接口的硬件连接如下图所示。

HDMI 输出接口的硬件连接

具体的管脚分配如下表所示：

| 信号         | 功能描述                | PG2T390H-900 管脚 |

|------------|---------------------|-----------------|

| HD_TX_PCLK | HDMI 显示图像像素时钟       | K15             |

| HD_TX_VS   | HDMI 显示图像帧同步信号      | C15             |

| HD_TX_HS   | HDMI 显示图像行同步信号      | E15             |

| HD_TX_DE   | HDMI 显示图像有效像素点使能信号  | E14             |

| HD_TX_D0   | HDMI 显示图像像素点数据位[0]  | C14             |

| HD_TX_D1   | HDMI 显示图像像素点数据位[1]  | D14             |

| HD_TX_D2   | HDMI 显示图像像素点数据位[2]  | A13             |

| HD_TX_D3   | HDMI 显示图像像素点数据位[3]  | B13             |

| HD_TX_D4   | HDMI 显示图像像素点数据位[4]  | A15             |

| HD_TX_D5   | HDMI 显示图像像素点数据位[5]  | K16             |

| HD_TX_D6   | HDMI 显示图像像素点数据位[6]  | L16             |

| HD_TX_D7   | HDMI 显示图像像素点数据位[7]  | H16             |

| HD_TX_D8   | HDMI 显示图像像素点数据位[8]  | J16             |

| HD_TX_D9   | HDMI 显示图像像素点数据位[9]  | L15             |

| HD_TX_D10  | HDMI 显示图像像素点数据位[10] | G15             |

| HD_TX_D11  | HDMI 显示图像像素点数据位[11] | H15             |

| HD_TX_D12  | HDMI 显示图像像素点数据位[12] | G14             |

| HD_TX_D13  | HDMI 显示图像像素点数据位[13] | H14             |

| HD_TX_D14  | HDMI 显示图像像素点数据位[14] | F13             |

| HD_TX_D15  | HDMI 显示图像像素点数据位[15] | G13             |

| HD_TX_D16  | HDMI 显示图像像素点数据位[16] | B12             |

| HD_TX_D17  | HDMI 显示图像像素点数据位[17] | C12             |

| HD_TX_D18  | HDMI 显示图像像素点数据位[18] | E13             |

| HD_TX_D19  | HDMI 显示图像像素点数据位[19] | F12             |

| HD_TX_D20  | HDMI 显示图像像素点数据位[20] | H12             |

| HD_TX_D21  | HDMI 显示图像像素点数据位[21] | H11             |

| HD_TX_D22  | HDMI 显示图像像素点数据位[22] | J14             |

|             |                              |     |

|-------------|------------------------------|-----|

| HD_TX_D23   | HDMI 显示图像像素点数据位[23]          | K14 |

| HD_TX_SC_MC | MS7210 音频通道 I2S 的时钟信号        | E16 |

| HD_TX_I2S1  | MS7210 音频通道 I2S 的数据通道 1      | B15 |

| HD_TX_I2S0  | MS7210 音频通道 I2S 的数据通道 0      | F15 |

| HD_TX_WS    | MS7210 音频通道 I2S 的位时钟         | D16 |

| HD_TX_INT   | MS7210 输出中断                  | C16 |

| HD_SCL      | MS7200、MS7210 控制通道 IIC 的时钟信号 | J17 |

| HD_SDA      | MS7200、MS7210 控制通道 IIC 的数据信号 | H17 |

| RSTN_OUT    | MS7200 、MS7210 硬件复位信号，低电平有效  | E20 |

## 3.4、按键/指示灯/存储接口

### 3.4.1、按键

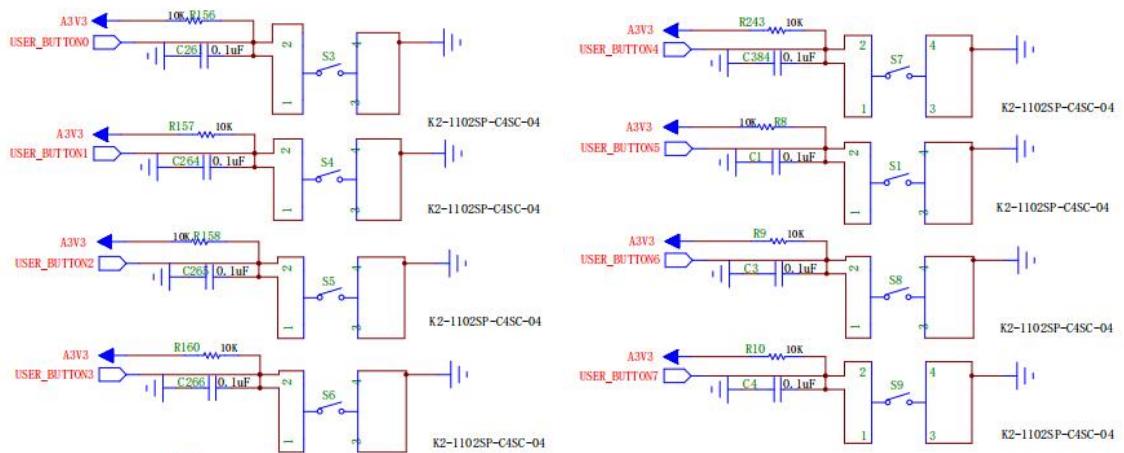

MES2T900-390HP 开发板上扩展有 8 个用户按键，按键连接在 FPGA 普通 IO 上，低电平有效；按键未按下时，按键信号为高电平，当按键按下时，按键信号为低电平。

RSTN

按键电路图

具体管脚分配如下：

| 信号           | 描述     | PG2T390H-900 管脚 |

|--------------|--------|-----------------|

| USER_BUTTON0 | 按键控制信号 | P28             |

| USER_BUTTON1 |        | P27             |

| USER_BUTTON2 |        | T28             |

| USER_BUTTON3 |        | R28             |

| USER_BUTTON4 |        | U28             |

| USER_BUTTON5 |        | U27             |

| USER_BUTTON6 |        | R26             |

| USER_BUTTON7 |        | P26             |

| REST         |        | K10             |

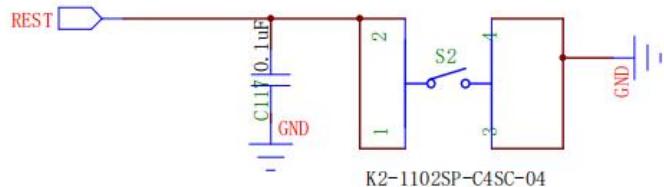

### 3.4.2、LED 灯

MES2T900-390HP 开发板上扩展有 8 个用户 LED 灯, FPGA 输出高电平时 LED 灯亮。

扩展板上 LED 灯功能电路图如下图所示：

LED 灯电路图

具体的管脚分配如下所示：

| 信号        | 描述        | PG2T390H-900 管脚 |

|-----------|-----------|-----------------|

| USER_LED0 | LEDO 控制信号 | V30             |

| USER_LED1 | LED1 控制信号 | V29             |

| USER_LED2 | LED2 控制信号 | V20             |

| USER_LED3 | LED3 控制信号 | V19             |

| USER_LED4 | LED4 控制信号 | W24             |

| USER_LED5 | LED5 控制信号 | W23             |

| USER_LED6 | LED6 控制信号 | V24             |

| USER_LED7 | LED7 控制信号 | U24             |

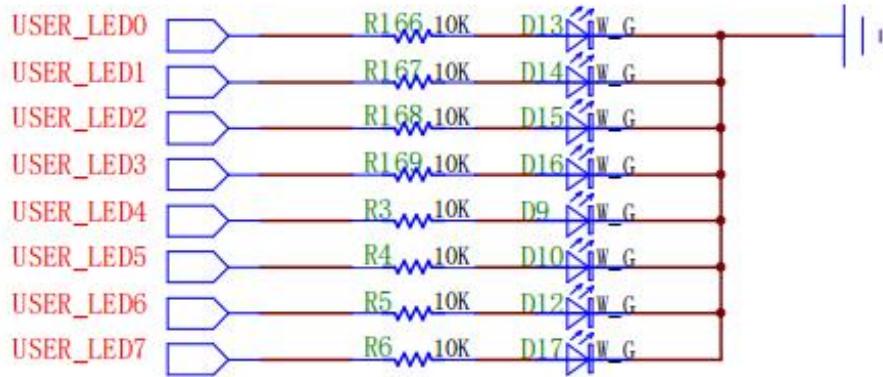

### 3.4.3、EEPROM

MES2T900-390HP 开发板板载了一片容量为：2Kbit (1\*256\*8bit) 的 EEPROM，型号为 AT24C02,由 1 个 256byte 的 block 组成,通过 IIC 总线进行通信。EEPROM 的 I2C 信号连接的 FPGA 的 IO 口上。下图为 EEPROM 的设计示意图；

EEPROM 的设计示意图

具体的管脚分配如下：

| 信号  | 描述        | PG2T390H-900 管脚 |

|-----|-----------|-----------------|

| SCL | EEPROM 时钟 | F18             |

| SDA | EEPROM 数据 | G18             |

### 3.4.4、PMOD 接口

MES2T900-390HP 扩展底板上扩展了 1 个 PMOD 接口，对应 IO Bank 电压及接口

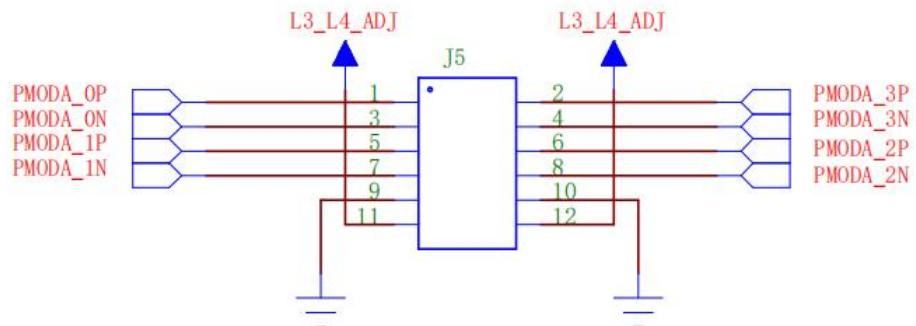

电压为由跳线帽 J4 选择，原理图如下图所示：

PMOD 原理图

具体的管脚分配如下：

| 信号       | 描述 | PG2T390H-900 管脚 |

|----------|----|-----------------|

| PMODA_0P | IO | N25             |

| PMODA_0N | IO | N26             |

| PMODA_1P | IO | M20             |

| PMODA_1N | IO | L20             |

| PMODA_2P | IO | M28             |

| PMODA_2N | IO | L28             |

| PMODA_3P | IO | M29             |

| PMODA_3N | IO | M30             |

### 3.5、时钟

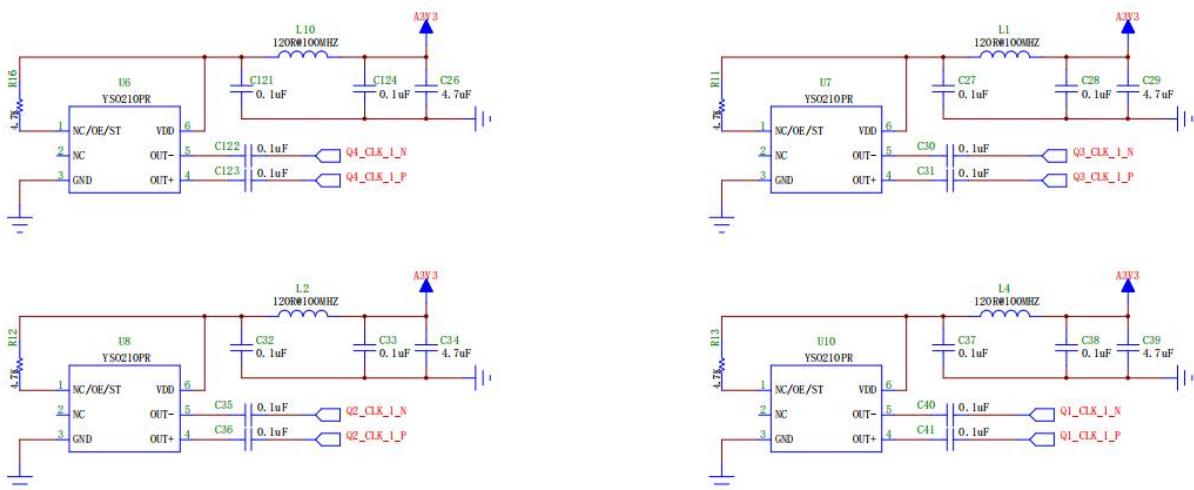

MES2T900-390HP 扩展底板上配有 4 个 125MHz 有源差分晶振。用于 HSST 参考时钟输入。

#### 3.5.1、125MHz 有源差分晶振

下图 U3 为 125MHz 有源差分晶振之一，用于光纤通信的参考时钟输入，晶振时钟输入至 BANK L7 上。

扩展板 125MHz 有源差分晶振

具体的管脚分配如下表所示：

| 信号         | 描述        | PG2T390H-900 管脚 |

|------------|-----------|-----------------|

| Q1_CLK_1_P | HSST 参考时钟 | E8              |

| Q1_CLK_1_N |           | E7              |

| Q2_CLK_1_P |           | J8              |

| Q2_CLK_1_N |           | J7              |

| Q3_CLK_1_P |           | N8              |

| Q3_CLK_1_N |           | N7              |

| Q4_CLK_1_P |           | U8              |

| Q4_CLK_1_N |           | U7              |

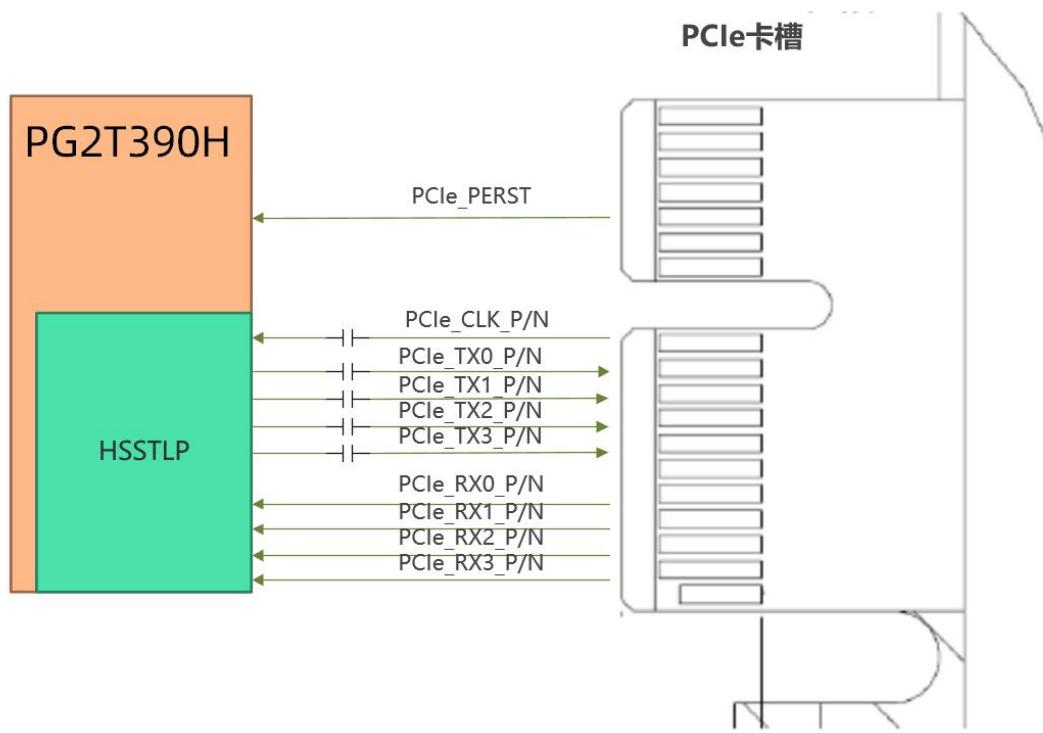

### 3.6、FMC 连接器

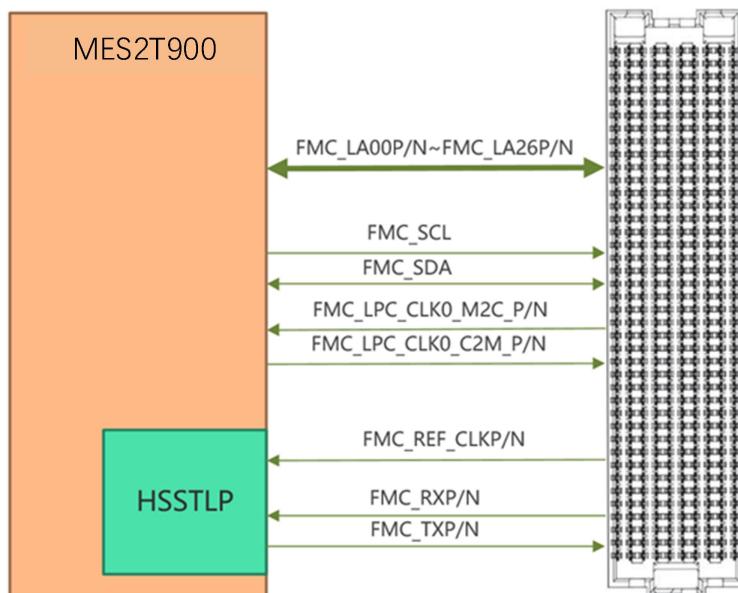

MES2T900-390HP 扩展底板预留了一组 FMC 扩展口，符合 FMC 接口规范，可用于外接 FMC 模块。

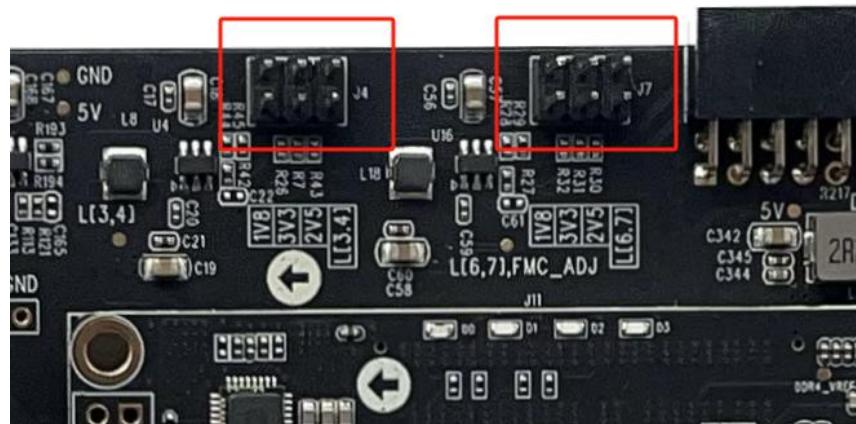

其中 FMC 扩展口共扩展 84 对差分 IO, 1 路 I2C 总线信号, 8 路 HSSTLP 高速串行数据收发信号以及为 HSSTLP 提供的 2 路参考时钟。FMC 扩展的差分信号分别连接在 BANK L3、BANK L4、BANK L6、BANK L7 上，其中 BANK L3\_L4 的 IO 电压由 L3\_L4\_ADJ 决定，且 BANK L3\_L4 可通过跳线帽座连接 J4 处的不同针脚决定为 3.3V 或 2.5V,1.8V，BANK L6 L7 的 IO 电压由 L6\_L7\_ADJ 决定，且 BANK L6\_L7 可通过跳线帽座连接 J7 处的不同针脚决定为 3.3V 或 2.5V,1.8V。

注意：开发板上电前应确认 J4 和 J7 跳线帽的连接，不能悬空，悬空跳线帽会输出 5V 烧坏部分电路。

J4 位置

FPGA 与 FMC 连接器相连的框图如下表所示：

FPGA 与 FMC 连接器相连设计示意图

具体的管脚分配如下表所示：

J2 :

| 信号        | 描述                              | PG2T390H-900 管脚 |

|-----------|---------------------------------|-----------------|

| Q1_RX_2_P | FMC 模块的高速串行口数据线，接收 FPGA 的数据信号 P | B6              |

| Q1_RX_2_N | FMC 模块的高速串行口数据线，接收 FPGA 的数据信号 N | B5              |

| Q1_RX_1_P | FMC 模块的高速串行口数据线，                | D6              |

|           |                                     |    |

|-----------|-------------------------------------|----|

|           | 接收 FPGA 的数据信号 P                     |    |

| Q1_RX_1_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | D5 |

| Q1_RX_0_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | E4 |

| Q1_RX_0_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | E3 |

| Q1_RX_3_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | A8 |

| Q1_RX_3_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | A7 |

| Q2_RX_2_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | G4 |

| Q2_RX_2_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | G3 |

| Q2_RX_0_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | K6 |

| Q2_RX_0_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | K5 |

| Q2_RX_3_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | F6 |

| Q2_RX_3_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | F5 |

| Q2_RX_1_P | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 P | H6 |

| Q2_RX_1_N | FMC 模块的高速串行口数据线,<br>接收 FPGA 的数据信号 N | H5 |

| Q1_TX_2_P | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | B2 |

| Q1_TX_2_N | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | B1 |

| Q1_TX_1_P | FMC 模块的高速串行口数据线,                    | C4 |

|            |                                     |    |

|------------|-------------------------------------|----|

|            | 发送 FPGA 的数据信号 P                     |    |

| Q1_TX_1_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | C3 |

| Q1_TX_0_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | D2 |

| Q1_TX_0_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | D1 |

| Q1_TX_3_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | A4 |

| Q1_TX_3_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | A3 |

| Q2_TX_2_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | H2 |

| Q2_TX_2_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | H1 |

| Q2_TX_0_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | K2 |

| Q2_TX_0_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | K1 |

| Q2_TX_3_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | F2 |

| Q2_TX_3_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | F1 |

| Q2_TX_1_P  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 P | J4 |

| Q2_TX_1_N  | FMC 模块的高速串行口数据线,<br>发送 FPGA 的数据信号 N | J3 |

| Q2_CLK_0_P | FMC 模块的高速串行口参考时钟<br>P               | G8 |

| Q2_CLK_0_N | FMC 模块的高速串行口参考时钟<br>N               | G7 |

| Q1_CLK_0_P | FMC 模块的高速串行口参考时钟                    | C8 |

|            |                    |      |

|------------|--------------------|------|

|            | P                  |      |

| Q1_CLK_0_N | FMC 模块的高速串行口参考时钟 N | C7   |

| CLK0_M2C_P | FMC 参考时钟 P/数据      | L25  |

| CLK0_M2C_N | FMC 参考时钟 N/数据      | K25  |

| CLK1_C2M_P | FMC 参考时钟 P/数据      | J21  |

| CLK1_C2M_N | FMC 参考时钟 N/数据      | J22  |

| CLK1_M2C_P | FMC 参考时钟 P/数据      | AD23 |

| CLK1_M2C_N | FMC 参考时钟 N/数据      | AE24 |

| CLK0_C2M_P | FMC 参考时钟 P/数据      | K23  |

| CLK0_C2M_N | FMC 参考时钟 N/数据      | K24  |

| FMC_SCL    | FMC I2C 总线时钟       | W26  |

| FMC_SDA    | FMC I2C 总线数据       | V25  |

| LA00_P_CC  | FMC 参考数据 (时钟) P    | C25  |

| LA00_N_CC  | FMC 参考数据 (时钟) N    | B25  |

| LA01_P_CC  | FMC 参考数据 (时钟) P    | D26  |

| LA01_N_CC  | FMC 参考数据 (时钟) N    | C26  |

| LA02_P     | FMC 参考数据           | B23  |

| LA02_N     | FMC 参考数据           | A23  |

| LA03_P     | FMC 参考数据           | F25  |

| LA03_N     | FMC 参考数据           | E25  |

| LA04_P     | FMC 参考数据           | B27  |

| LA04_N     | FMC 参考数据           | A27  |

| LA05_P     | FMC 参考数据           | A25  |

| LA05_N     | FMC 参考数据           | A26  |

| LA06_P     | FMC 参考数据           | B30  |

| LA06_N     | FMC 参考数据           | A30  |

| LA07_P     | FMC 参考数据           | C29  |

| LA07_N     | FMC 参考数据           | B29  |

| LA08_P     | FMC 参考数据           | F26  |

| LA08_N     | FMC 参考数据           | E26  |

|           |                 |     |

|-----------|-----------------|-----|

| LA09_P    | FMC 参考数据        | G29 |

| LA09_N    | FMC 参考数据        | F30 |

| LA10_P    | FMC 参考数据        | D29 |

| LA10_N    | FMC 参考数据        | C30 |

| LA11_P    | FMC 参考数据        | H30 |

| LA11_N    | FMC 参考数据        | G30 |

| LA12_P    | FMC 参考数据        | H26 |

| LA12_N    | FMC 参考数据        | H27 |

| LA13_P    | FMC 参考数据        | B28 |

| LA13_N    | FMC 参考数据        | A28 |

| LA14_P    | FMC 参考数据        | C24 |

| LA14_N    | FMC 参考数据        | B24 |

| LA15_P    | FMC 参考数据        | G28 |

| LA15_N    | FMC 参考数据        | F28 |

| LA16_P    | FMC 参考数据        | E23 |

| LA16_N    | FMC 参考数据        | D23 |

| LA17_P_CC | FMC 参考数据 (时钟) P | E28 |

| LA17_N_CC | FMC 参考数据 (时钟) N | D28 |

| LA18_P_CC | FMC 参考数据 (时钟) P | D27 |

| LA18_N_CC | FMC 参考数据 (时钟) N | C27 |

| LA19_P    | FMC 参考数据        | J29 |

| LA19_N    | FMC 参考数据        | H29 |

| LA20_P    | FMC 参考数据        | E24 |

| LA20_N    | FMC 参考数据        | D24 |

| LA21_P    | FMC 参考数据        | G23 |

| LA21_N    | FMC 参考数据        | G24 |

| LA22_P    | FMC 参考数据        | G27 |

| LA22_N    | FMC 参考数据        | F27 |

| LA23_P    | FMC 参考数据        | E29 |

| LA23_N    | FMC 参考数据        | E30 |

| LA24_P    | FMC 参考数据        | J23 |

|           |                 |      |

|-----------|-----------------|------|

| LA24_N    | FMC 参考数据        | J24  |

| LA25_P    | FMC 参考数据        | L22  |

| LA25_N    | FMC 参考数据        | L23  |

| LA26_P    | FMC 参考数据        | L26  |

| LA26_N    | FMC 参考数据        | L27  |

| LA27_P    | FMC 参考数据        | K28  |

| LA27_N    | FMC 参考数据        | K29  |

| LA28_P    | FMC 参考数据        | M22  |

| LA28_N    | FMC 参考数据        | M23  |

| LA29_P    | FMC 参考数据        | N29  |

| LA29_N    | FMC 参考数据        | N30  |

| LA30_P    | FMC 参考数据        | P23  |

| LA30_N    | FMC 参考数据        | N24  |

| LA31_P    | FMC 参考数据        | N27  |

| LA31_N    | FMC 参考数据        | M27  |

| LA32_P    | FMC 参考数据        | P21  |

| LA32_N    | FMC 参考数据        | P22  |

| LA33_P    | FMC 参考数据        | N21  |

| LA33_N    | FMC 参考数据        | N22  |

| HA00_P_CC | FMC 参考数据 (时钟) P | AG29 |

| HA00_N_CC | FMC 参考数据 (时钟) N | AH29 |

| HA01_P_CC | FMC 参考数据 (时钟) P | AB27 |

| HA01_N_CC | FMC 参考数据 (时钟) N | AC27 |

| HA02_P    | FMC 参考数据        | AH26 |

| HA02_N    | FMC 参考数据        | AH27 |

| HA03_P    | FMC 参考数据        | AJ26 |

| HA03_N    | FMC 参考数据        | AK26 |

| HA04_P    | FMC 参考数据        | AD29 |

| LA04_N    | FMC 参考数据        | AE29 |

| HA05_P    | FMC 参考数据        | AE28 |

| HA05_N    | FMC 参考数据        | AF28 |

|           |                 |      |

|-----------|-----------------|------|

| HA06_P    | FMC 参考数据        | AK29 |

| HA06_N    | FMC 参考数据        | AK30 |

| HA07_P    | FMC 参考数据        | AJ28 |

| HA07_N    | FMC 参考数据        | AJ29 |

| HA08_P    | FMC 参考数据        | AJ27 |

| HA08_N    | FMC 参考数据        | AK28 |

| HA09_P    | FMC 参考数据        | AF26 |

| HA09_N    | FMC 参考数据        | AF27 |

| HA10_P    | FMC 参考数据        | AA25 |

| HA10_N    | FMC 参考数据        | AB25 |

| HA11_P    | FMC 参考数据        | AG30 |

| HA11_N    | FMC 参考数据        | AH30 |

| HA12_P    | FMC 参考数据        | AE30 |

| HA12_N    | FMC 参考数据        | AF30 |

| HA13_P    | FMC 参考数据        | AG27 |

| HA13_N    | FMC 参考数据        | AG28 |

| HA14_P    | FMC 参考数据        | Y26  |

| HA14_N    | FMC 参考数据        | AA26 |

| HA15_P    | FMC 参考数据        | W27  |

| HA15_N    | FMC 参考数据        | W28  |

| HA16_P    | FMC 参考数据        | AC26 |

| HA16_N    | FMC 参考数据        | AD26 |

| HA17_P_CC | FMC 参考数据 (时钟) P | AD27 |

| HA17_N_CC | FMC 参考数据 (时钟) N | AD28 |

| HA18_P    | FMC 参考数据        | AB29 |

| HA18_N    | FMC 参考数据        | AB30 |

| HA19_P    | FMC 参考数据        | AC29 |

| HA19_N    | FMC 参考数据        | AC30 |

| HA20_P    | FMC 参考数据        | Y28  |

| HA20_N    | FMC 参考数据        | AA28 |

| HA21_P    | FMC 参考数据        | W29  |

|           |                 |      |

|-----------|-----------------|------|

| HA21_N    | FMC 参考数据        | Y29  |

| HA22_P    | FMC 参考数据        | Y30  |

| HA22_N    | FMC 参考数据        | AA30 |

| HA23_P    | FMC 参考数据        | AA27 |

| HA23_N    | FMC 参考数据        | AB28 |

| HB00_P_CC | FMC 参考数据 (时钟) P | AE23 |

| HB00_N_CC | FMC 参考数据 (时钟) N | AF23 |

| HB01_P    | FMC 参考数据        | AD21 |

| HB01_N    | FMC 参考数据        | AE21 |

| HB02_P    | FMC 参考数据        | Y23  |

| HB02_N    | FMC 参考数据        | Y24  |

| HB03_P    | FMC 参考数据        | AB22 |

| HB03_N    | FMC 参考数据        | AB23 |

| HB04_P    | FMC 参考数据        | AC20 |

| LB04_N    | FMC 参考数据        | AC21 |

| HB05_P    | FMC 参考数据        | Y21  |

| HB05_N    | FMC 参考数据        | AA21 |

| HB06_P_CC | FMC 参考数据 (时钟) P | AF22 |

| HB06_N_CC | FMC 参考数据 (时钟) N | AG23 |

| HB07_P    | FMC 参考数据        | AF20 |

| HB07_N    | FMC 参考数据        | AF21 |

| HB08_P    | FMC 参考数据        | AJ22 |

| HB08_N    | FMC 参考数据        | AJ23 |

| HB09_P    | FMC 参考数据        | AH21 |

| HB09_N    | FMC 参考数据        | AJ21 |

| HB10_P    | FMC 参考数据        | AJ24 |

| HB10_N    | FMC 参考数据        | AK25 |

| HB11_P    | FMC 参考数据        | AK20 |

| HB11_N    | FMC 参考数据        | AK21 |

| HB12_P    | FMC 参考数据        | AK23 |

| HB12_N    | FMC 参考数据        | AK24 |

|           |                 |      |

|-----------|-----------------|------|

| HB13_P    | FMC 参考数据        | AG20 |

| HB13_N    | FMC 参考数据        | AH20 |

| HB14_P    | FMC 参考数据        | AA22 |

| HB14_N    | FMC 参考数据        | AA23 |

| HB15_P    | FMC 参考数据        | AE25 |

| HB15_N    | FMC 参考数据        | AF25 |

| HB16_P    | FMC 参考数据        | AK23 |

| HB16_N    | FMC 参考数据        | AK24 |

| HB17_P_CC | FMC 参考数据 (时钟) P | AG24 |

| HB17_N_CC | FMC 参考数据 (时钟) N | AH24 |

| HB18_P    | FMC 参考数据        | AC24 |

| HB18_N    | FMC 参考数据        | AD24 |

| HB19_P    | FMC 参考数据        | AG22 |

| HB19_N    | FMC 参考数据        | AH22 |

| HB20_P    | FMC 参考数据        | AC22 |

| HB20_N    | FMC 参考数据        | AD22 |

| HB21_P    | FMC 参考数据        | AA20 |

| HB21_N    | FMC 参考数据        | AB20 |

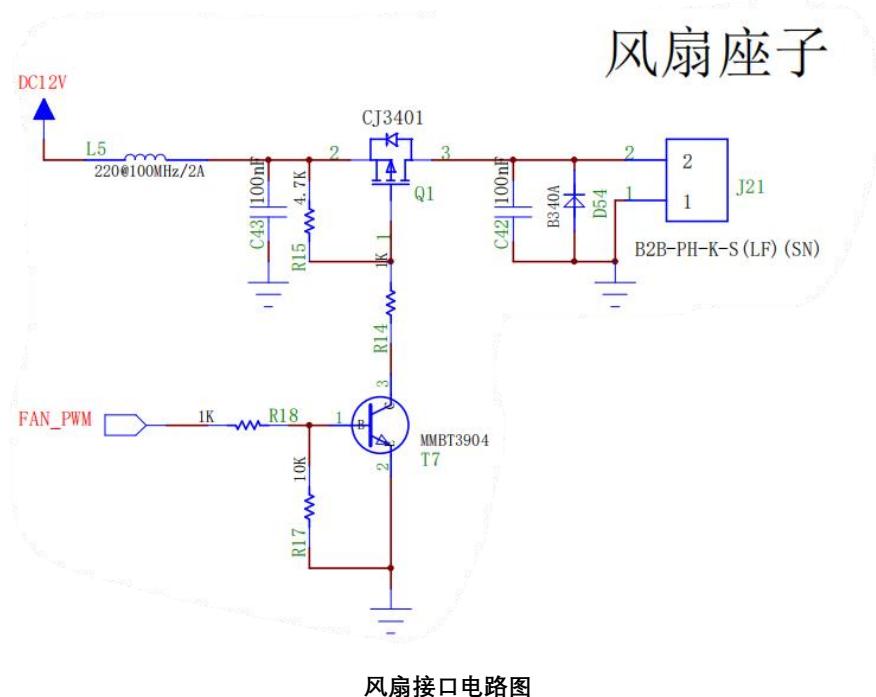

### 3.7、外接风扇

MES2T900-390HP 开发板上预留有 1 个外接风扇接口。

具体的管脚分配如下所示：

| 信号      | 描述     | PG2T390H-900 管脚 |

|---------|--------|-----------------|

| FAN_PWM | 风扇控制引脚 | V21             |

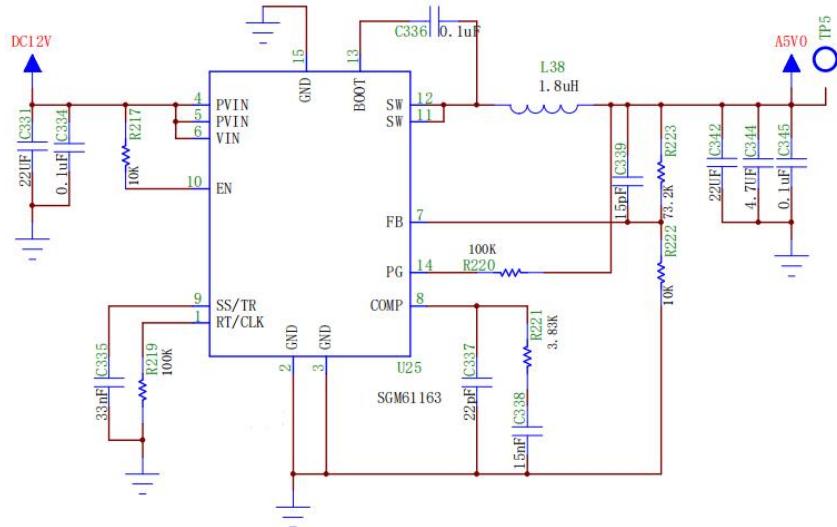

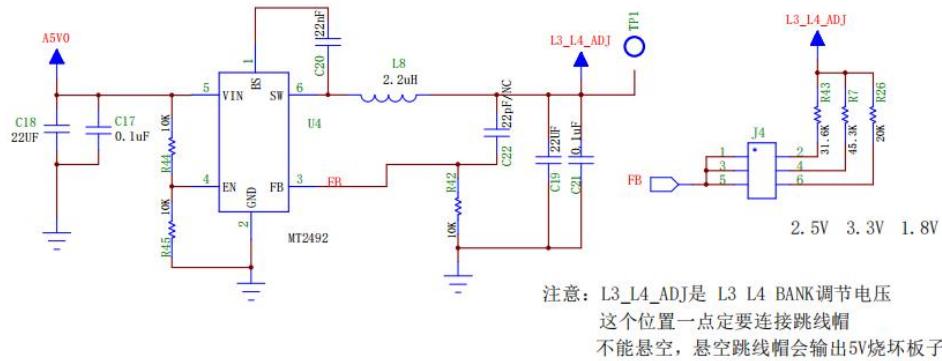

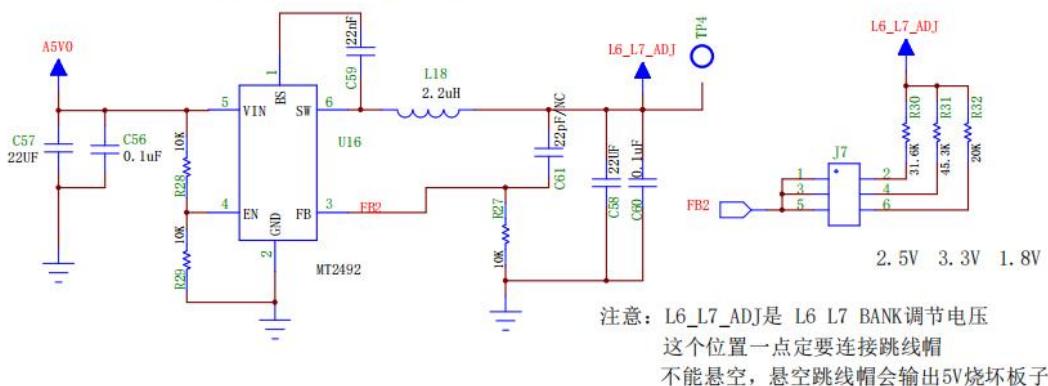

### 3.8、供电电源

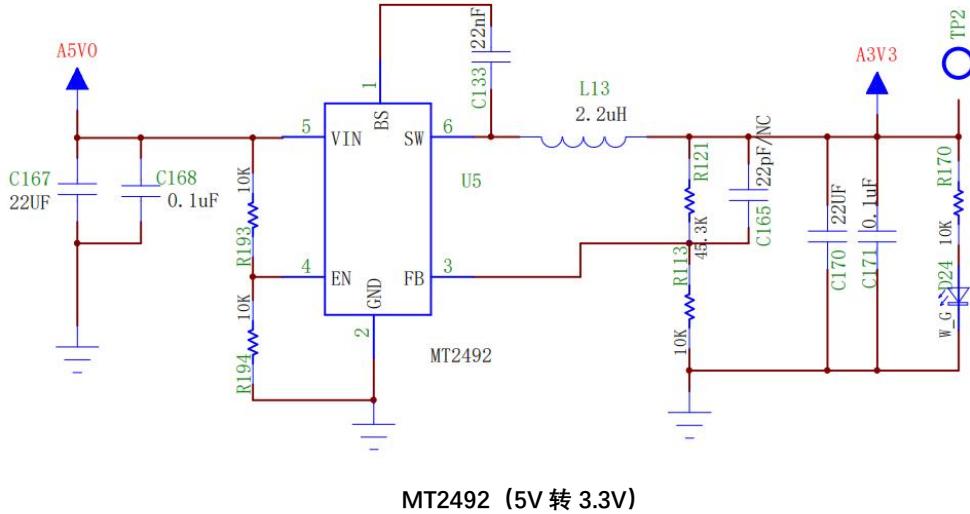

开发板的电源输入电压为+12V, 请使用开发板自带的电源, 不要用其他规格的电源,以免损坏开发板。扩展板上通过 1 路 DC/DC 电源芯片 SGM61163 把+12V 电压转化成+5V 电源, 最大输出电流 6A;再使用三颗 DC/DC 电源芯片 MT2492 把+5V 分别转换出+3.3V、L3\_L4\_ADJ(3.3V,2.5V,1.8V)和 L6\_L7\_ADJ(3.3V,2.5V,1.8V)电源最大输出电流 2A 供外设接口和 FPGA Bank 电源使用 ; 扩展板上的+5V 电源通过板间连接器给核心板供电,扩展板上电源设计如下图所示:

SGM61163 (12V 转 5V)

$$V_{out} = 0.6 * (1 + R1/R2)$$

MT2492 (5V 转 L3\_L4\_Adjust-3.3,2.5V,1.8V)

$$V_{out} = 0.6 * (1 + R1/R2)$$

MT2492 (5V 转 L6\_L7\_Adjust-3.3,2.5V,1.8V)

$$V_{out} = 0.6 * (1 + R1/R2)$$

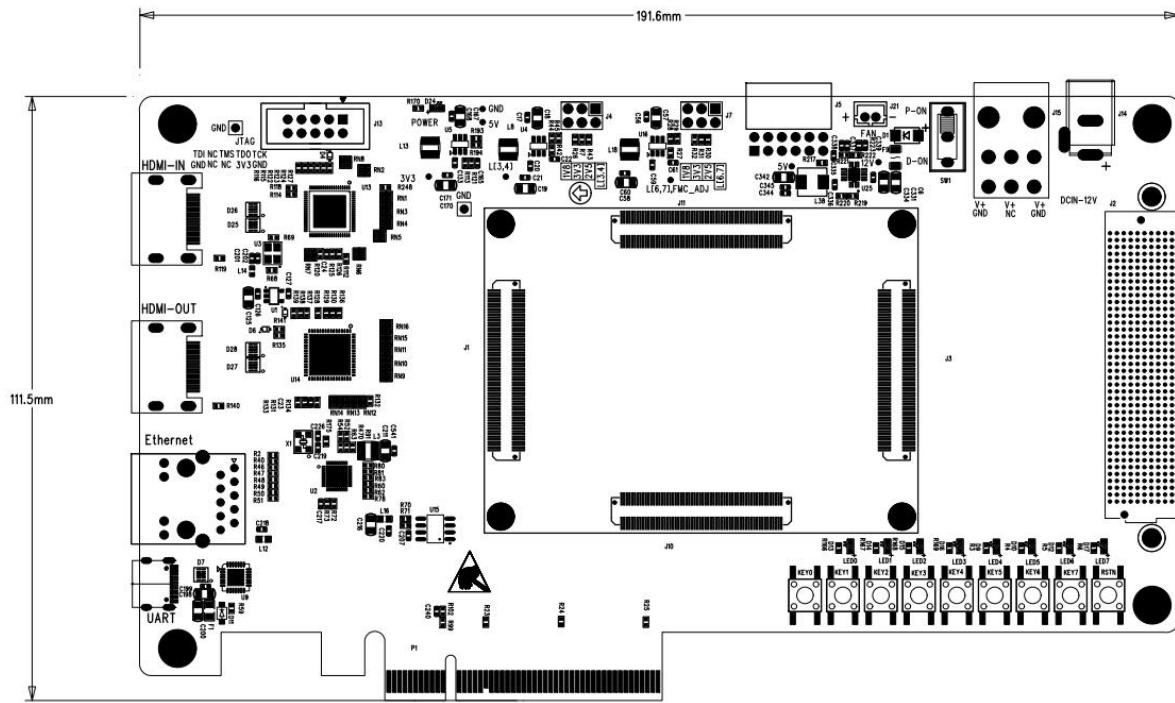

### 3.9、底板尺寸图

扩展底板尺寸图