# 盘古 22 开发板(MES22GP) 硬件使用手册 V1.0

紫光同创 logos 系列 FPGA 开发平台

版本日期：2022-11-24

Administrator: 深圳市小眼睛半导体科技有限公司

联系邮箱：[support@meyesemi.com](mailto:support@meyesemi.com)

QQ 群：[808770961](#)

公司网址：[www.meyesemi.com](http://www.meyesemi.com)

微信公众号：小眼睛 FPGA

购买渠道：[小眼睛半导体](#)

客服微信：17665247134

## 版本记录

| 日期         | 版本   | 修改原因 |

|------------|------|------|

| 2022.11.24 | V1.0 | 创建文档 |

|            |      |      |

## 目录

|                          |    |

|--------------------------|----|

| 1 开发板简介 .....            | 2  |

| 1.1 概述 .....             | 2  |

| 1.2 开发系统简介 .....         | 2  |

| 1.2.1 系统资源 .....         | 2  |

| 1.2.2 板卡尺寸 .....         | 5  |

| 2 接口描述 .....             | 7  |

| 2.1 电源时钟及加载 .....        | 7  |

| 2.1.1 电源 .....           | 7  |

| 2.1.2 时钟 .....           | 8  |

| 2.1.3 上电 IO Status ..... | 9  |

| 2.1.4 JTAG 接口 .....      | 9  |

| 2.2 Memory .....         | 10 |

| 2.2.1 DDR3 .....         | 10 |

| 2.2.2 QSPI Flash .....   | 12 |

| 2.2.3 SD card 接口 .....   | 13 |

| 2.3 外接通信口 .....          | 14 |

| 2.3.1 网口 .....           | 14 |

| 2.3.2 PMOD 接口 .....      | 15 |

| 2.3.3 扩展 IO 接口 .....     | 17 |

| 2.3.4 串口 .....           | 17 |

| 2.4 HDMI .....           | 19 |

| 2.4.1 HDMI 输入接口 .....    | 19 |

| 2.4.2 HDMI 输出接口 .....    | 21 |

| 2.5 按键开关及指示灯 .....       | 22 |

| 2.5.1 按键 .....           | 22 |

| 2.5.2 Led 灯 .....        | 24 |

| 2.5.3 数码管 .....          | 25 |

| 2.5.4 拨动开关 .....         | 26 |

## 1 开发板简介

### 1.1 概述

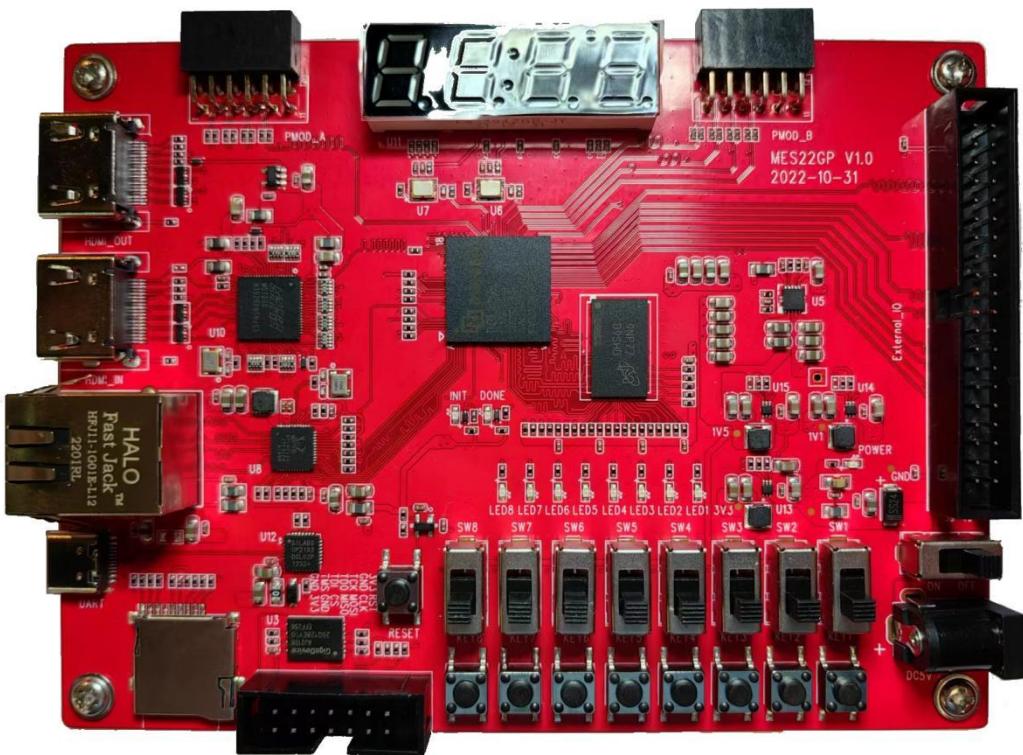

MES22GP 开发板是 MEYESEMI 基于多年在 FPGA 领域开发经验，及多个业务场景的应用特点，而开发的一套全新的国产 FPGA 开发套件，MES22GP 开发板采用紫光同创 40nm 工艺的 FPGA 作为主控芯片（logos 系列：PGL22G-MBG324），板卡电源采用圣邦微（SGM61032）解决方案，HDMI 接口采用宏晶微 MS7200，更大程度上实现了国产化，预留 HDMI 收发接口用于图像验证及处理；10/100/1000M 以太网接口，方便各类高速通信系统验证。

图 1.1 MES22GP 开发板

### 1.2 开发系统简介

#### 1.2.1 系统资源

MES22GP 开发板是基于紫光同创公司的 logos 系列的 PGL22G 芯片设计的一套开发套件，FPGA 封装选用 MBG324。MES22GP 上在 FPGA 上挂载了一片 16bit 数据位宽的 DDR3，一片 DDR3 的总容量高达 512Mbit，整个系统的存储带宽高达 800Mb/s，充分满足了高速数据的缓存处理需求。

MES22GP 开发板上还扩展了丰富的外围接口，其中包含了一路光纤通信模块接口、一路扩展的差分 40PIN IO 接口、一路千兆以太网接口、一路 HDMI 输入接口、一路 HDMI 输出接口、两路 PMOD (Camera) 2\*6 PIN 接口、一路 SD 卡接口、一路 Uart 接口和 8 个按键、8 个拨动开关、8 个 LED 灯以及一个数码管。

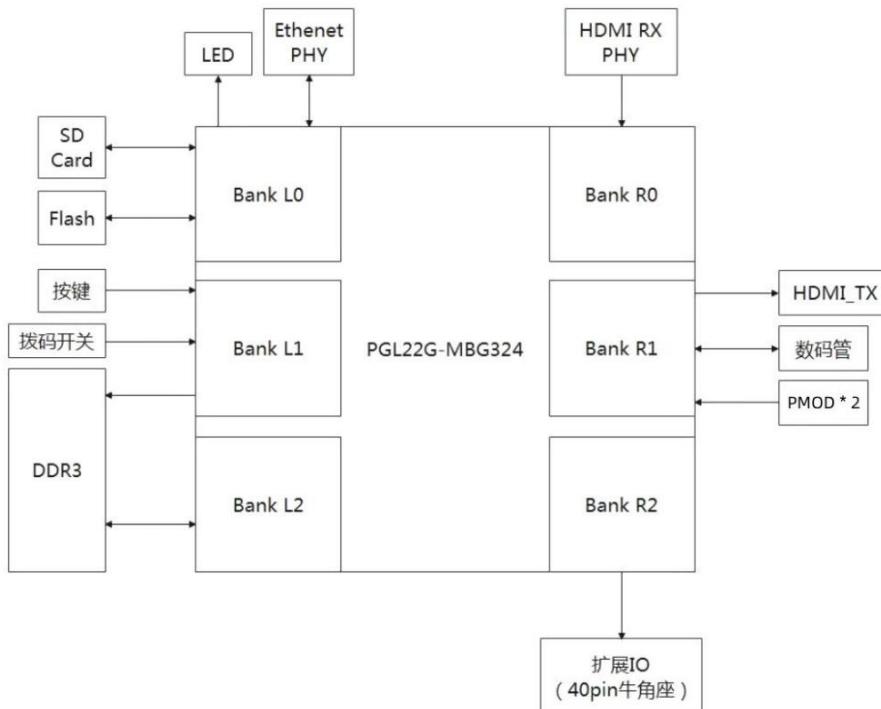

下图为整个开发系统的功能接口框图：

图 1.2 MES22GP 开发板系统功能结构框图

上图中板卡提供的功能详细情况如下：

◎ Pango® PGL22G-MBG324

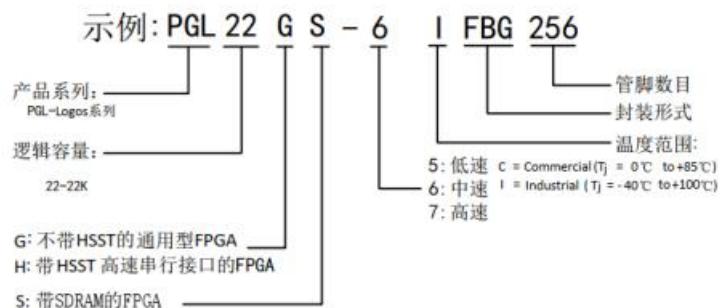

Logos 器件产品型号的命名含义如下：

Logos系列FPGA产品型号的编号内容及意义如图1所示。

图 1.3 Logos2 系列器件命名规则

PGL22G 的主要参数如下表：

表 1.1 PGL22G-MBG324 的主要参数

| 名称               | 具体参数  |

|------------------|-------|

| 触发器(FF)          | 26304 |

| 查找表 LUT5         | 17536 |

| 等效 LUT4          | 21043 |

| DRM (18Kbits) 个数 | 48    |

| APM 单元 (乘法器)     | 30    |

| 模数转换/ADC         | 1     |

| 速度等级             | -6    |

| 温度等级             | 工业级   |

◎ 存储

- 512MB (MT41K256M16 \* 1)

- 128 Mb QSPI Flash (MES 开发板默认启动方式)

◎ 时钟

- 27MHz

单端有源晶振

- 50MHz

单端有源晶振

◎ 外设接口

- POMD 接口 \* 2

12 针 2.54mm 间距的双排弯针母座, 一个座子有 4 对差分信号, 两个共 8 对差分信号, 以及输出 3.3V 电源。

- 10/100/1000 Mbps 以太网 \* 1

千兆以太网接口芯片采用 RTL8211E 以太网 PHY 芯片为用户提供网络通信服务。RTL8211E 芯片支持 10/100/1000 Mbps 网络传输速率; 全双工和自适应。

- HDMI 输出 \* 1

从 IO 引脚引出至 HDMI 座子。

- HDMI 输入 \* 1

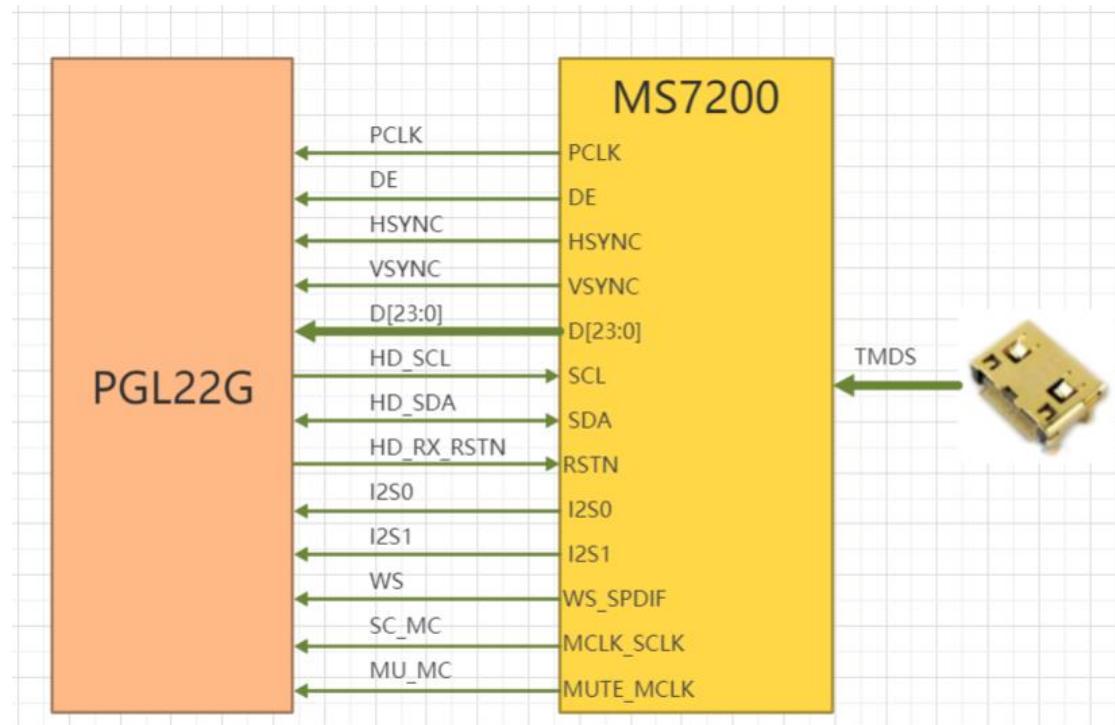

选用了国产宏晶微公司的 MS7200 HDMI 接收芯片，兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz, 最高采样率达到 300MHz; 支持 HBR 音频。

- 扩展 IO 接口 \* 1

40 针 2.54mm 间距的双排简牛座，含 17 组 LVDS 信号与其中有 2 路可作为差分时钟信号，以及含有 3.3V,5V 输出电源；

- USB 转串口 \* 1

用于和电脑通信，方便用户调试。串口芯片采用 Silicon Labs 的 USB-UAR 芯片: CP2102 , USB 接口采用 USB Type C 接口。

- Micro SD 卡座

支持 SDIO 模式和 SPI 模式。

- JTAG 接口

14 针 2.54mm 间距的双排排针口，用于 FPGA 程序的下载和调试；

- 用户 LED

8 个用户发光二极管；

- 用户按键

8 个用户按键，1 个复位按键；

- 用户拨动开关

8 个用户拨动开关；

- 数码管

1 个四位发光数码管；

### 1.2.2 板卡尺寸

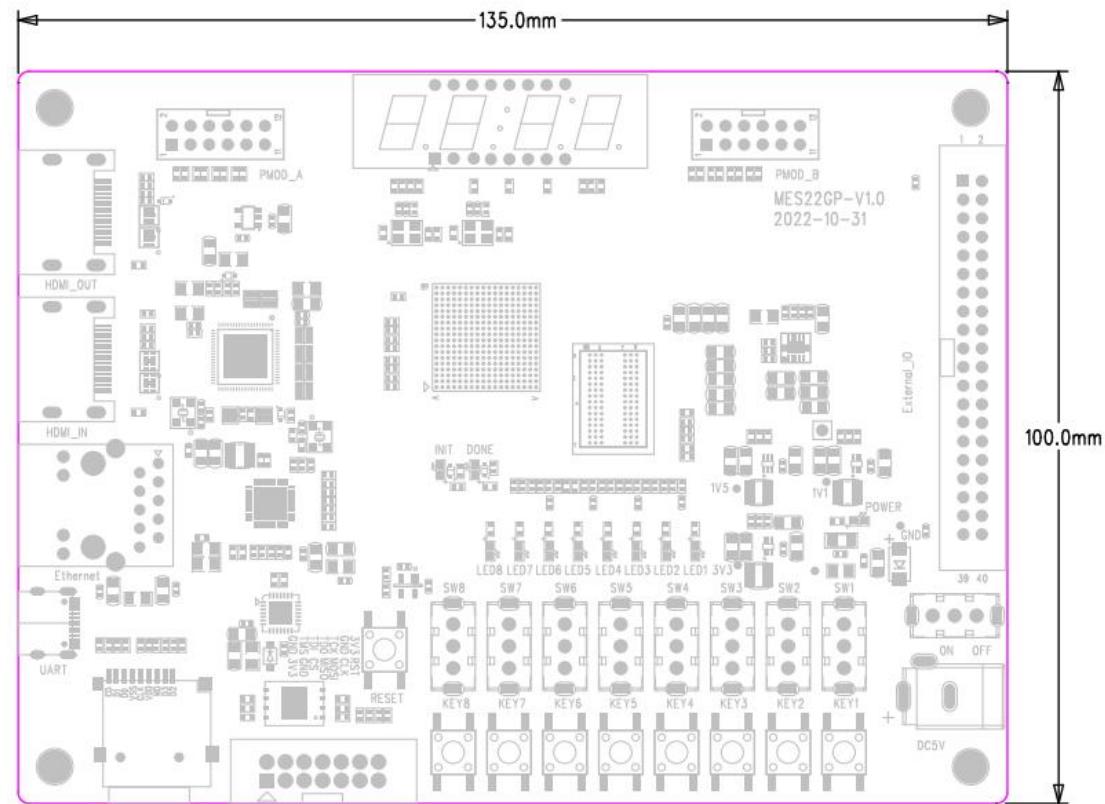

MES22GP 开发板的板卡尺寸如下图：

图 1.5 MES22GP 开发板尺寸图

## 2 接口描述

### 2.1 电源时钟及加载

#### 2.1.1 电源

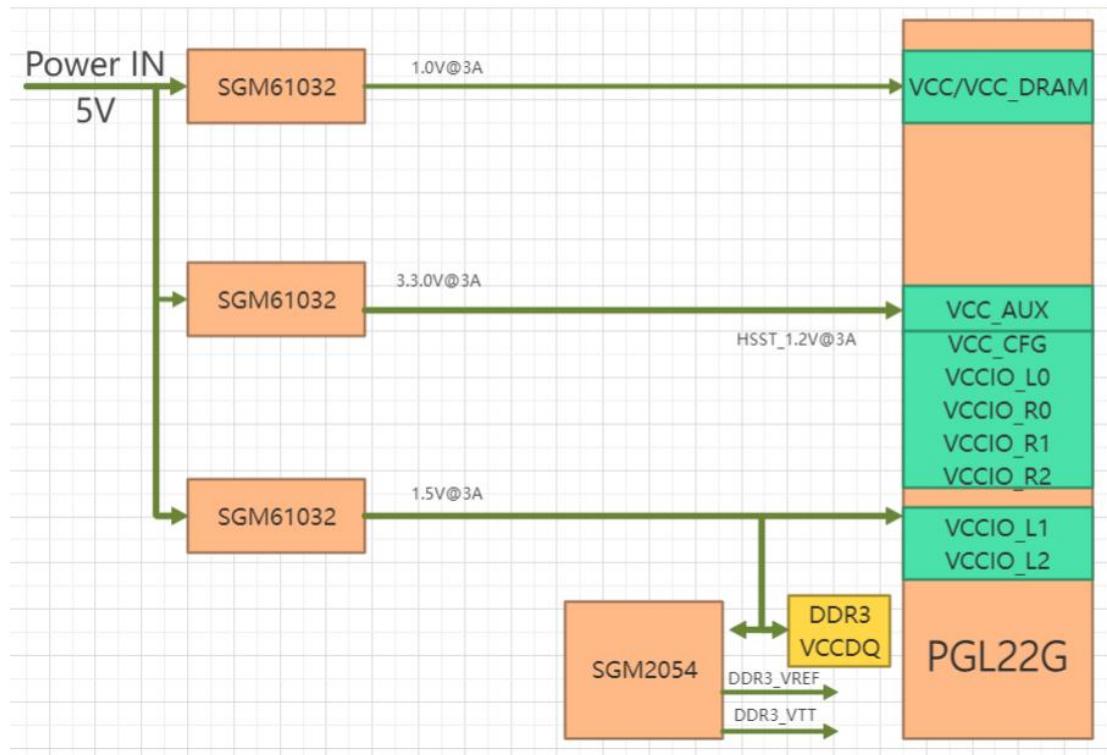

MES22GP 开发板的主要电源共有 3 路，电源外部输入支持 5V。系统的电源网络如下图：

图 2.1 电源拓扑图

各个电源的功能作用如下表：

表 2.1 各路电源功能

| 电源          | 功能用途                                            |

|-------------|-------------------------------------------------|

| 5.0V        | 低电压 DC-DC 的电源，HDMI 接口 5V                        |

| 1.1V        | PGL22G 的内核电压                                    |

| 3.3V        | I/O 电压，部分接口（以太网，数码管，LED 灯，开关，FLASH，SD card）供电电压 |

| 1.5V        | DDR3 供电电压，PGL22G Bank L1、Bank L2 电源             |

| VTT(0.75V)  | DDR3 控制线与地址线的上拉电压，保持信号完整性                       |

| VREF(0.75V) | DDR3 参考电压                                       |

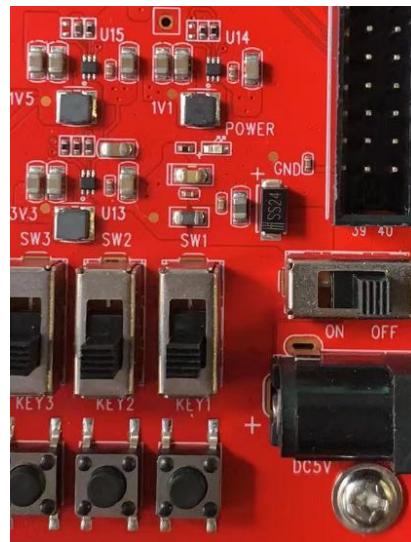

MES22GP 开发板外部电源的输入电压为 DC5V，板上有一个上电开关，在 DC 座旁边。拨码往左拨给板子上电，右拨给板子掉电。注：TYPE-C 方口只能当串口使用，不能作为供电接口；

图 2.2 电源输入接口实物图

### 2.1.2 时钟

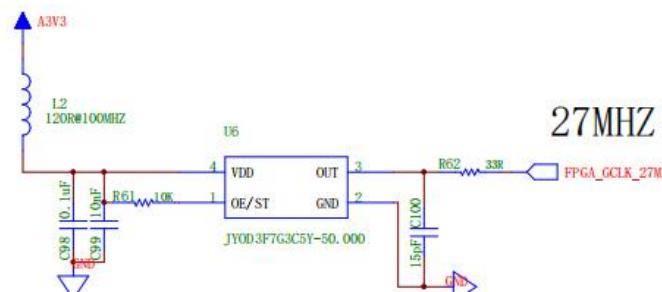

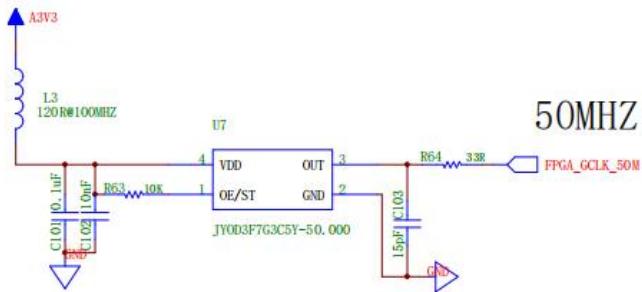

MES22GP 板上配有 2 个有源单端晶振给 PGL22G 提供时钟，有源单端晶振频率分别为 50MHz 和 27MHz，均可用作 FPGA 的系统运行主时钟的时钟源。

具体管脚分配请看下表：

表 2.2 单端有源晶振

| 信号            | PGL22G Pin |

|---------------|------------|

| FPGA_GCLK_27M | J18        |

| FPGA_GCLK_50M | H18        |

下图为有源单端晶振电路，这两个时钟是给 FPGA 内部的逻辑提供输入时钟，可用于逻辑设计或是通过 PLL 来产生不同频率的时钟。

图 2.3 有源单端晶振电路

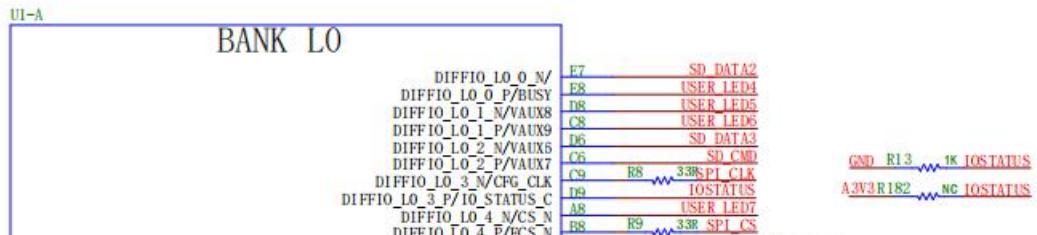

### 2.1.3 上电 IO Status

在 Logos 器件上有一个功能复用 IO，控制从上电完成后到进入用户模式之前中所有用户 IO 的弱上拉电阻是否使能。此管脚在配置之前或是配置过程中，该引脚不允许悬空，此 IO 在上电后的对应功能如下：

- (1) “0”，使能所有用户 IO 内部上拉电阻。

- (2) “1”，不使能所有用户 IO 内部上拉电阻。

MES22GP 将此管脚的功能默认接 GND，用户可根据需求，自行焊接电阻选择上电后初始的 IO 状态；

功能电路如下：

图 2.4 IO Status 配置电路

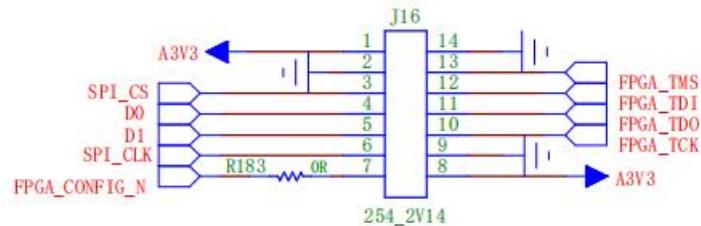

#### 2.1.4 JTAG 接口

MES22GP 开发板预留了一个 JTAG 接口，用于下载 FPGA 程序或者固化程序到 FLASH。

图 2.5 JTAG 接口电路

此 14pin 接口还连接到了板上的 QSPI Flash 上，通过对 FPGA\_CONFIG\_N 拉低，使 PGL22G 进入复位状态，释放出 QSPI Flash 的操控权限，这时我们可以通过这个接口直接烧录 Flash；

## 2.2 Memory

### 2.2.1 DDR3

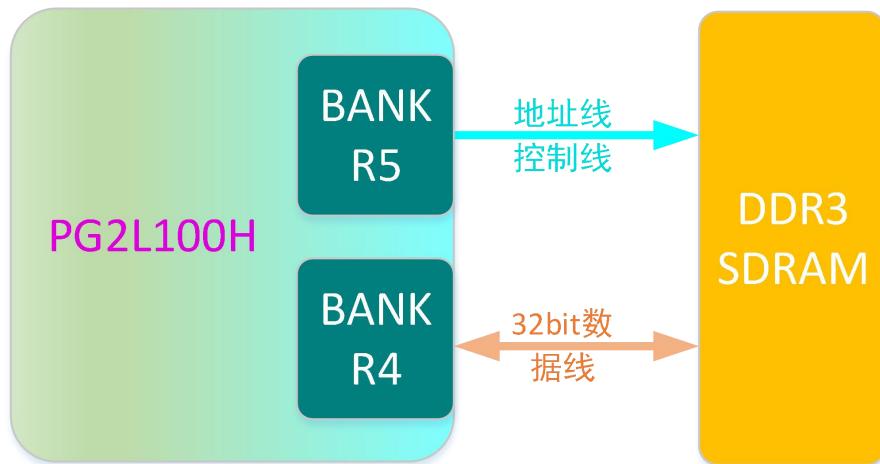

MES22GP 开发板上有一片 Micron 的 DDR3 (MT41K256M16 TW107: P) 内存组件，拥有 16bit 位宽的存储空间。DDR3 DRAM 的硬件连接示意图如图 2.2 所示：

图 2.6 MES22GP 的 DDR3 连接图

PGL22G 内可运行 DDR 控制器最大支持位宽可达 72bit，速度高达 533MHz (1066Mbps)。DDR3 使用 1.5V SSTL 接口标准，在 MES22GP 开发板上 PGL22G 与 DDR3 紧密的排列在一起，保持连接和匹配。

DDR3 布线采用 50 欧姆走线阻抗用于单端信号，DCI 电阻 (VRP / VRN) 以及差分时钟设置为 100 欧姆。每个 DDR3 芯片在 ZQ 上都需要 240 欧姆电阻下拉。DDR-VDDQ 设置为 1.5V，以支持所选的 DDR3 器件。DDR-VTT 是与

DDR-VDDQ 始终电压跟随，保持为  $\frac{1}{2}$  倍 DDR-VDDQ 的电压值。DDR-VREF 是一个独立的缓冲输出，等于  $\frac{1}{2}$  倍 DDR-VDDQ 的电压。DDR-VREF 是隔离的，可为 DDR 电平转换提供更清晰的参考。

该 DDR3 存储系统直接连接到了 PGL22G 的 Bank R4 及 Bank R5 上；DDR3 的硬件设计需要严格考虑信号完整性，我们在电路设计和 PCB 设计的时候已经充分考虑了匹配电阻/终端电阻，走线阻抗控制，走线等长控制，保证 DDR3 的高速稳定的工作。

DDR3 的具体管脚分配如下：

表 2.3 PGL22G 上的 DDR3 连接引脚分配表

| 信号名称          | PGL22G<br>管脚 | 信号名称          | PGL22G<br>管脚 |

|---------------|--------------|---------------|--------------|

| ddr3_addr[0]  | M4           | ddr3_addr[14] | J2           |

| ddr3_addr[1]  | M3           | ddr3_addr[15] | J1           |

| ddr3_addr[2]  | P2           | ddr3_ba[0]    | U2           |

| ddr3_addr[3]  | P1           | ddr3_ba[1]    | U1           |

| ddr3_addr[4]  | L5           | ddr3_ba[2]    | T2           |

| ddr3_addr[5]  | M5           | ddr3_cas_n    | T1           |

| ddr3_addr[6]  | N2           | ddr3_ck_n     | V3           |

| ddr3_addr[7]  | N1           | ddr3_ck_p     | U3           |

| ddr3_addr[8]  | K4           | ddr3_cke      | L4           |

| ddr3_addr[9]  | M1           | ddr3_cs_n     | R1           |

| ddr3_addr[10] | M6           | ddr3_odt      | V2           |

| ddr3_addr[11] | L1           | ddr3_ras_n    | R2           |

| ddr3_addr[12] | K2           | ddr3_reset_n  | M2           |

| ddr3_addr[13] | K1           | ddr3_we_n     | V1           |

| ddr3_dm[0]    | R8           | ddr3_dm[1]    | U5           |

| ddr3_dq[0]    | T8           | ddr3_dq[8]    | T4           |

| ddr3_dq[1]    | T6           | ddr3_dq[9]    | V9           |

|               |    |               |    |

|---------------|----|---------------|----|

| ddr3_dq[2]    | R6 | ddr3_dq[10]   | U9 |

| ddr3_dq[3]    | R9 | ddr3_dq[11]   | V7 |

| ddr3_dq[4]    | T9 | ddr3_dq[12]   | U7 |

| ddr3_dq[5]    | N4 | ddr3_dq[13]   | V6 |

| ddr3_dq[6]    | N5 | ddr3_dq[14]   | U6 |

| ddr3_dq[7]    | P6 | ddr3_dq[15]   | V5 |

| ddr3_dqs_n[0] | N7 | ddr3_dqs_p[1] | U8 |

| ddr3_dqs_p[0] | N6 | ddr3_dqs_n[1] | V8 |

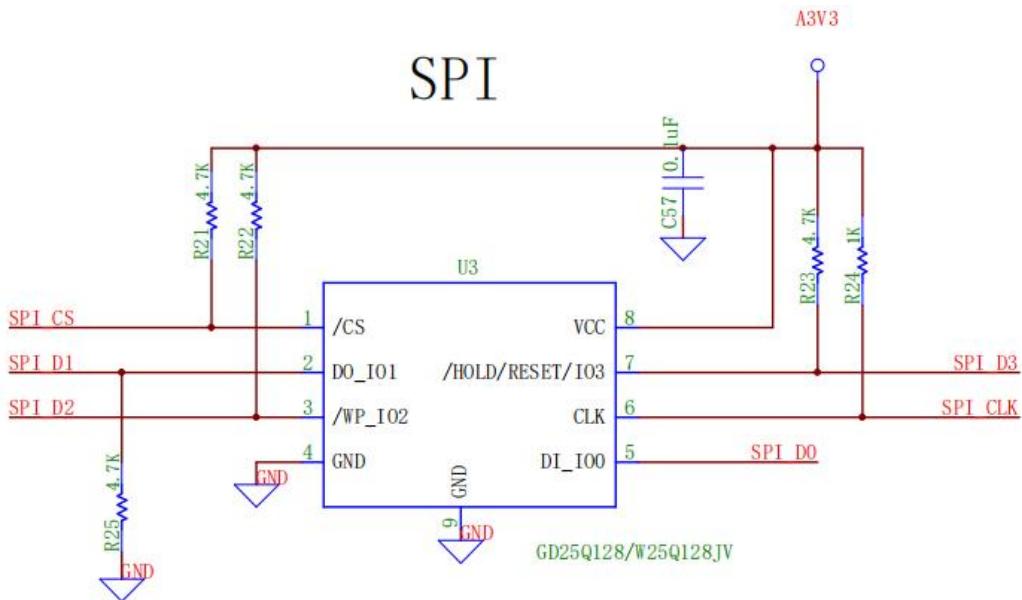

## 2.2.2 QSPI Flash

MES22GP 开发板具有 4 位 SPI (QSPI) 串行 Nor 闪存，使用的是兆易创新的 GD25Q128E。连接在 PGL22G 的特定引脚上，采用 3.3V 电平标准。

QSPI 的电路连接如下：

图 2.7 Flash 电路图

管脚分配如下

表 2.4 QSPI Flash 引脚图

| 信号  | 描述     | PGL22G Pin | QSPI Pin |

|-----|--------|------------|----------|

| CS  | 片选     | B8         | 1        |

| DQ0 | 数据位 0  | B4         | 5        |

| DQ1 | 数据位 1  | A4         | 2        |

| DQ2 | 数据位 2  | B3         | 3        |

| DQ3 | 数据位 3  | A3         | 7        |

| SCK | 串行数据时钟 | C9         | 6        |

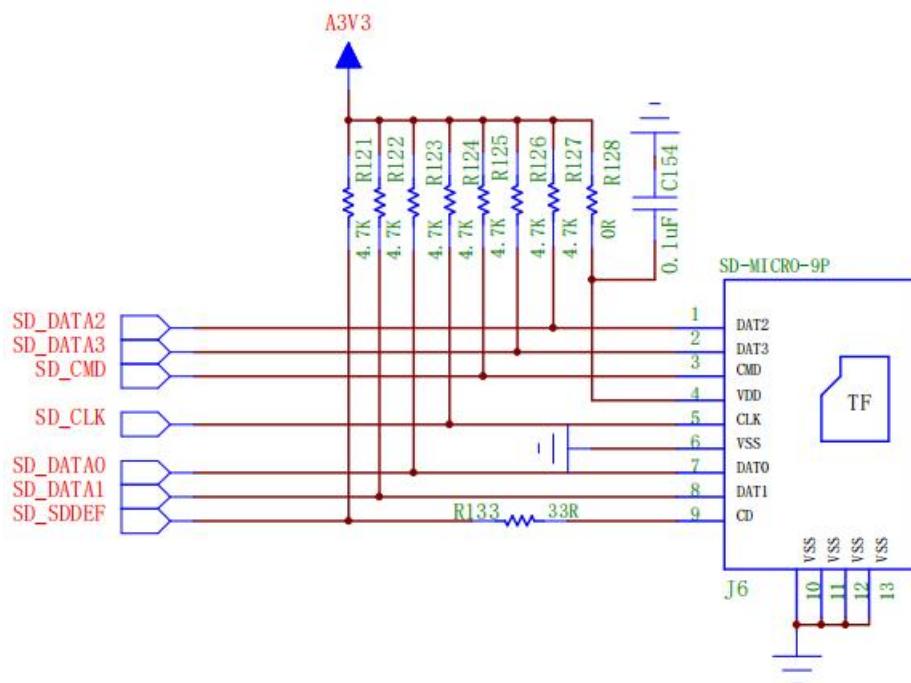

### 2.2.3 SD card 接口

SD 卡是现在非常常用的存储设备，我们扩展出来的 SD 卡，支持 SPI 模式和 SD 模式，使用的 SD 卡为 MicroSD 卡。原理图如下图所示。SD 卡是 3.3V 接口。

图 2.8 SDCARD 电路

表 2.5 SDCARD 引脚示例

| 信号        | 描述    | PGL22G Pin                            | SD Card Pin      |

|-----------|-------|---------------------------------------|------------------|

| CLK       | 时钟    | A5                                    | 5                |

| CMD       | 命令串行线 | C6                                    | 3                |

| DATA[0:3] | 数据线   | D0: B6<br>D1: A6<br>D2: C17<br>D3: E7 | 7<br>8<br>1<br>2 |

| DETCT     | 卡识别   | B7                                    | 9                |

## 2.3 外接通信口

### 2.3.1 网口

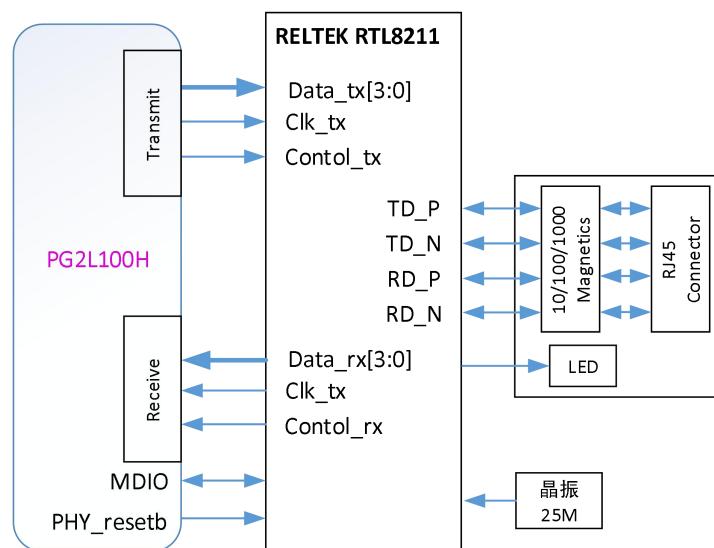

MES22GP 开发板使用 Realtek RTL8211E PHY 实现了一个 10/100/1000 以太网端口，用于网络连接。该器件工作电压为支持 2.5V、3.3V。PHY 连接到 BANK R3，并通过 RGMII 接口连接到 PGL22G。RJ-45 连接器是 HFJ11-1G01E-L12RL，具有集成的自动缠绕磁性元件，可提高性能，质量和可靠性。RJ-45 有两个状态指示灯 LED，用于指示流量和有效链路状态。

下图显示了 MES22GP 开发板上的网口连接框图。

图 2.9 RTL8211 连接示例

下表显示了 PGL22G 与 RTL8211E 的管脚连接。

表 2.6 PGL22G 连接 RTL8211 引脚情况

| 信号名称    | 描述         | PGL22G 管脚 | RTL8211E Pin |

|---------|------------|-----------|--------------|

| RX_CLK  | 接收时钟线      | B5        | 40           |

| RX_CTRL | 接收控制线      | G4        | 37           |

| RXD[3]  | 接收数据线 3    | D1        | 38           |

| RXD[2]  | 接收数据线 2    | E2        | 39           |

| RXD[1]  | 接收数据线 1    | E1        | 41           |

| RXD[0]  | 接收数据线 0    | F4        | 42           |

| TX_CLK  | 发送时钟线      | D2        | 47           |

| TX_CTRL | 发送控制线      | D4        | 2            |

| TXD[3]  | 发送数据线 3    | B2        | 44           |

| TXD[2]  | 发送数据线 2    | B1        | 45           |

| TXD[1]  | 发送数据线 1    | C2        | 48           |

| TXD[0]  | 发送数据线 0    | C1        | 1            |

| MDC     | 控制总线时钟     | A1        | 5            |

| MDIO    | 控制总线数据     | A2        | 4            |

| RSTN    | 复位控制线, 低有效 | 重加载固件按键   | 29           |

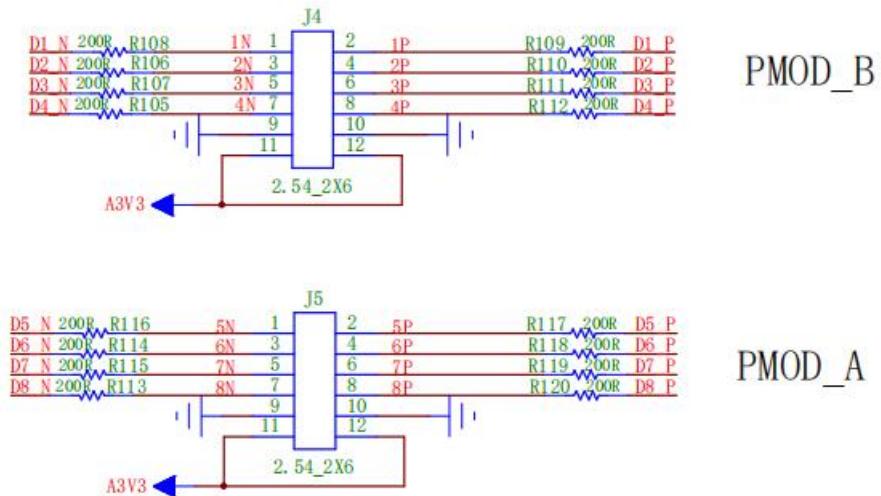

### 2.3.2 PMOD 接口

MES22GP 板上有 2 路 PMOD 接口, 2 路接口分别跟 FPGA 的 差分信号管脚相连接, 用户可根据需求运用此两路接口功能。

PMOD 原理图如下图所示:

图 2.10 PMOD 连接器

下表显示了 PGL22G 与 2 个 PMOD 接口的管脚连接。

表 2.7 PGL22G 引脚分配情况

| 信号名称 | 描述    | PGL22G 管脚 |

|------|-------|-----------|

| D1_N | 差分 IO | K17       |

| D1_P | 差分 IO | K18       |

| D2_N | 差分 IO | L17       |

| D2_P | 差分 IO | L18       |

| D3_N | 差分 IO | M17       |

| D3_P | 差分 IO | M18       |

| D4_N | 差分 IO | N17       |

| D4_P | 差分 IO | N18       |

| D5_N | 差分 IO | L14       |

| D5_P | 差分 IO | L15       |

| D6_N | 差分 IO | K15       |

| D6_P | 差分 IO | K14       |

| D7_N | 差分 IO | J16       |

| D7_P | 差分 IO | H16       |

| D8_N | 差分 IO | G17       |

| D8_P | 差分 IO | G18       |

### 2.3.3 扩展 IO 接口

MES22GP 板上通过 1 个 2\*20 PIN 简牛座连出了 17 对差分信号，其中有两队是差分时钟引脚，用户可自定义扩展 IO 的应用接口；

下表显示了 PGL22G 与 40 PIN 扩展 IO 的管脚连接。

表 2.8 PGL22G 引脚分配情况

| 信号名称      | 描述           | PGL22G 管脚 |

|-----------|--------------|-----------|

| EX_IO_1N  | 差分 IO        | T10       |

| EX_IO_1P  | 差分 IO        | R10       |

| EX_IO_2N  | 差分 IO        | V10       |

| EX_IO_2P  | 差分 IO        | U10       |

| EX_IO_3N  | 差分 IO        | V13       |

| EX_IO_3P  | 差分 IO        | U13       |

| EX_IO_4N  | 差分 IO        | V12       |

| EX_IO_4P  | 差分 IO        | U12       |

| EX_IO_5N  | 差分 IO        | V11       |

| EX_IO_5P  | 差分 IO        | U11       |

| EX_IO_6N  | 差分 IO        | T11       |

| EX_IO_6P  | 差分 IO        | R11       |

| EX_IO_7N  | 差分 IO，可作时钟信号 | T17       |

| EX_IO_7P  | 差分 IO，可作时钟信号 | T18       |

| EX_IO_8N  | 差分 IO，可作时钟信号 | R18       |

| EX_IO_8P  | 差分 IO，可作时钟信号 | R17       |

| EX_IO_9N  | 差分 IO        | U17       |

| EX_IO_9P  | 差分 IO        | U18       |

| EX_IO_10N | 差分 IO        | V17       |

| EX_IO_10P | 差分 IO        | V18       |

| EX_IO_11N | 差分 IO        | P18       |

| EX_IO_11P | 差分 IO        | P17       |

| EX_IO_12N | 差分 IO        | T16       |

|           |       |     |

|-----------|-------|-----|

| EX_IO_12P | 差分 IO | R16 |

| EX_IO_13N | 差分 IO | V14 |

| EX_IO_13P | 差分 IO | U14 |

| EX_IO_14N | 差分 IO | V15 |

| EX_IO_14P | 差分 IO | U15 |

| EX_IO_15N | 差分 IO | U16 |

| EX_IO_15P | 差分 IO | V16 |

| EX_IO_16N | 差分 IO | R15 |

| EX_IO_16P | 差分 IO | R14 |

| EX_IO_17N | 差分 IO | T13 |

| EX_IO_17P | 差分 IO | R13 |

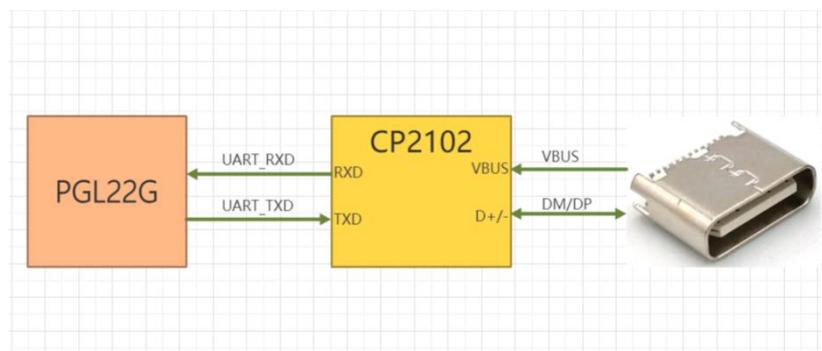

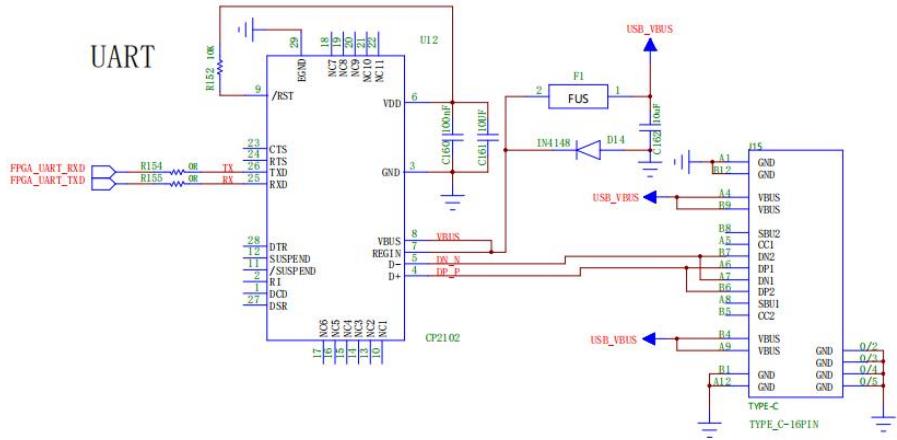

### 2.3.4 串口

MES22GP 开发板上集成了一路 USB 转串口模块，采用的 USB-UART 芯片是 CP2102，USB 接口采用 USB Type C 接口，可以用一根 USB Type C 线将它连接到上 PC 的 USB 口进行串口数据通信。

USB Uart 电路设计的示意图如下图所示：

图 2.11 USB-UART 原理框图

表 2.9 UART 引脚

| 信号            | 描述        | PGL22G |

|---------------|-----------|--------|

| FPGA_UART_RXD | Uart 数据输入 | F11    |

| FPGA_UART_TXD | Uart 数据输出 | G11    |

图 2.12 USB-UART 电路

## 2.4 HDMI

### 2.4.1 HDMI 输入接口

HDMI 输入接口的实现, 选用了国产宏晶微公司的 MS7200 HDMI 接收芯片, 兼容 HDMI1.4b 及 HDMI 1.4b 下标准视频的 3D 传输格式。支持的最高分辨率高达 4K@30Hz, 最高采样率达到 300MHz; MS7200 支持 YUV 和 RGB 之间的色彩空间转换, 数字接口支持 YUV 及 RGB 格式输出;

MS7200 支持通过 IIS 总线或 SPDIF 传输高清音频，同时还支持高比特音频（HBR）音频，在 HBR 模式下，音频采样率最高为 768KHz。

其中, MS7200 的 IIC 配置接口与 FPGA 的 IO 相连, 通过 FPGA 的编程来对 MS7200 进行初始化和控制操作, MES22GP 开发板上将 MS7200 的 SA 管脚下拉到地, 故 IIC 的 ID 地址为 0x56;

HDMI 输入接口的硬件连接如下图所示。

图 2.13 HDMI Receiver 连接示意图

具体管脚分配请看下表：

表 2.10 HDMI 管脚分配

| 信号         | 功能描述               | PGL22G Pin |

|------------|--------------------|------------|

| HD_RX_PCLK | HDMI 显示图像像素时钟      | A16        |

| HD_RX_VS   | HDMI 显示图像帧同步信号     | A18        |

| HD_RX_HS   | HDMI 显示图像行同步信号     | B18        |

| HD_RX_DE   | HDMI 显示图像有效像素点使能信号 | C18        |

| HD_RX_D0   | HDMI 显示图像像素点数据位[0] | D18        |

| HD_RX_D1   | HDMI 显示图像像素点数据位[1] | E18        |

| HD_RX_D2   | HDMI 显示图像像素点数据位[2] | A17        |

| HD_RX_D3   | HDMI 显示图像像素点数据位[3] | B17        |

| HD_RX_D4   | HDMI 显示图像像素点数据位[4] | C17        |

| HD_RX_D5   | HDMI 显示图像像素点数据位[5] | E15        |

| HD_RX_D6   | HDMI 显示图像像素点数据位[6] | A15        |

| HD_RX_D7   | HDMI 显示图像像素点数据位[7] | B15        |

| HD_RX_D8   | HDMI 显示图像像素点数据位[8] | C15        |

|             |                                    |     |

|-------------|------------------------------------|-----|

| HD_RX_D9    | HDMI 显示图像像素点数据位[9]                 | G12 |

| HD_RX_D10   | HDMI 显示图像像素点数据位[10]                | D15 |

| HD_RX_D11   | HDMI 显示图像像素点数据位[11]                | A14 |

| HD_RX_D12   | HDMI 显示图像像素点数据位[12]                | B14 |

| HD_RX_D13   | HDMI 显示图像像素点数据位[13]                | A13 |

| HD_RX_D14   | HDMI 显示图像像素点数据位[14]                | B13 |

| HD_RX_D15   | HDMI 显示图像像素点数据位[15]                | C13 |

| HD_RX_D16   | HDMI 显示图像像素点数据位[16]                | D13 |

| HD_RX_D17   | HDMI 显示图像像素点数据位[17]                | A12 |

| HD_RX_D18   | HDMI 显示图像像素点数据位[18]                | B12 |

| HD_RX_D19   | HDMI 显示图像像素点数据位[19]                | E11 |

| HD_RX_D20   | HDMI 显示图像像素点数据位[20]                | F12 |

| HD_RX_D21   | HDMI 显示图像像素点数据位[21]                | A11 |

| HD_RX_D22   | HDMI 显示图像像素点数据位[22]                | B11 |

| HD_RX_D23   | HDMI 显示图像像素点数据位[23]                | C11 |

| HD_SCL      | MS7200 控制通道 IIC 的时钟信号              | E17 |

| HD_SDA      | MS7200 控制通道 IIC 的数据信号              | D17 |

| HD_RX_SC_MC | MS7200 音频通道 I2S 的串行时钟信号            | A10 |

| HD_RX_MU_MC | MS7200 音频通道 I2S 的主时钟信号或<br>Mute 信号 | D10 |

| HD_RX_I2S1  | MS7200 音频通道 I2S 的数据通道 1            | B10 |

| HD_RX_I2S0  | MS7200 音频通道 I2S 的数据通道 0            | C10 |

| HD_RX_WS_SP | MS7200 音频通道 I2S 的位时钟               | D11 |

| HD_RX_RSTN  | MS7200 硬件复位信号, 低电平有效               | E16 |

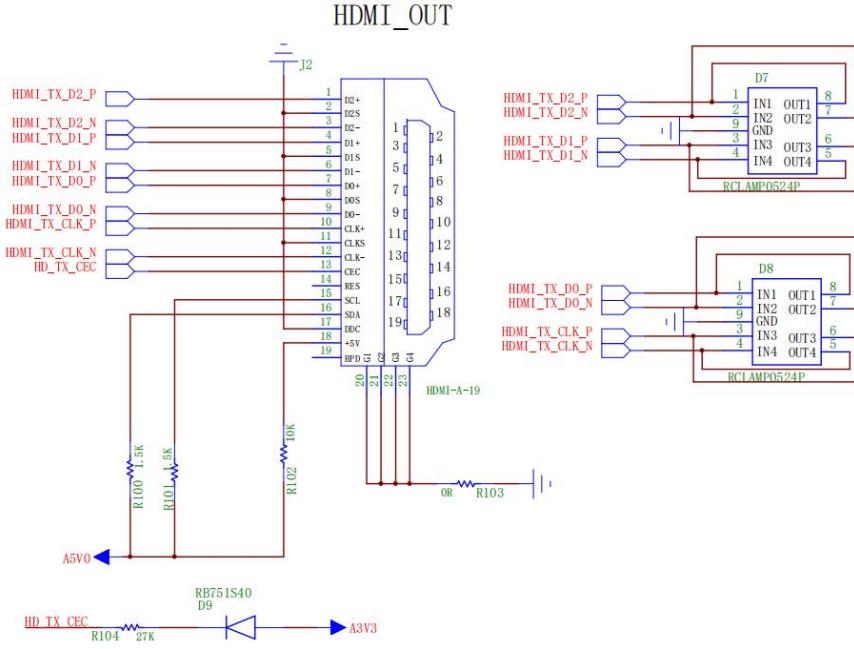

#### 2.4.2 HDMI 输出接口

HDMI 输出接口的硬件连接如下图所示。

图 2.14 HDMI 输出原理图

具体管脚分配请看下表：

表 2.11 HDMI 管脚分配

| 信号            | 功能描述               | PGL22G Pin |

|---------------|--------------------|------------|

| HDMI_TX_D0_P  | HDMI 显示图像像素时钟      | F16        |

| HDMI_TX_D0_N  | HDMI 显示图像帧同步信号     | G16        |

| HDMI_TX_D1_P  | HDMI 显示图像行同步信号     | F14        |

| HDMI_TX_D1_N  | HDMI 显示图像有效像素点使能信号 | F13        |

| HDMI_TX_D2_P  | HDMI 显示图像像素点数据位[0] | G14        |

| HDMI_TX_D2_N  | HDMI 显示图像像素点数据位[1] | G13        |

| HDMI_TX_CLK_P | HDMI 显示图像像素点数据位[2] | F18        |

| HDMI_TX_CLK_N | HDMI 显示图像像素点数据位[3] | F17        |

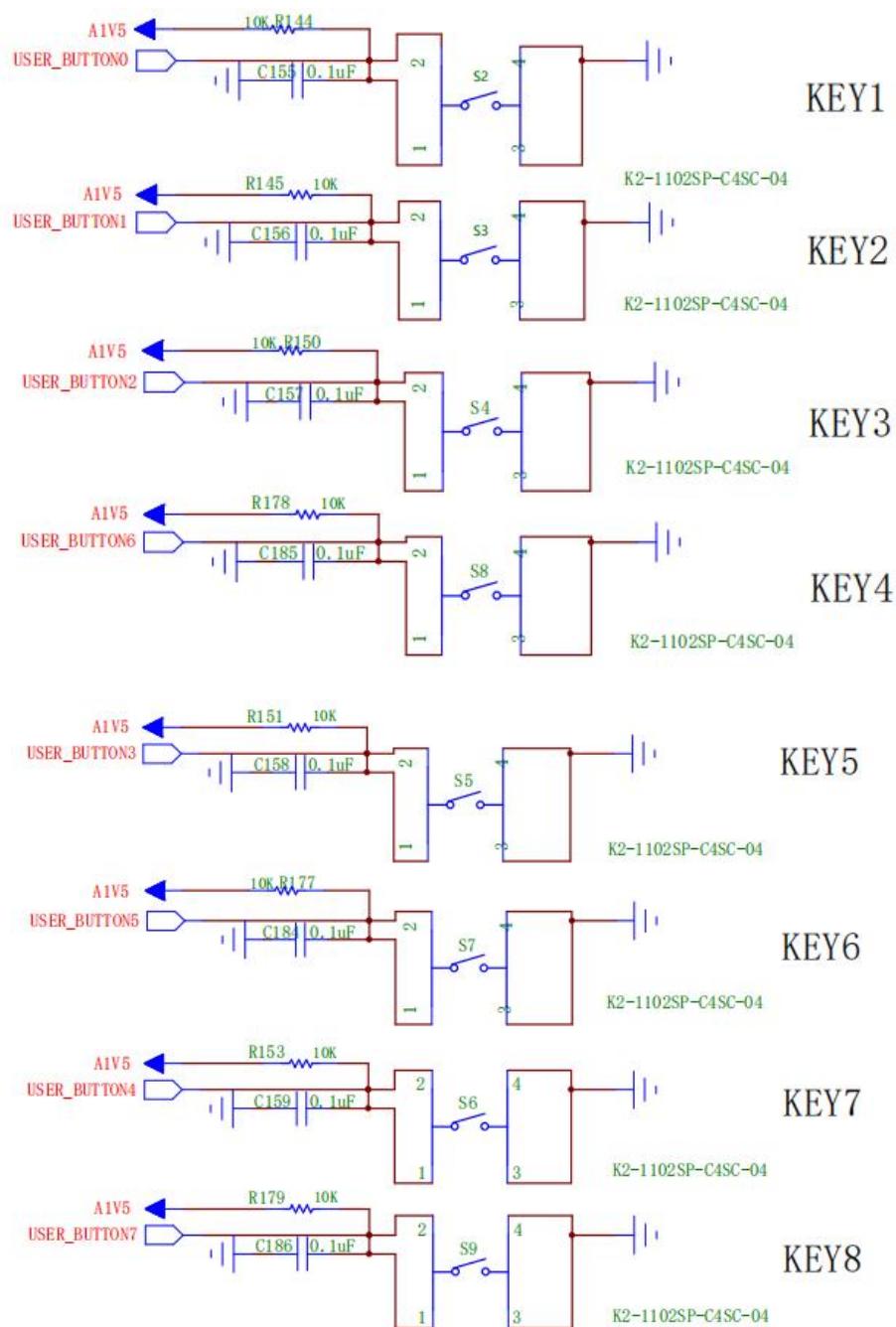

## 2.5 按键开关及指示灯

### 2.5.1 按键

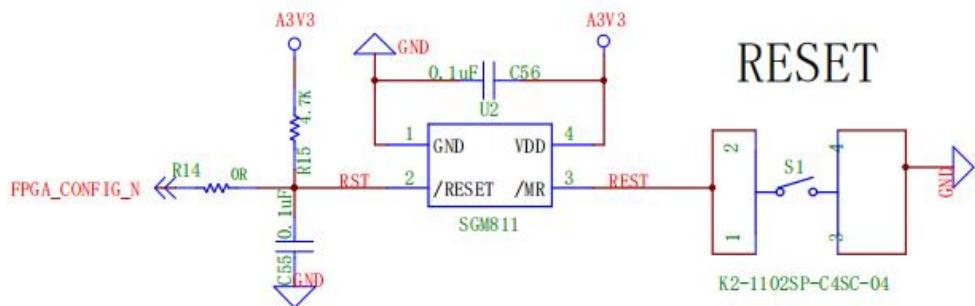

MES22GP 开发板提供了 8 个用户按键 (K1~8)；1 个重加载复位按键，重加载按键通过一个延时复位芯片连接到 PGL22G 的 RSTN 管脚；8 个用户按键都连接到 PGL22G 的普通 IO 上，按键低电平有效，但按键按下时，IO 上的输入电压为低；当没有按下按键时，IO 上的输入电压为高电平；

图 2.15 用户按键电路图

具体管脚分配如下：

表 2.12 按键管脚分配

| 信号   | PGL22G Pin |

|------|------------|

| REST | 重新加载固件按键   |

| KEY1 | J3         |

| KEY2 | H1         |

| KEY3 | H3         |

| KEY4 | F1         |

| KEY5 | H5         |

| KEY6 | G3         |

| KEY7 | G1         |

| KEY8 | F3         |

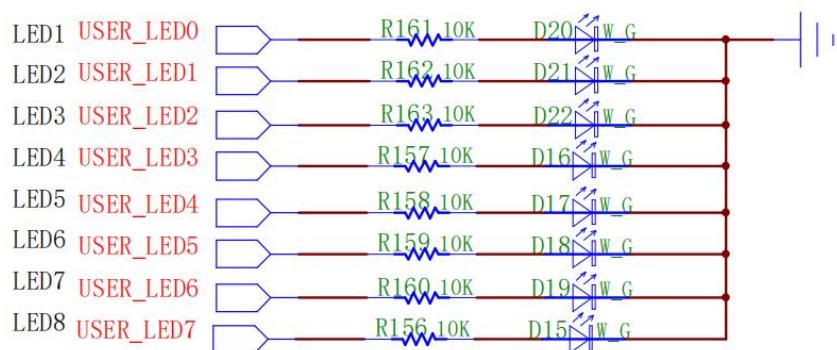

### 2.5.2 Led 灯

MES22GP 开发板有 11 个翠绿 LED 灯，其中 1 个是电源指示灯 (POWER)；2 个是 FPGA 的运行的状态指示灯：INIT 和 DONE；8 个是用户 LED 灯 (LED1~8)。连接在 PGL22G BANK L3 的 IO 上，FPGA 输出高电平时对应的 LED 灯亮灯，板上 LED 灯功能电路图：

图 2.16 LED 灯电路原理图

具体管脚分配请看下表：

表 2.13 LED 灯

| 信号   | PGL22G Pin |

|------|------------|

| LED1 | E5         |

| LED2 | E6         |

| LED3 | F7         |

| LED4 | F8         |

| LED5 | E8         |

| LED6 | D8         |

| LED7 | C8         |

| LED8 | A8         |

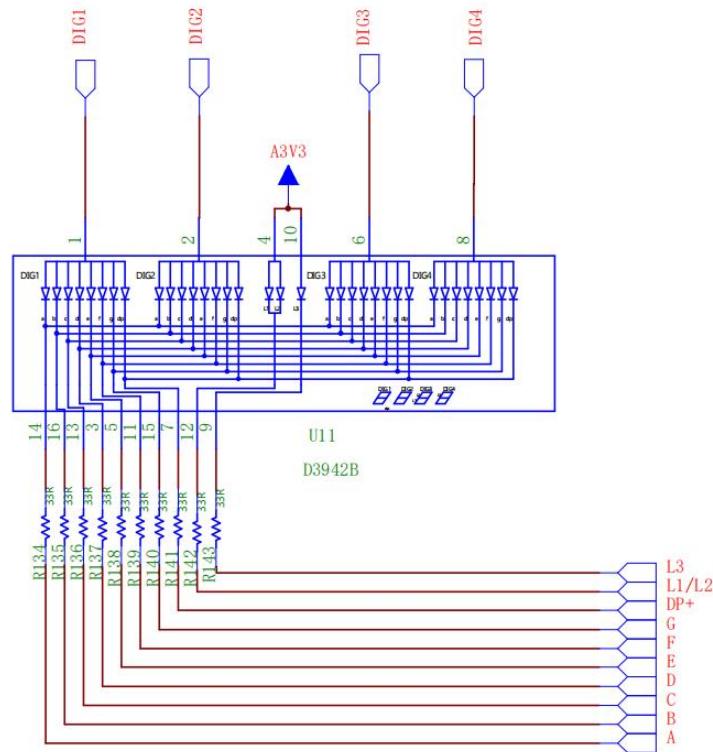

### 2.5.3 数码管

4 位 8 段共阳数码管的管脚及段选原理图如下图：

图 2.17 数码管电路原理图

表 2.14 数码管灯

| 信号 | PGL22G Pin | 信号    | PGL22G Pin |

|----|------------|-------|------------|

| A  | J14        | DP+   | M16        |

| B  | H13        | L1/L2 | N15        |

| C  | J15        | L3    | M13        |

| D  | L12        | DIG1  | H17        |

| E  | L16        | DIG2  | J17        |

| F  | M14        | DIG3  | L13        |

| G  | H14        | DIG4  | N16        |

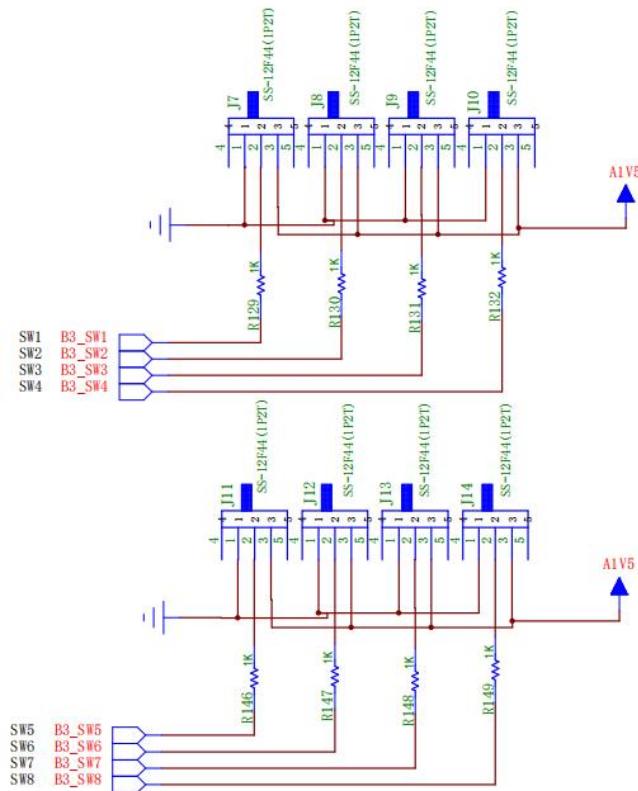

#### 2.5.4 拨动开关

MES22GP 开发板板卡上有 8 个的拨动开关，电路设计上 IO 默认识别低电平， 拨动开关拨通后为高电平，电路如下图：

图 2.18 拨动开关原理图

表 2.15 拨动开关

| 信号  | PGL22G Pin |

|-----|------------|

| SW1 | J5         |

| SW2 | H2         |

| SW3 | J6         |

| SW4 | H6         |

| SW5 | G2         |

| SW6 | G5         |

| SW7 | F2         |

| SW8 | G6         |