## 29. 音频回环实验例程说明

### 29.1. 实验简介

FPGA 具有丰富的可编程资源，能够高速并行的处理数据，使得 FPGA 在实时处理音频数据方面，有很大的优势。

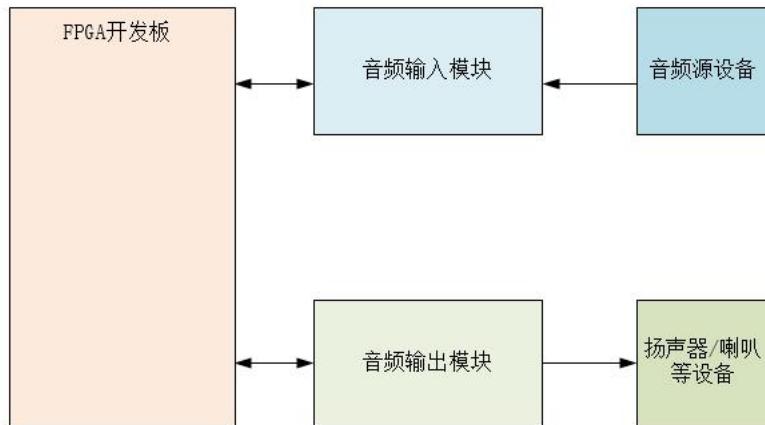

由于 FPGA 处理的是数字信号，麦克风等音频源设备接收的是模拟信号，因此如果我们想使用 FPGA 对音频进行处理，我们需要使用音频输入模块，将音频模拟信号转化为音频数字信号，再使用 FPGA 对音频数字信号(音频数据)进行处理。同样，在输出音频数据的时候，我们也需要使用音频输出模块，将音频数字信号转化为音频模拟信号，再通过扬声器将音频模拟信号播出。

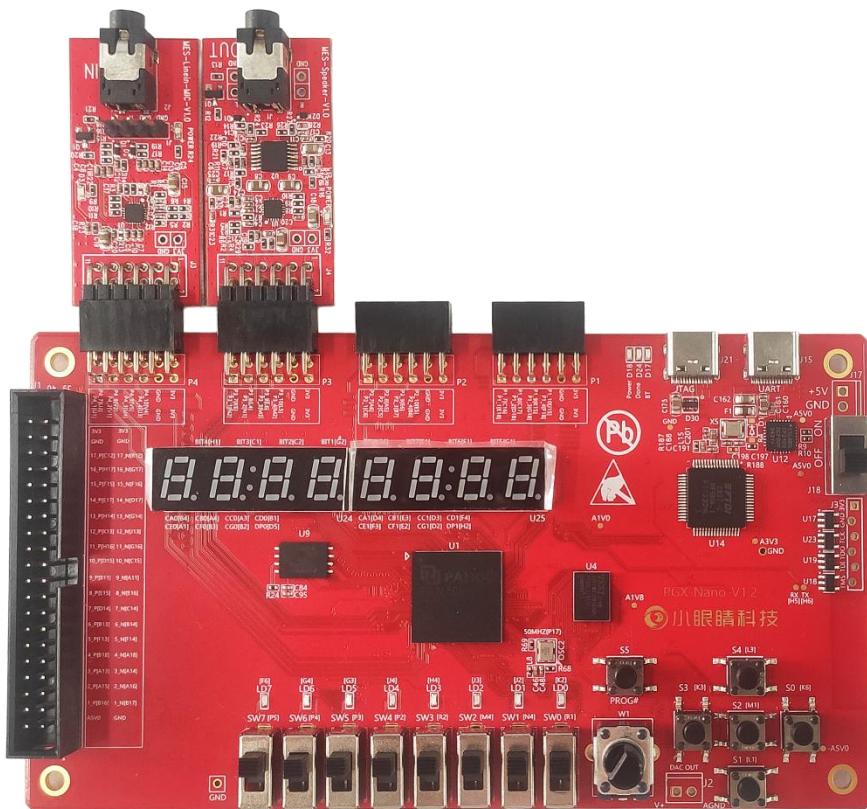

实验将使用 FPGA 开发板、音频输入模块，音频输出模块，完成音频环路实验。

实验框图：

### 29.2. 实验目的

音频环路实验：将音频输入至 FPGA 中，再将 FPGA 中的音频数据输出。

## 29.3. 实验器材介绍

### 29.3.1. 音频输入模块:

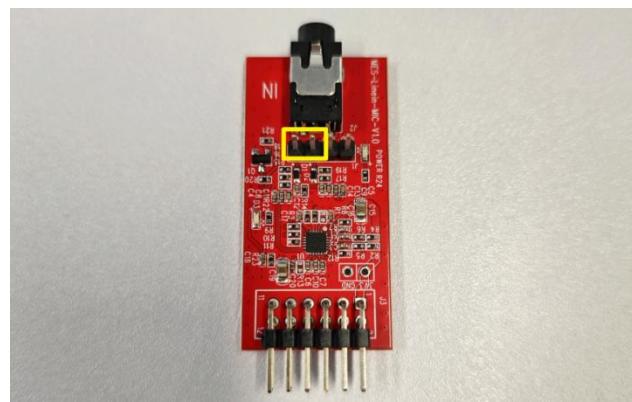

音频输入模块采用 ES7243E 音频芯片，将输入的音频模拟信号转为符合 I2S 音频协议的数字信号传输给 FPGA，此时我们就可以使用 FPGA 处理音频数据了。在模块使用时需要先对音频芯片进行寄存器配置。音频输入需要 3.5mm 三环音频接头，输入源可以为 PC 端、麦克风等。

需注意的是，麦克风输入的音频信号一般只有一个声道，此时如果不做任何处理，输出的也将只会有一个声道，考虑到这种情况，音频模块可以使用跳线帽扣在音频输入模块上最左侧的两个跳线针上，在电路上将左声道与右声道连接，此时音频输入模块左右两通道将都有信号输入。

例程中，对 E7243E 音频芯片的配置参数如下所示，如果需要更改配置，请仔细参考 **ES7243E** 芯片数据手册。

**ES7243E:**

- 1、模式：master（LRCK 与 SCLK 由 ES7243E 输出）

- 2、音频采样率：48KHz

- 3、数据位宽：16bit

- 4、MCLK：12.288MHz（由 FPGA 提供）

### 29.3.2. 音频输出模块

音频输出模块采用 ES8156 音频芯片，它将 FPGA 输出的遵循 i2s 协议的音频数据转换为音频模拟信号，由音响等扬声器设备播放。在音频输出模块使用时同样需要对 ES8156 音频芯片进行寄存器配置。音频输入需要 3.5mm 三环音频接头。

例程中，对 ES8156 音频芯片的配置参数如下所示，如果需要更改参数，请仔细参考 [ES8156 数据手册](#)。

ES8156:

- 5、模式：master（LRCK 与 SCLK 由 ES8156 输出）

- 6、音频采样率：48KHz

- 7、数据位宽：16bit

- 8、MCLK：12.288MHz（由 FPGA 提供）

## 29.4. 实验代码设计

顶层 module 下共有 5 个模块，具体功能如下表所示，完整代码请参考实验对应 demo。

| 模块名称               | 模块功能                |

|--------------------|---------------------|

| PLL                | 生成 Master clock     |

| ES7243E_reg_config | ES7243E 芯片 i2c 配置模块 |

| ES8156_reg_config  | ES8156 芯片 i2c 配置模块  |

| ES7243_i2s_rx      | 音频数据接收模块            |

| i2s_loop           | 音频环回模块              |

| ES8156_i2s_tx      | 音频数据发送模块            |

## 29.5. 实验器件连接

例程中，音频输入模块需接在 PGX-Nano 开发板 PMOD\_4 位置，音频输出模块需接在 PMOD\_3 位置。

## 29.6. 实验管脚分配

| PMOD-4（音频输入模块连接位置） |       |             |           |        |             |

|--------------------|-------|-------------|-----------|--------|-------------|

| 信号名称               | 网络名称  | PGX-Nano 管脚 | 信号名称      | 网络名称   | PGX-Nano 管脚 |

| LED_TEST           | PM4_1 | U1          | LIN_TEST  | PM4_7  | U2          |

| ES0_ALRCK          | PM4_2 | V1          | ES0_DSCLK | PM4_8  | V2          |

| ES0_ASOUT          | PM4_3 | U4          | ES0_MCLK  | PM4_9  | V5          |

| I2C_DATA           | PM4_4 | U3          | I2C_CLK   | PM4_10 | V4          |

| PMOD-3（音频输出模块连接位置） |       |             |           |        |             |

|--------------------|-------|-------------|-----------|--------|-------------|

| 信号名称               | 网络名称  | PGX-Nano 管脚 | 信号名称      | 网络名称   | PGX-Nano 管脚 |

| ES1_ASOUT          | PM3_1 | N2          | LOUT_TEST | PM3_7  | K5          |

| I2C_DATA           | PM3_2 | N1          | I2C_CLK   | PM3_8  | L4          |

| ES1_MCLK           | PM3_3 | M3          | ES1_DSCLK | PM3_9  | L6          |

| ES1_DSDIN          | PM3_4 | M2          | ES1_ALRCK | PM3_10 | L5          |

## 29.7. 补充说明

- 1、模块不支持四环音频接头作为麦克风等音频源的输入接头。

## 29.8. 实验现象

将音频模块与 FPGA 开发板相连，音频输入模块连接音频源，音频输出模块连接扬声器，烧录程序后，使用音频源播放音乐，可以从扬声器听到相应音乐。