# MES1/2KG 开发板

## 硬件使用说明手册

深圳市小眼睛半导体科技有限公司

2022.10.12

## 版本记录

| 日期         | 版本   | 修改原因 |

|------------|------|------|

| 2022.10.12 | V1.0 | 创建文档 |

|            |      |      |

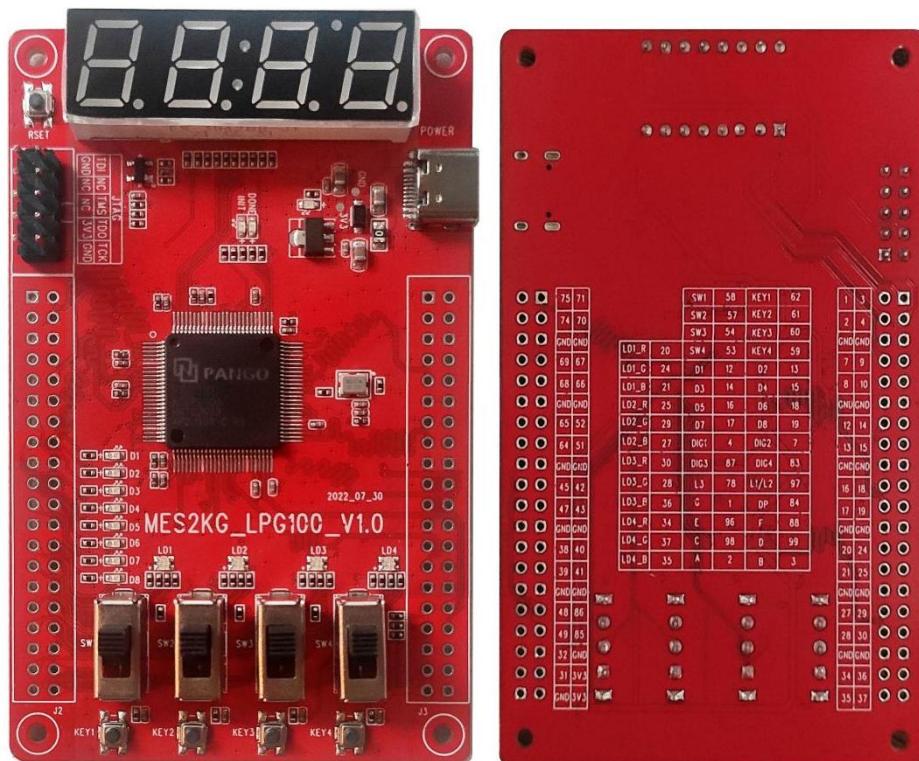

## 1 开发板简介

### 1.1 概述

MES1/2KG 开发板是一套基于紫光 FPGA 的开发套件，以紫光 Compact 系列 PGC1KG-LPG100 / PGC2KG-LPG100 器件为核心，预留丰富的扩展 IO 及数码管、按键、LED 灯，为用户提供基本的硬件环境。

本开发系统开源原理图及参考例程的源代码。

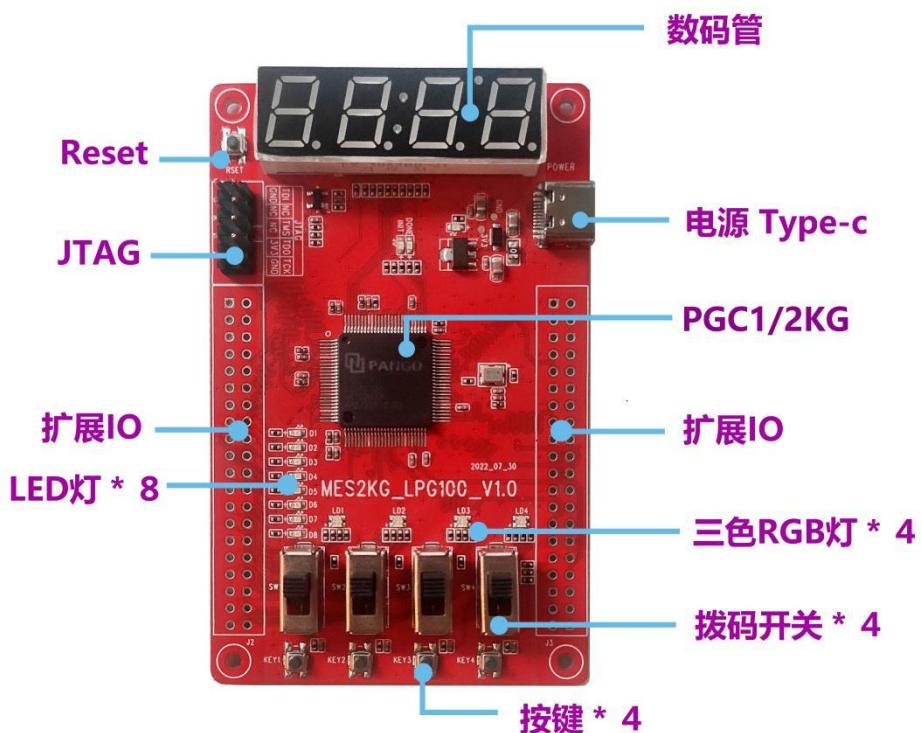

图 1.1 MES1/2KG 开发板

### 1.2 开发系统简介

#### 1.2.1 系统资源

MES1/2KG 开发板是基于紫光 PGC1KG/PGC2KG 的可扩展处理平台的开发套件。提供的功能包括：

- ◎ 紫光同创 FPGA: PGC1K/PGC2K

- 启动方式: 支持内置 flash

|          | 器件型号 <sup>1</sup>                       | PGC1K           | PGC2K | PGC4K | PGC7K | PGC10K |

|----------|-----------------------------------------|-----------------|-------|-------|-------|--------|

| 逻辑资源     | 等效 LUT4                                 | 1276            | 2428  | 4761  | 7104  | 9907   |

|          | Flip-Flop (个)                           | 1596            | 3036  | 5952  | 8880  | 12384  |

| RAM 资源   | 分布式 RAM (Kbit)                          | 11              | 16    | 39    | 56    | 78     |

|          | 内嵌 9K 块 RAM (个)                         | 7               | 8     | 11    | 26    | 45     |

|          | 块存储器 (Kbit)                             | 63              | 72    | 99    | 234   | 405    |

| Flash 资源 | 用户可用嵌入式 Flash 最大容量 (Kbits) <sup>2</sup> | 80 <sup>3</sup> | 80    | 1520  | 2070  | 3016   |

| 时钟资源     | 锁相环 PLL/Global Clock                    | 1/16            | 1/16  | 2/16  | 2/16  | 2/16   |

| I/O 资源   | IO Banks                                | 4               | 6     | 6     | 6     | 6      |

|          | 最大用户 I/O                                | 207             | 207   | 280   | 336   | 384    |

|          | 最大差分对                                   | 14              | 14    | 18    | 21    | 24     |

| 硬核资源     | I2C 硬核                                  | 2               | 2     | 2     | 2     | 2      |

|          | SPI 硬核                                  | 1               | 1     | 1     | 1     | 1      |

|          | 定时器/计数器 硬核                              | 1               | 1     | 1     | 1     | 1      |

|          | 片上振荡器                                   | 1               | 1     | 1     | 1     | 1      |

### ◎ 外设/接口

- Type-c 口 (电源接口)

- Jtag 接口 (调试接口)

- 4 位 8 段共阳数码管

- 4 位拨码开关

- 8 位 LED 灯

- 4 位按键

- 4 个三色 RGB 灯 (共阳)

- 54 个扩展 IO 口 (2.54 间距排针)

### ◎ 板上晶振

- 50MHz

## 2 接口描述

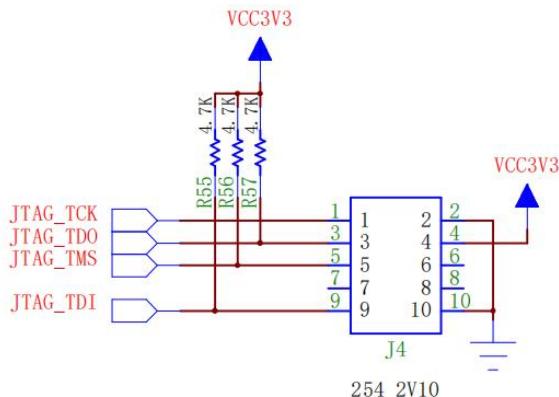

### 2.1 JTAG

MES1/2KG 板卡上的 Jtag 原理图如图

通过板上的 J4 (2.54MM 2\*5PIN 双排针) 需与紫光 jtag 下载器连接进行烧录。紫光同创下载器链接：

<https://item.taobao.com/item.htm?spm=a21dvs.23580594.0.0.1d293d0dN6yth2&ft=t&id=687149863298>

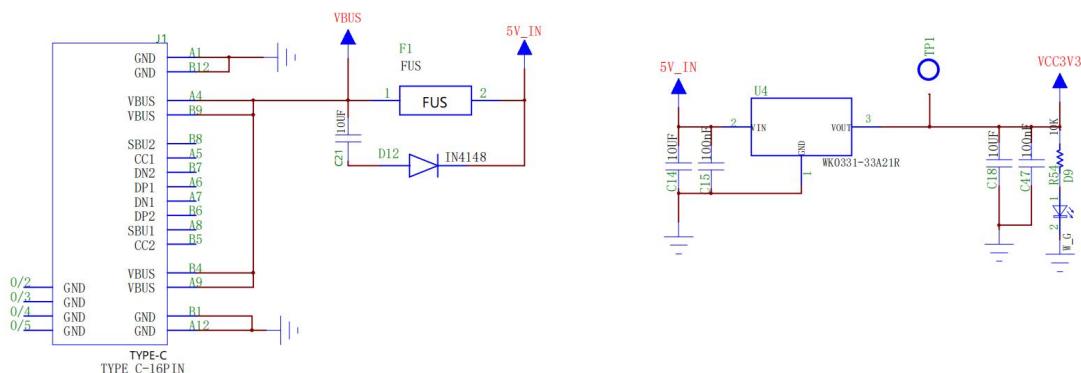

## 2.2 电源

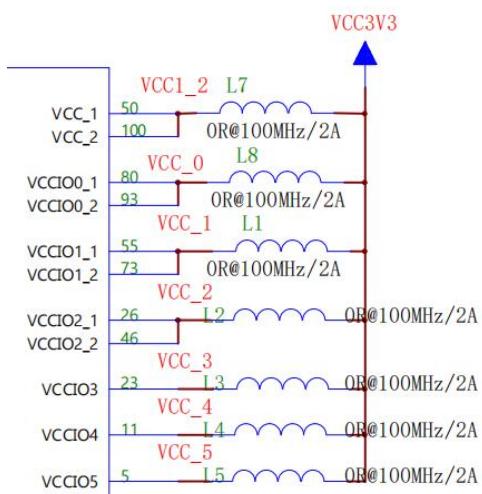

板卡使用 USB 接口上的 VBUS 供电，使用一个 LDO 得到 3.3V 电源

板上使用的 PGC1K/PGC2K，电源均支持 3.3V 供电，简化了板卡的电源网络。

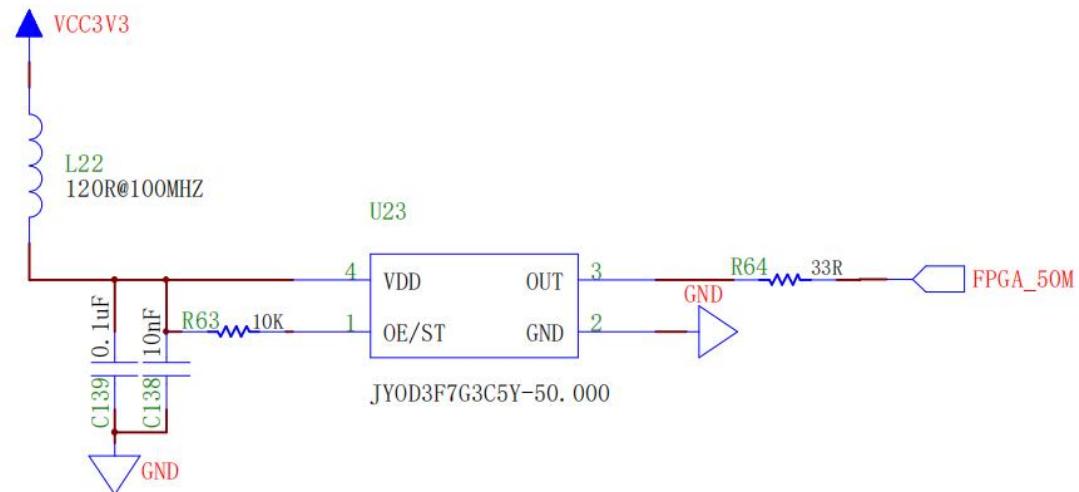

## 2.3 时钟

MES1/2KG 板卡上使用了一个 50MHz 晶振给 PGC1K/PGC2K 提供时钟。

连接 GW1N-4 的管脚如下表：

| 信号              | 描述         | FPGA 管脚 |

|-----------------|------------|---------|

| <b>FPGA_50M</b> | 50MHz 时钟输入 | 63      |

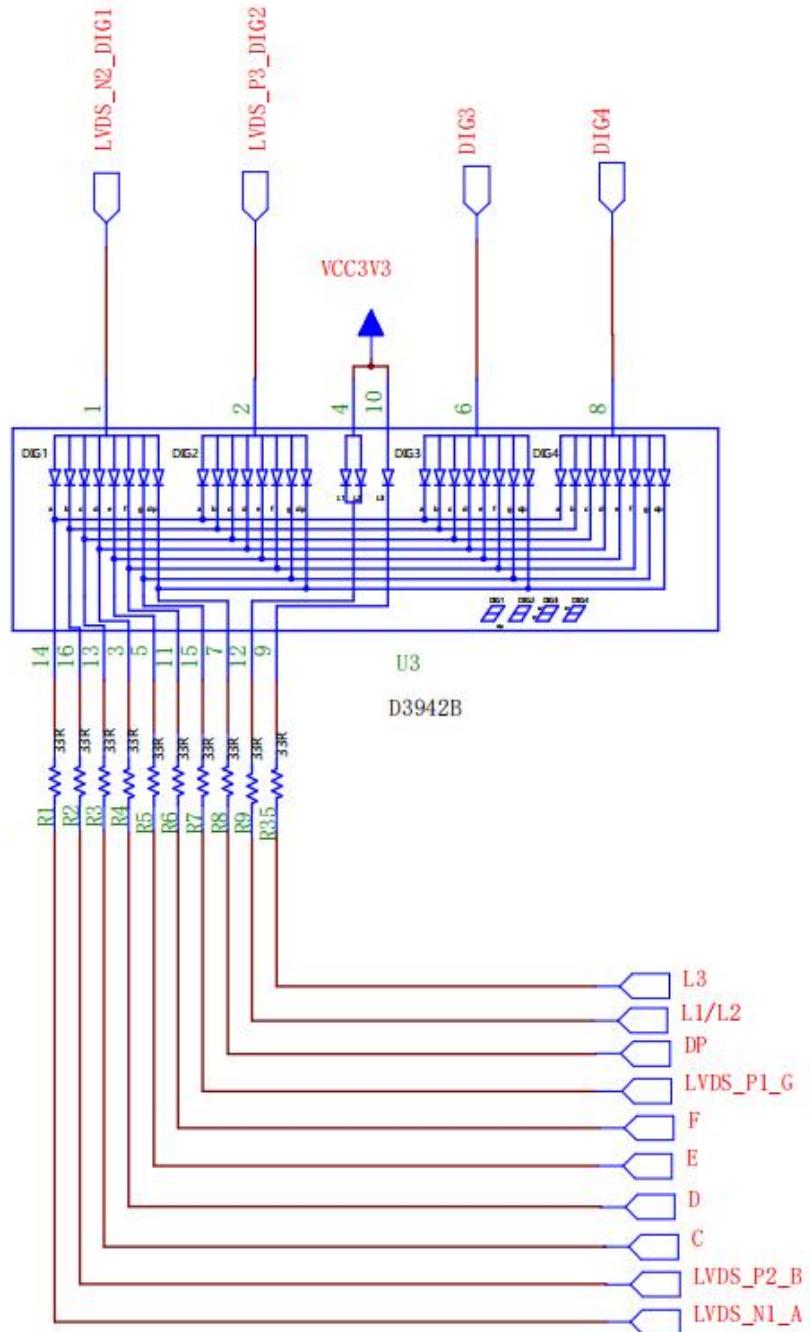

## 2.4 共阳数码管

4 位 8 段数码管的管脚及段选原理图如下图

连接 PGC1K/PGC2K 的管脚如下表：

| 信号              | 描述          | FPGA 管脚 |

|-----------------|-------------|---------|

| <b>SEG_DIG1</b> | 左侧起第一位数码管位选 | 4       |

| <b>SEG_DIG2</b> | 左侧起第二位数码管位选 | 7       |

| <b>SEG_DIG3</b> | 左侧第三位数码管位选  | 87      |

| <b>SEG_DIG4</b> | 左侧第四位数码管位选  | 83      |

|               |           |    |

|---------------|-----------|----|

| <b>SEG_A</b>  | 数码管段选 A   | 2  |

| <b>SEG_B</b>  | 数码管段选 B   | 3  |

| <b>SEG_C</b>  | 数码管段选 C   | 98 |

| <b>SEG_D</b>  | 数码管段选 D   | 99 |

| <b>SEG_E</b>  | 数码管段选 E   | 96 |

| <b>SEG_F</b>  | 数码管段选 F   | 88 |

| <b>SEG_G</b>  | 数码管段选 G   | 1  |

| <b>SEG_DP</b> | 数码管段选 DP  | 84 |

| <b>L1/L2</b>  | 数码管 L1/L2 | 97 |

| <b>L3</b>     | 数码管 L3    | 78 |

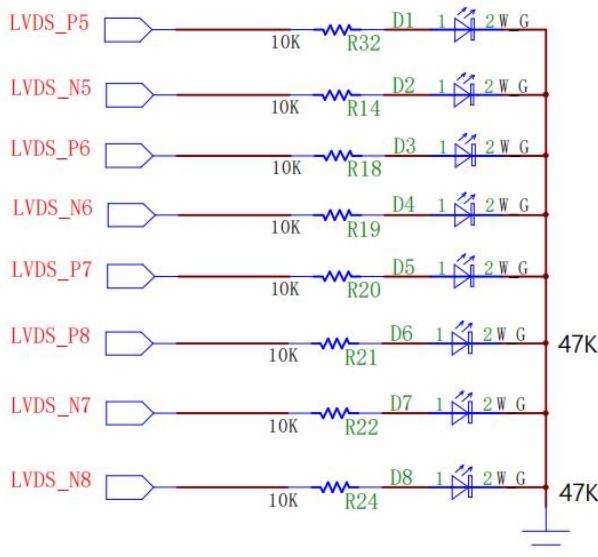

## 2.5 单色 LED 灯

MES1/2KG 板卡上有 8 个 LED 灯供 IO 控制，另有一个电源指示灯在 Type-c 座旁边，与初始化（INIT）、配置状态（DONE）指示灯。

8 个可控的 LED 灯高电平可点亮 LED 灯，电路图与管脚连接如下：

| 信号          | 描述        | FPGA 管脚 |

|-------------|-----------|---------|

| <b>LED1</b> | LED1 控制信号 | 12      |

| <b>LED2</b> | LED2 控制信号 | 13      |

| <b>LED3</b> | LED3 控制信号 | 14      |

|             |           |    |

|-------------|-----------|----|

| <b>LED4</b> | LED4 控制信号 | 15 |

| <b>LED5</b> | LED5 控制信号 | 16 |

| <b>LED6</b> | LED6 控制信号 | 18 |

| <b>LED7</b> | LED7 控制信号 | 17 |

| <b>LED8</b> | LED8 控制信号 | 19 |

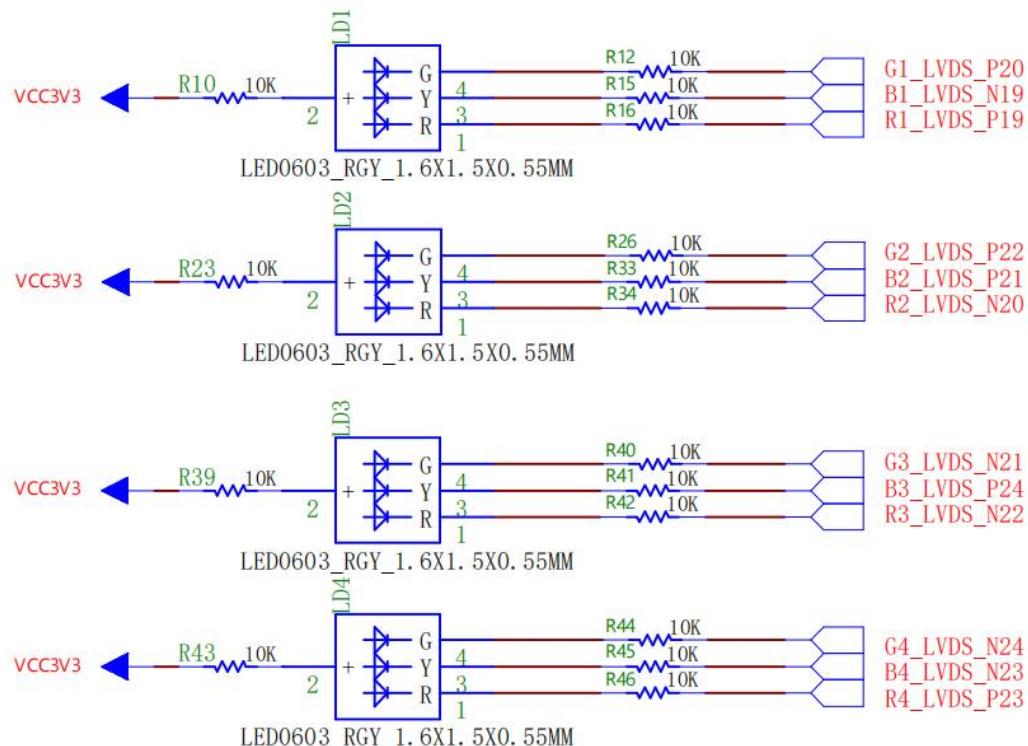

## 2.6 三色 LED 灯

MES1/2KG 板卡上有 4 个三色共阳 LED 灯，控制 IO 为低时 LED 亮起对应颜色。

| 信号            | 描述          | FPGA 管脚 |

|---------------|-------------|---------|

| <b>G_LED1</b> | G_LED1 控制信号 | 24      |

| <b>B_LED1</b> | B_LED1 控制信号 | 21      |

| <b>R_LED1</b> | R_LED1 控制信号 | 20      |

| <b>G_LED2</b> | G_LED2 控制信号 | 29      |

| <b>B_LED2</b> | B_LED2 控制信号 | 27      |

|               |             |    |

|---------------|-------------|----|

| <b>R_LED2</b> | R_LED2 控制信号 | 25 |

| <b>G_LED3</b> | G_LED3 控制信号 | 28 |

| <b>B_LED3</b> | B_LED3 控制信号 | 36 |

| <b>R_LED3</b> | R_LED4 控制信号 | 30 |

| <b>G_LED4</b> | G_LED4 控制信号 | 37 |

| <b>B_LED4</b> | B_LED4 控制信号 | 35 |

| <b>R_LED4</b> | R_LED4 控制信号 | 34 |

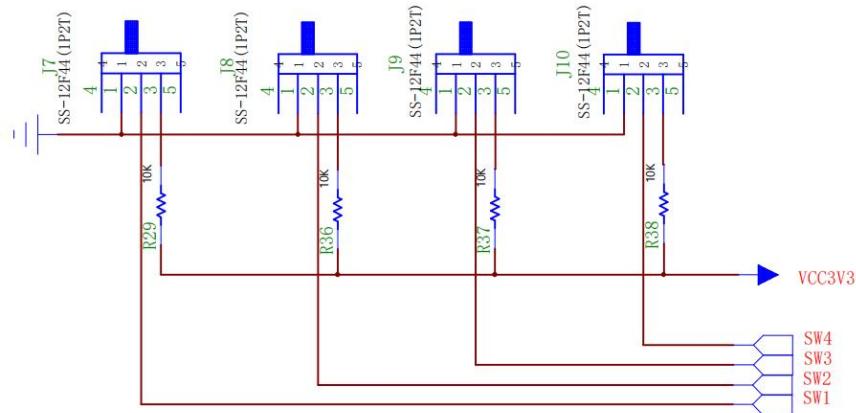

## 2.7 拨码开关

MES1/2KG 板卡上有一个 4 位的拨码开关，电路设计上 IO 默认识别低电平，拨码开关拨通后为高电平，电路如下图：

管脚连接如下表：

| 信号         | 描述       | FPGA 管脚 |

|------------|----------|---------|

| <b>SW1</b> | SW1 控制信号 | 58      |

| <b>SW2</b> | SW2 控制信号 | 57      |

| <b>SW3</b> | SW3 控制信号 | 54      |

| <b>SW4</b> | SW4 控制信号 | 53      |

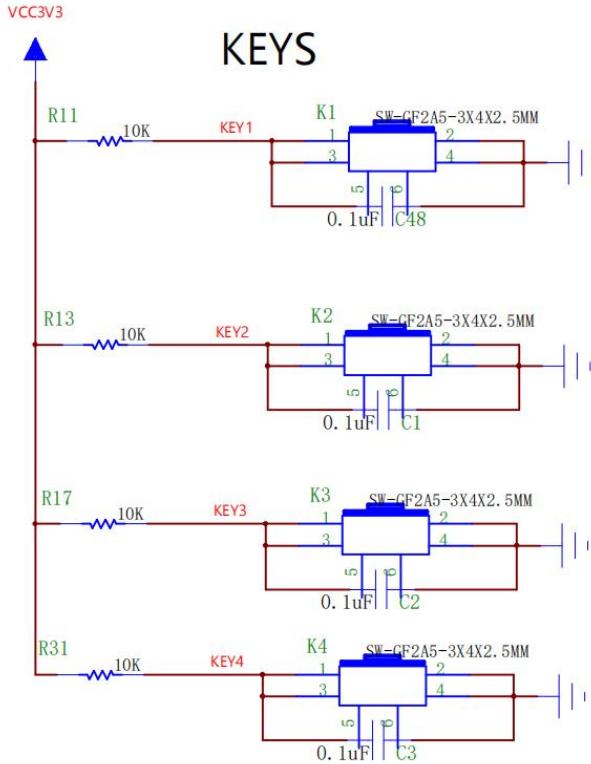

## 2.8 按键

MES1/2KG 板卡上有 4 个的轻触式按键，电路设计上 IO 默认识别高电平，按键按下后为低电平，电路如下图：

管脚连接如下表：

| 信号          | 描述        | FPGA 管脚 |

|-------------|-----------|---------|

| <b>KEY1</b> | KEY1 控制信号 | 62      |

| <b>KEY2</b> | KEY2 控制信号 | 61      |

| <b>KEY3</b> | KEY3 控制信号 | 60      |

| <b>KEY4</b> | KEY4 控制信号 | 59      |

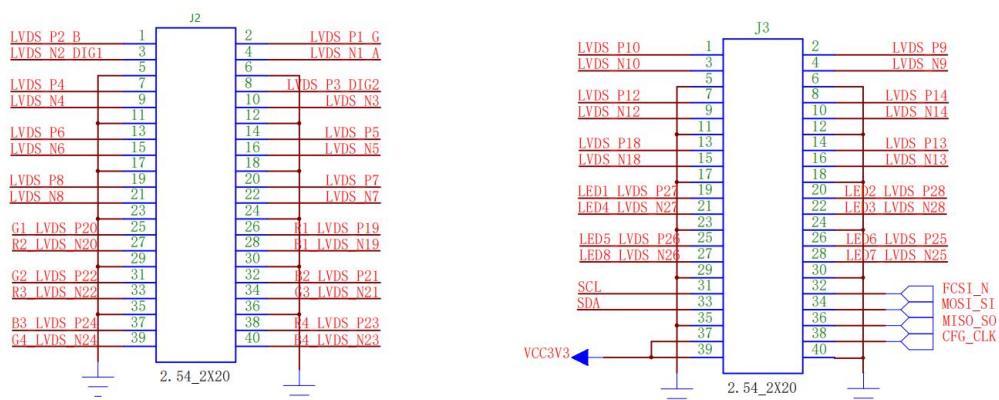

## 2.9 扩展 IO

MES1/2KG 板卡上预留两组 40pin 脚的排针口（2.54 间距）可供用户自行扩展使用，电路连接如下：

J2 位于数码管左侧

J2 的管脚连接如下：

| 序号        | FPGA 管脚 | 序号        | FPGA 管脚 |

|-----------|---------|-----------|---------|

| <b>1</b>  | 3       | <b>2</b>  | 1       |

| <b>3</b>  | 4       | <b>4</b>  | 2       |

| <b>5</b>  | GND     | <b>6</b>  | GND     |

| <b>7</b>  | 9       | <b>8</b>  | 7       |

| <b>9</b>  | 10      | <b>10</b> | 8       |

| <b>11</b> | GND     | <b>12</b> | GND     |

| <b>13</b> | 14      | <b>14</b> | 12      |

| <b>15</b> | 15      | <b>16</b> | 13      |

| <b>17</b> | GND     | <b>18</b> | GND     |

| <b>19</b> | 18      | <b>20</b> | 16      |

| <b>21</b> | 19      | <b>22</b> | 17      |

| <b>23</b> | GND     | <b>24</b> | GND     |

| <b>25</b> | 24      | <b>26</b> | 20      |

| <b>27</b> | 25      | <b>28</b> | 21      |

| <b>29</b> | GND     | <b>30</b> | GND     |

| <b>31</b> | 29      | <b>32</b> | 27      |

| <b>33</b> | 30      | <b>34</b> | 28      |

| <b>35</b> | GND     | <b>36</b> | GND     |

| <b>37</b> | 36      | <b>38</b> | 34      |

| <b>39</b> | 37      | <b>40</b> | 35      |

J3 位于数码管右侧

J3 的管脚连接如下：

| 序号        | FPGA 管脚 | 序号        | FPGA 管脚 |

|-----------|---------|-----------|---------|

| <b>1</b>  | 71      | <b>2</b>  | 75      |

| <b>3</b>  | 70      | <b>4</b>  | 74      |

| <b>5</b>  | GND     | <b>6</b>  | GND     |

| <b>7</b>  | 67      | <b>8</b>  | 69      |

| <b>9</b>  | 66      | <b>10</b> | 68      |

| <b>11</b> | GND     | <b>12</b> | GND     |

| <b>13</b> | 52      | <b>14</b> | 65      |

| <b>15</b> | 51      | <b>16</b> | 64      |

| <b>17</b> | GND     | <b>18</b> | GND     |

| <b>19</b> | 42      | <b>20</b> | 45      |

| <b>21</b> | 43      | <b>22</b> | 47      |

| <b>23</b> | GND     | <b>24</b> | GND     |

| <b>25</b> | 40      | <b>26</b> | 38      |

| <b>27</b> | 41      | <b>28</b> | 39      |

| <b>29</b> | GND     | <b>30</b> | GND     |

| <b>31</b> | 86      | <b>32</b> | 48      |

| <b>33</b> | 85      | <b>34</b> | 49      |

| <b>35</b> | GND     | <b>36</b> | 32      |

| <b>37</b> | 3.3V    | <b>38</b> | 31      |

| <b>39</b> | 3.3V    | <b>40</b> | GND     |

### 3 开发板使用注意事项

1. 开发板使用时，注意轻拿轻放，并做好静电防护。

2. 连接模块时，必须先断电。