# voice\_loop\_50 DEMO 说明文档

## 1、实验简介

FPGA 具有丰富的可编程资源，能够高速并行的处理数据，使得 FPGA 在实时处理音频数据方面，有很大的优势。

由于 FPGA 处理的是数字信号，麦克风等音频源设备接收的是模拟信号，因此如果我们想使用 FPGA 对音频进行处理，我们需要使用音频输入模块，将音频模拟信号转化为音频数字信号，再使用 FPGA 对音频数字信号(音频数据)进行处理。同样，在输出音频数据的时候，我们也需要使用音频输出模块，将音频数字信号转化为音频模拟信号，再通过扬声器将音频模拟信号播出。

实验将使用 MES50HP 开发板、PMOD 扩展板、音频输入模块，音频输出模块，完成音频环路实验。

音频环路实验：将音频输入至 FPGA 中，再将 FPGA 中的音频数据输出。

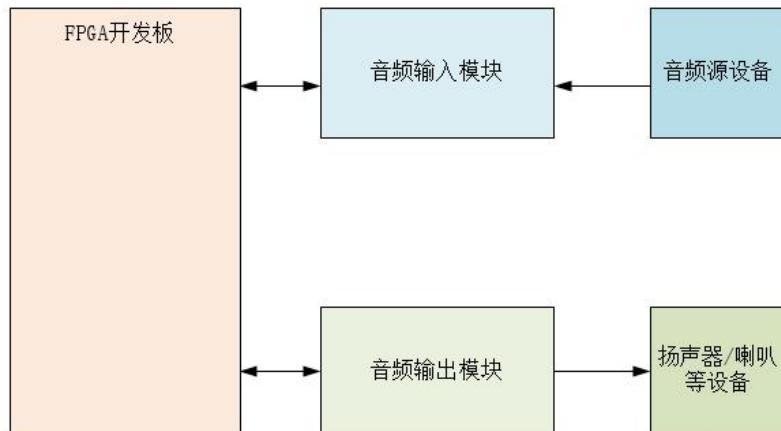

实验框图：

图一 实验框图

## 2、实验器材

MES50HP FPGA 开发板：

图二 MESS50HP 开发板

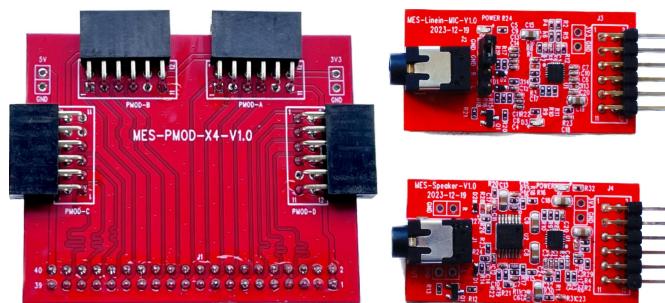

PMOD 音频模块组合：

PMOD 扩展版：用于 40pin 扩展口转 PMOD 扩展口。

音频输入模块：将音频模拟信号转为音频数据。音频输出模块：将音频数据转为音频模拟信号。

说明：麦克风收集、扬声器发出的信号都为模拟信号，但 FPGA 处理的信号为数字信号，所以我们需要使用两个音频模块完成音频模拟信号与音频数据之间的转换。

图三 PMOD 音频模块组合

3.5mm 3 环音频线 x2 :

连接音频源与音频输入模块、扬声器与音频输出模块。

图四 3.5mm 3 环音频线

音频源设备：电脑

扬声器/喇叭等设备：音响

### 3、实验代码设计

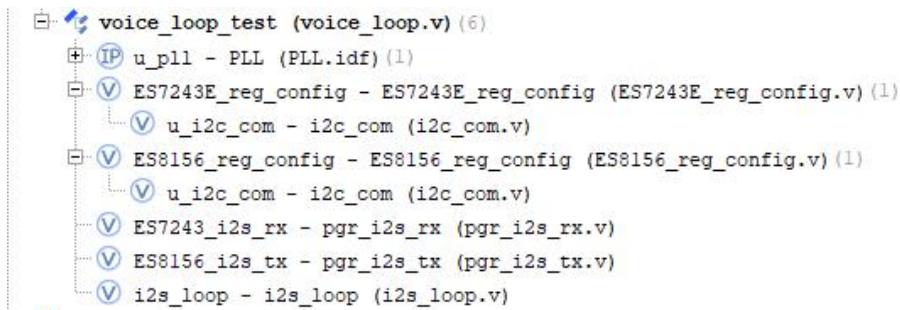

代码层次化设计结构：

图五 代码层次化设计结构

模块功能说明：

表 1 模块功能说明

|                    |                     |

|--------------------|---------------------|

| PLL                | 生成 Master clock     |

| ES7243E_reg_config | ES7243E 芯片 i2c 配置模块 |

| ES8156_reg_config  | ES8156 芯片 i2c 配置模块  |

| ES7243_i2s_rx      | 音频数据接收模块            |

| i2s_loop           | 音频环回模块              |

| ES8156_i2s_tx      | 音频数据发送模块            |

详细信号说明请参考 **MES-Linein-MIC** 硬件使用说明、**MES-Speaker** 硬件使用说明、**ES8156** 音频芯片数据手册、**ES7243E** 音频芯片数据手册。

芯片配置说明：

ES7243E 芯片与 ES8156 芯片使用时，需要先进行寄存器配置，demo 中芯片配置参数如下：

ES7243E：

- 1、模式：master（LRCK 与 SRCK 由 ES7243E 输出）

- 2、音频采样率：48KHz

- 3、数据位宽：16bit

- 4、MCLK：12.288MHz（由 FPGA 提供）

提示：音频源的输出格式应与配置参数保持一致。

ES8156：

- 5、模式：master（LRCK 与 SRCK 由 ES8156 输出）

- 6、音频采样率：48KHz

- 7、数据位宽：16bit

- 8、MCLK：12.288MHz（由 FPGA 提供）

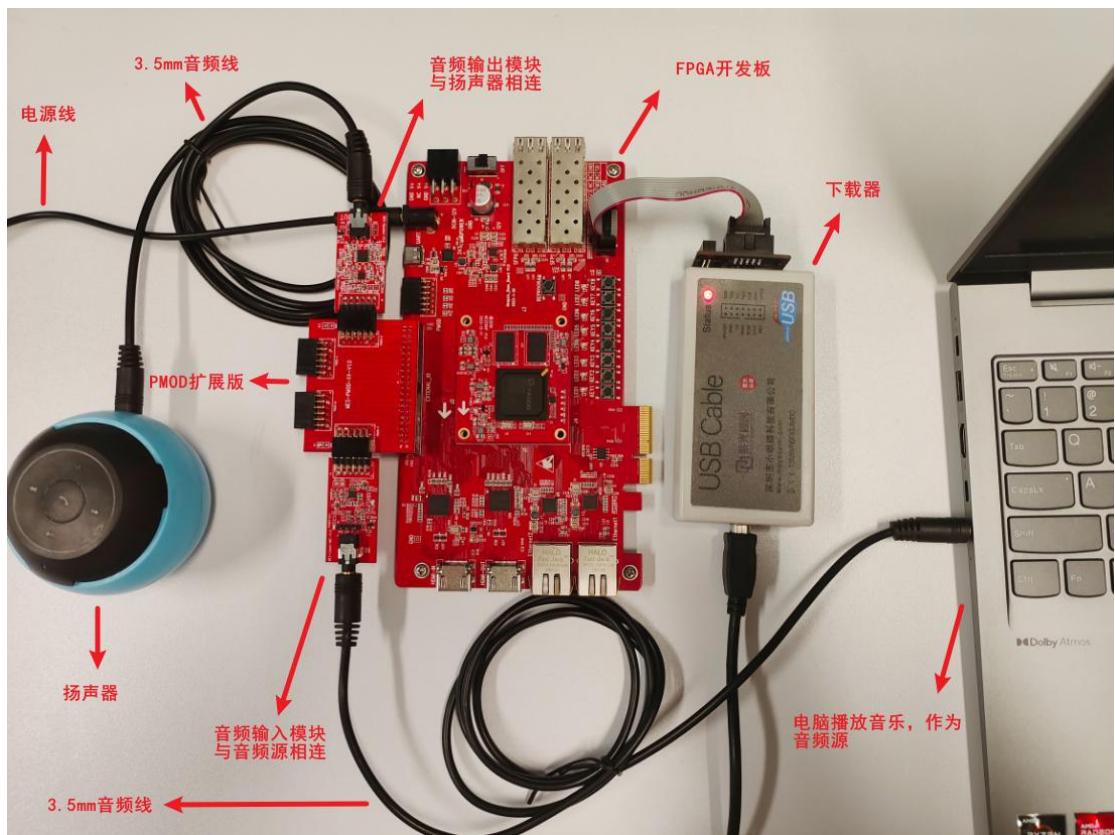

## 4、实验器件连接

图六 实验器件连接

其中：音频输入模块的管脚绑定在了 PMOD—C、音频输出模块的管脚绑定在了 PMOD—D。

## 5、补充说明

- (1) 四环耳机不支持麦克风，仅支持扬声器

- (2) 推荐使用下图耳机规格作为音频麦克风或者音频播放设备（双插孔台式耳机）

## 2.0米/双插孔

(3) 音频源输出格式应与 ES7243E 芯片配置参数保持一致:

## 6、实验目的:

将音频信号输入至 FPGA 中，经过简单的处理后，将音频信号输出，可以听到连接音频输出模块的扬声器播放音频源输出的音频信号。