## 10. DDR3 读写实验例程

### 10.1 实验目的

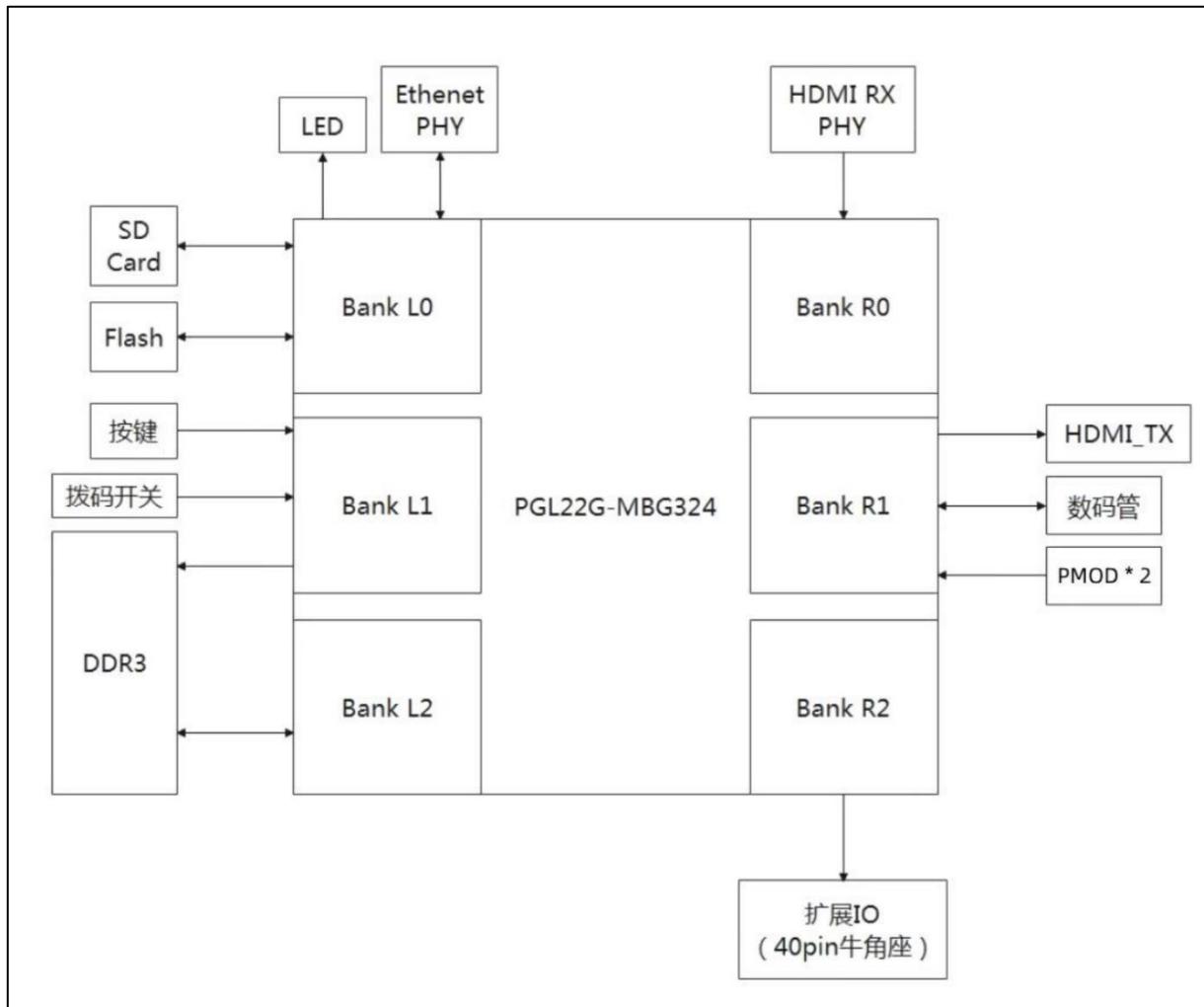

MES22GP 开发板上有一片 Micron 的 DDR3 (MT41K256M16 TW107: P) 内存组件，拥有 16bit 位宽的存储空间 (MT41J 系列是旧的产品，目前很多型号已经停产，后续替代就是 MT41K 系列。硬件上的差异是 MT41K 支持 1.35V 低电压，同时也兼容 1.5V 电压，所以可以用 MT41K 直接替换相应型号的 MT41J 芯片)。该 DDR3 存储系统直接连接到了 PGL22G 的 Bank L1 及 Bank L2 上。PGL22G 的 DDR IP 为硬核 IP，需选择正确的 IP 添加 (详情请查看“MES22GP 开发板硬件使用手册”)。

生成 DDR3 IP 官方例程，实现 DDR3 的读写控制，了解其工作原理和用户接口。

### 10.2 DDR3 控制器简介

HMIC\_H IP 是深圳市紫光同创电子有限公司 FPGA 产品中用于实现对 SDRAM 读写而设计的 IP，通过公司 Pango Design Suite 套件（后文简称 PDS）中 IP Compiler 工具（后文简称 IPC）例化生成 IP 模块。

- 支持 LPDDR、DDR2、DDR3；

- 支持 x8 x16 Memory Device；

- 用户接口

- 标准的 AXI4 总线接口

- ◆ 一组 128bit 的 AXI4 Host Port

- ◆ 两组 64bit 的 AXI4 Host Port

- 标准的 APB 总线接口

- ◆ DDRC 配置接口

- 支持可配低功耗模式：Self-Refresh 和 Power Down；

- 支持 DDR3 的最高数据速率达到 1066Mbps；

- 支持 DDR2 的最高数据速率达到 800Mbps；

- 支持 LPDDR 的最高数据速率达到 400Mbps；

- Burst Length 8 和单 Rank；

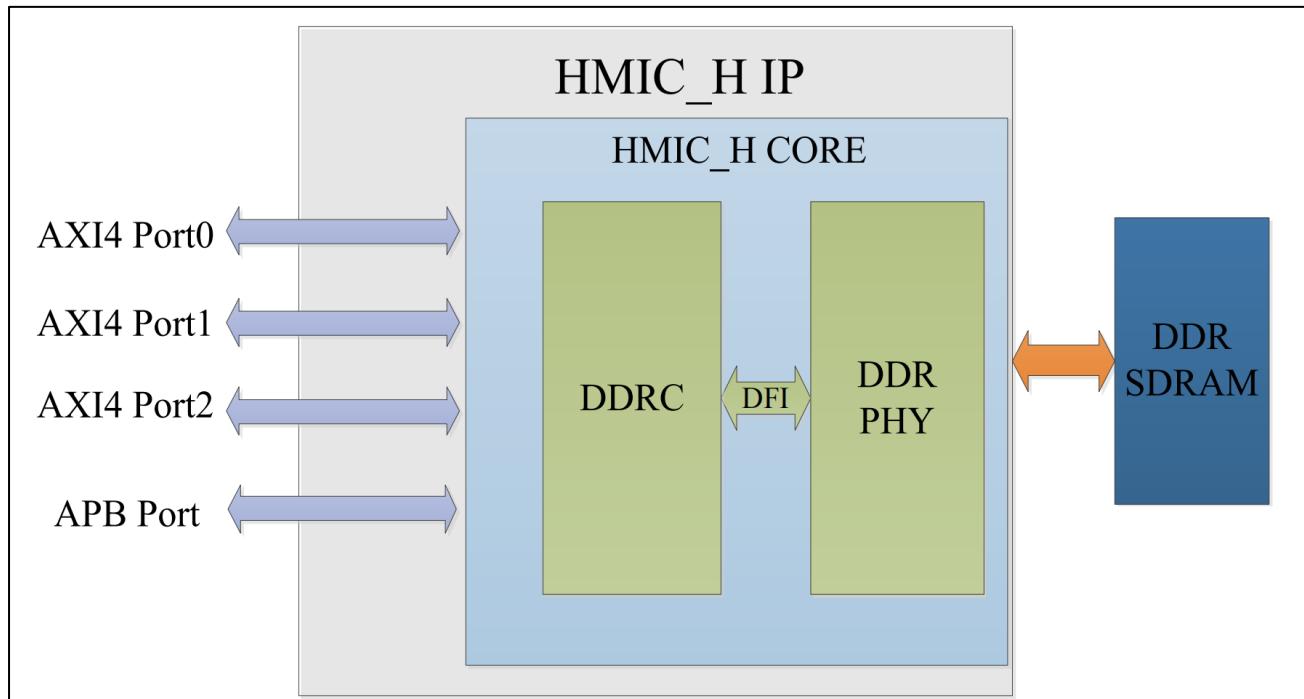

HMIC\_H IP 系统框图如下图所示：

HMIC\_H IP 包括了 DDR Controller、DDR PHY 和 PLL，用户通过 AXI4 接口实现数据的

读写, 通过 APB 接口可配置 DDR Controller 内部寄存器, PLL 用于产生需要的各种时钟。

AXI4 接口: HMIC\_H IP 提供三组 AXI4 Host Port: AXI4 Port0(128bit)、AXI4 Port1(64bit)、AXI4 Port2(64bit)。用户通过 HMIC\_H IP 界面可以选择使能这三组 AXI4 Port。三组 AXI4 Host Port 均为标准 AXI4 接口。

APB 接口: HMIC\_H IP 提供一个 APB 配置接口, 通过该接口, 可配置 DDR Controller 内部寄存器。HMIC\_H IP 初始化完成后使能该接口。

详细的端口说明请点击 IP 配置界面的 View Datasheet 查看 IP 手册。

## 10.3 实验设计

### 10.3.1 安装 DDR3 IP 核

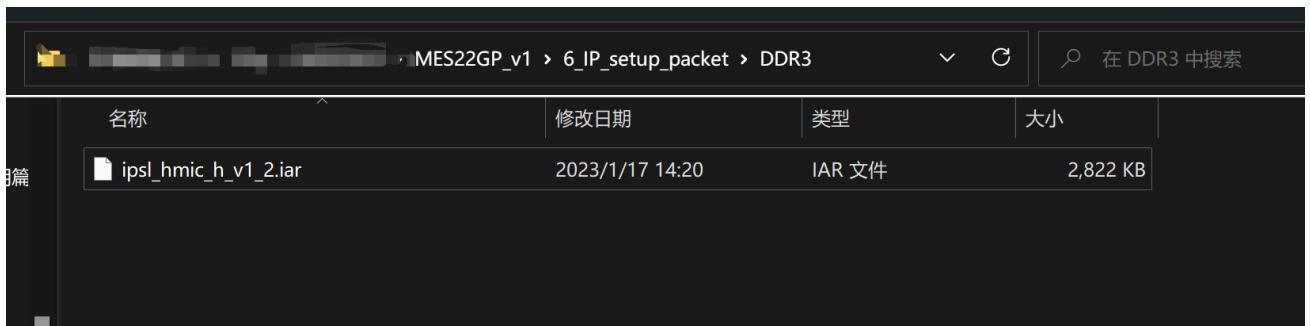

PDS 安装后, 需手动添加 DDR3 IP, 操作流程如下:

- (1) DDR3 IP 文件: 6\_IP\_setup\_packet\DDR3\ipsl\_hmic\_h\_v1\_2. iar

(2) IP 安装步骤: 1\_Demo\_document\工具使用篇\03\_IP 核安装与查看用户指南

### 10.3.2 DDR3 读写 Example 工程

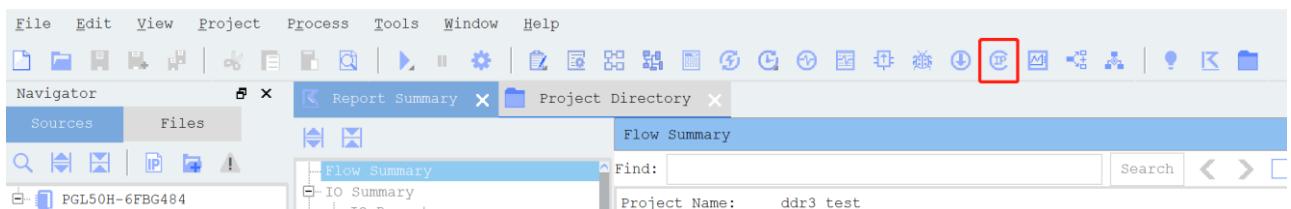

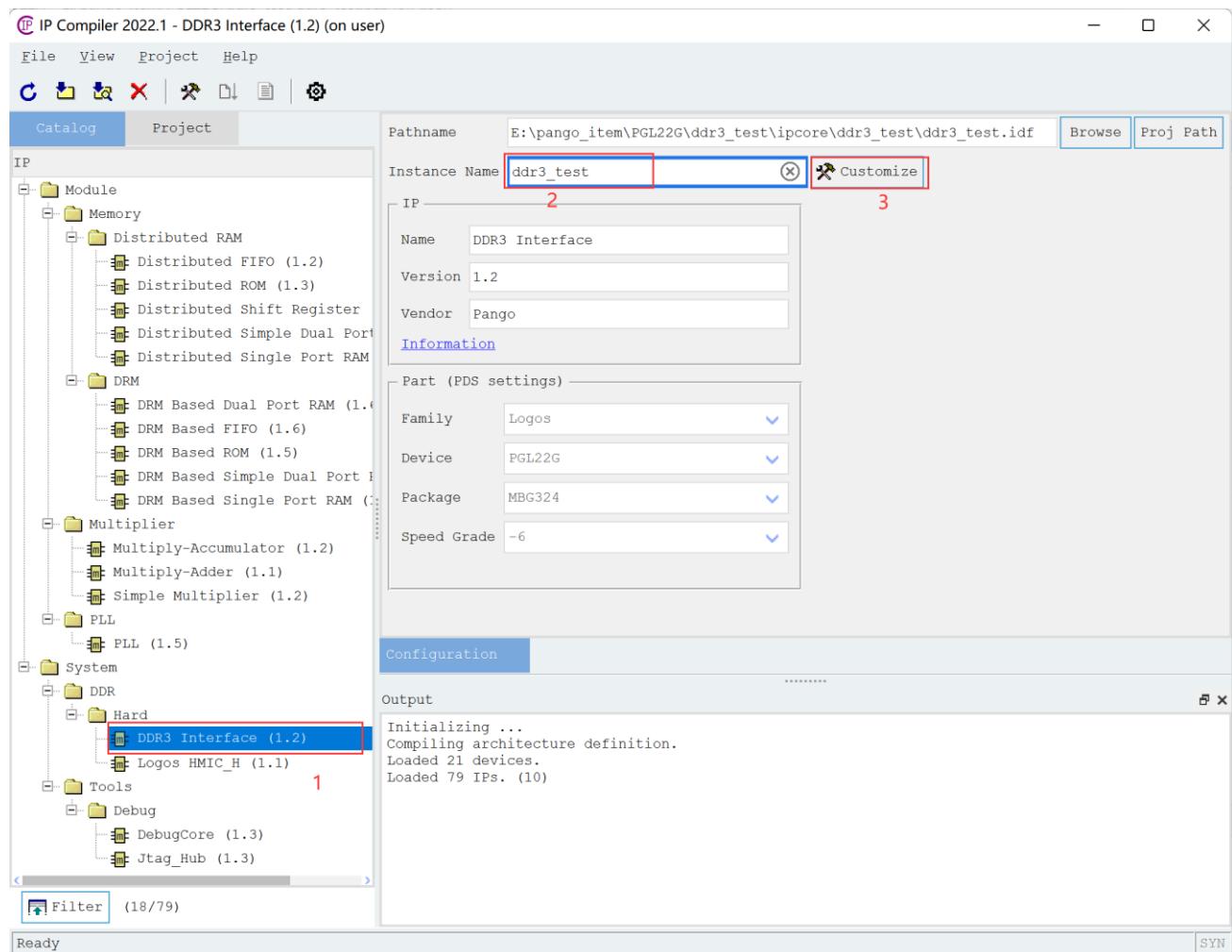

1. 打开 PDS 软件, 新建工程 ddr3\_test, 点开如下图标, 打开 IP Compiler;

2. 选择 DDR3 IP, 取名, 然后点击 Customize;

### 10.3.2.1 DDR3 IP 配置说明

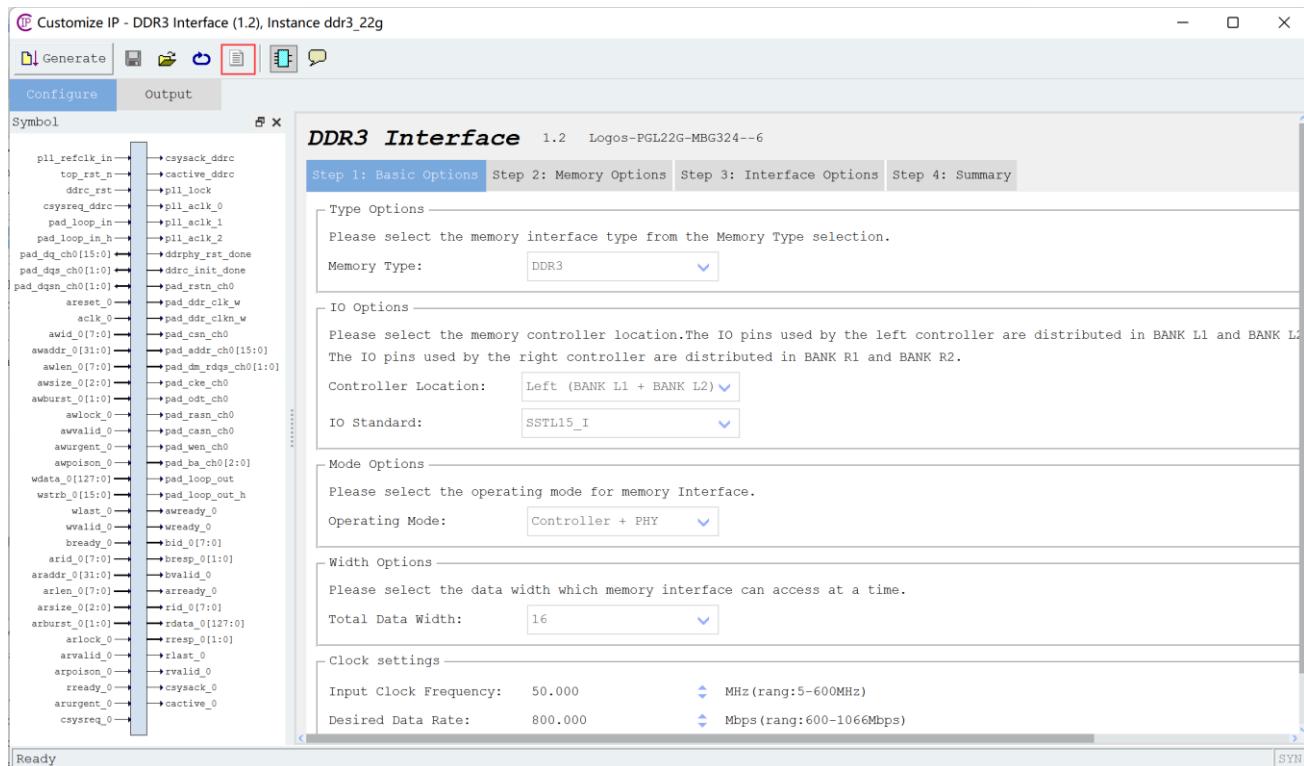

HMIC\_H IP 配置分为四个页面, 分别为 Step1: Basic Options, Step2: Memory Options, Step3: Interface Options, Step4: Summary, 请务必按照该页面顺序配置。

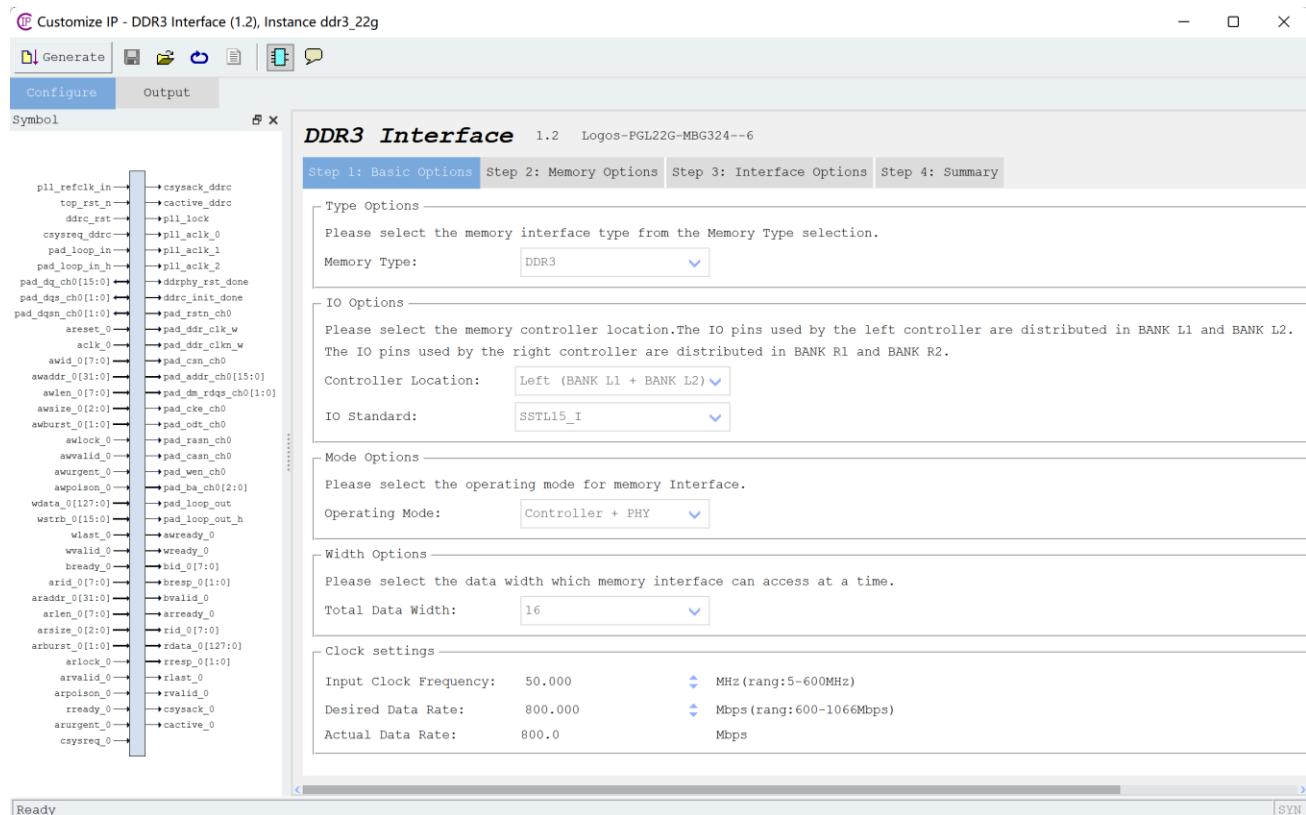

#### 10.3.2.2 Step 1: Basic Options

是 IP 的基本配置页面, 页面如下图所示:

Basic Options 详细参数见下表:

表 7 Basic Options 参数说明

| 选项名/参数名             | 说明                                                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------------|

| Memory Type         | 使用的SDRAM类型, 目前支持的类型为<br>1) DDR3;<br>2) DDR2;<br>3) LPDDR                                                                        |

| Controller Location | Controller在FPGA芯片的位置, 目前PGL22支持的位置为<br>1) Right (BANK R1 + BANK R2);<br>2) Left (BANK L1 + BANK L2);<br>注: HMIC_H为硬核, 位置固定不可变动。 |

| 选项名/参数名               | 说明                                                                                                       |

|-----------------------|----------------------------------------------------------------------------------------------------------|

| IO Standard           | 接口标准选项, DDR3支持的接口标准为<br>1) SSTL15_I<br>2) SSTL15_II<br>DDR2和LPDDR支持的接口标准为<br>1) SSTL18_I<br>2) SSTL18_II |

| Operating Mode        | HMIC_H运行模式选择。目前只支持Controller + PHY模式                                                                     |

| Total Data Width      | 与HMIC_H连接的片外SDRAM总共的DQ宽度。目前支持的总宽度为<br>1) 16<br>2) 8                                                      |

| Input Clock Frequency | HMIC_H的输入时钟, 单位MHz                                                                                       |

| Desired Data Rate     | 期望的数据速率, DDR3支持的最高速率为1066Mbps, DDR2支持的最高速率为800Mbps, LPDDR支持的最高速率为400Mbps。                                |

| Actual Data Rate      | 实际能达到的数据速率, 尽可能接近期望的速率。                                                                                  |

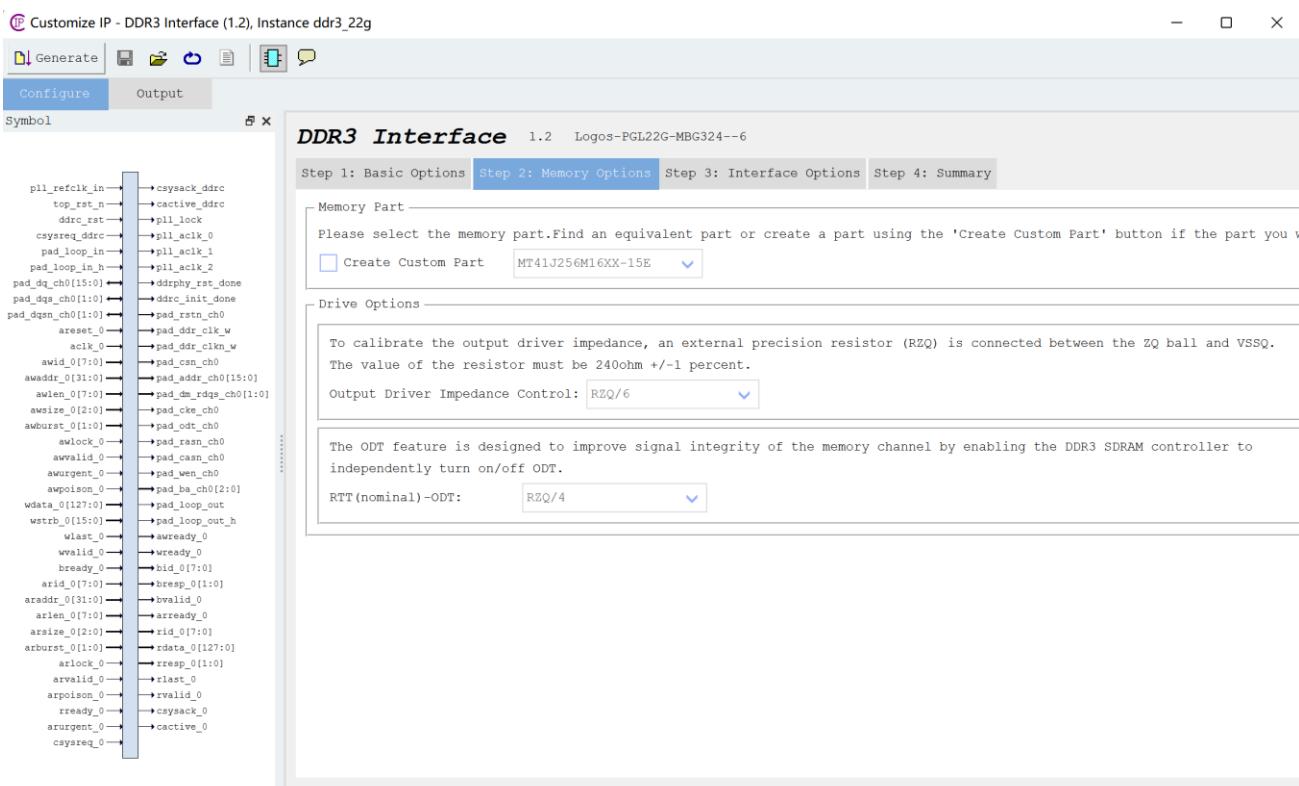

### 10.3.2.3 Step 2: Memory Options

是 Memory 参数的配置页面, 页面如下图所示:

表 8 Memory Options 参数说明

| 选项名/参数名            | 说明                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Memory Part        | <p>SDRAM的具体型号, DDR3支持的型号为</p> <ol style="list-style-type: none"> <li>1) MT41J128M8XX-15E</li> <li>2) MT41J64M16XX-15E</li> <li>3) MT41J256M8XX-15E</li> <li>4) MT41J128M16XX-15E</li> <li>5) MT41J512M8XX-15E</li> <li>6) MT41J256M16XX-15E</li> </ol> <p>DDR2支持的型号为</p> <ol style="list-style-type: none"> <li>1) MT47H128M8XX-25E</li> <li>2) MT47H64M16XX-25E</li> <li>3) MT47H128M16XX-25E</li> <li>4) MT47H256M4XX-25E</li> <li>5) MT47H64M8XX-25E-IT</li> </ol> <p>LPDDR支持的型号为</p> <ol style="list-style-type: none"> <li>1) MT46H128M16XXXX-5L-IT</li> <li>2) MT46H64M16XXXX-5L-IT</li> <li>3) MT46H64M16XXXX-6L-IT</li> <li>4) MT46H32M16XXXX-5</li> <li>5) MT46H16M16XXXX-6-IT</li> <li>6) MT46H16M16XXXX-75-IT</li> </ol> <p>若这些均不是所需要的器件型号, 则可以勾选Create Custom Part选项, 然后在Custom Memory Part选项框中定制新的SDRAM类型。</p> |

| Custom Memory Part | <p>该选项框在勾选Create Custom Part选项时显示, 用于定制新的SDRAM类型。包含选项: Base Part、Timing Parameters、Row Address、Column Address、Bank Address。</p> <p>Base Part: 定制SDRAM的参考型号。</p> <p>Timing Parameters: 定制SDRAM的Timing参数。</p> <p>Row Address: 行地址。</p> <p>Column Address: 列地址。</p> <p>Bank Address: Bank地址</p>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Drive Options      | <p>驱动能力选项, DDR3支持的驱动选项为 (详细说明见DDR3协议)</p> <ol style="list-style-type: none"> <li>1) Output Driver Impedance Control</li> <li>2) RTT(nominal)-ODT</li> </ol> <p>DDR2支持的驱动选项为 (详细说明见DDR2协议)</p> <ol style="list-style-type: none"> <li>1) Output Driver Strength</li> <li>2) RTT(nominal)-ODT</li> </ol> <p>LPDDR支持的驱动选项为 (详细说明见LPDDR协议)</p> <ol style="list-style-type: none"> <li>1) Driver Strength</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                             |

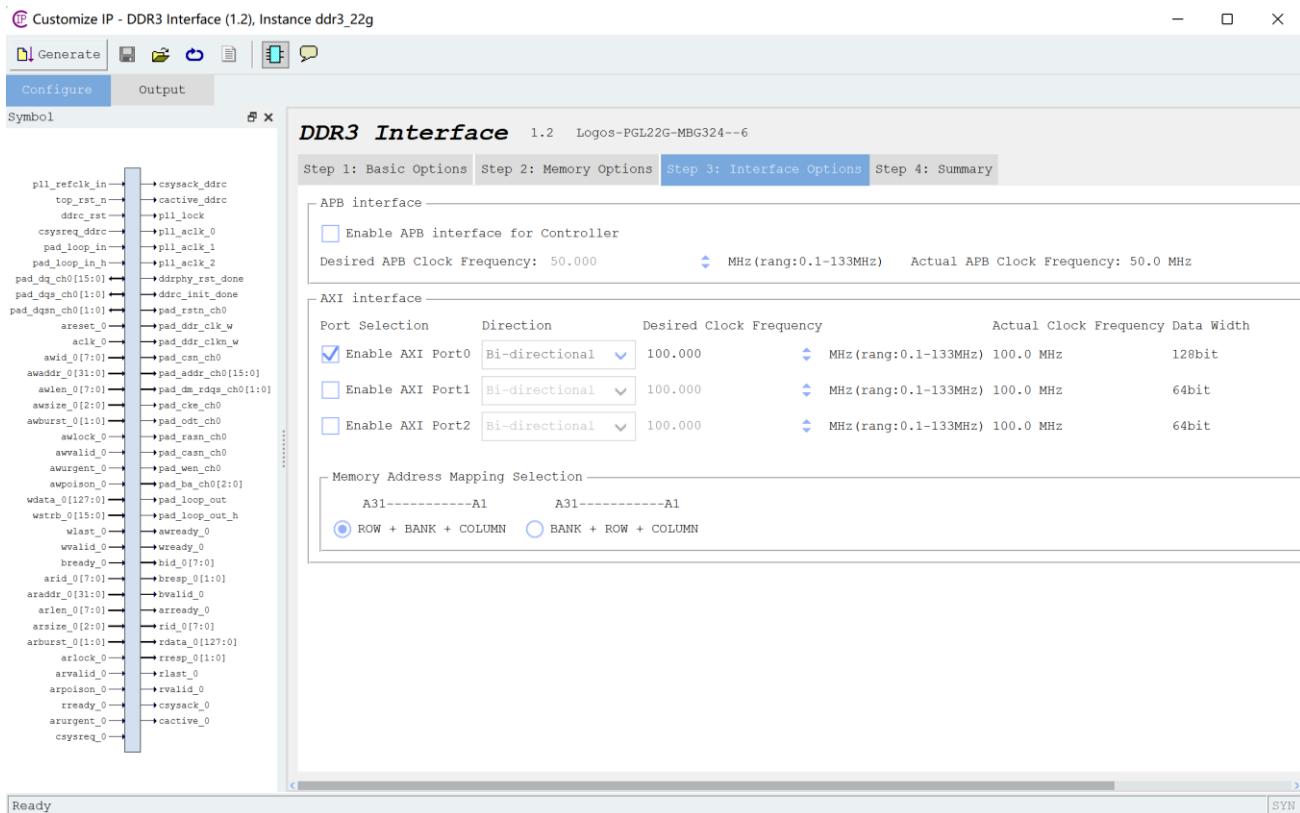

#### 10.3.2.4 Step 3: Interface Options

是接口参数的配置页面, 页面如下图所示:

Interface Options 详细参数见下表:

表 9 Interface Options 参数说明

| 选项名/参数名                          | 说明                                                                                                                                                                            |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| APB interface                    | APB接口配置, 包括使能和APB接口的时钟频率。                                                                                                                                                     |

| AXI interface                    | 三组AXI4接口的配置, 包括使能、读写方向、时钟频率。<br>读写方向配置如下<br>1) Bi-directional 可读可写<br>2) Read 只读<br>3) Write 只写                                                                               |

| Memory Address Mapping Selection | SDRAM的地址与AXI4地址映射选项<br>1) ROW + BANK + COLUMN<br>2) BANK + ROW + COLUMN<br>AXI4的读写地址为32位, 但是只有A1-A31有效, A0为无效位。例如, 选择ROW+BANK+COLUMN时, SDRAM列地址c0对应AXI地址A1, c1对应A2, 其他地址以此类推。 |

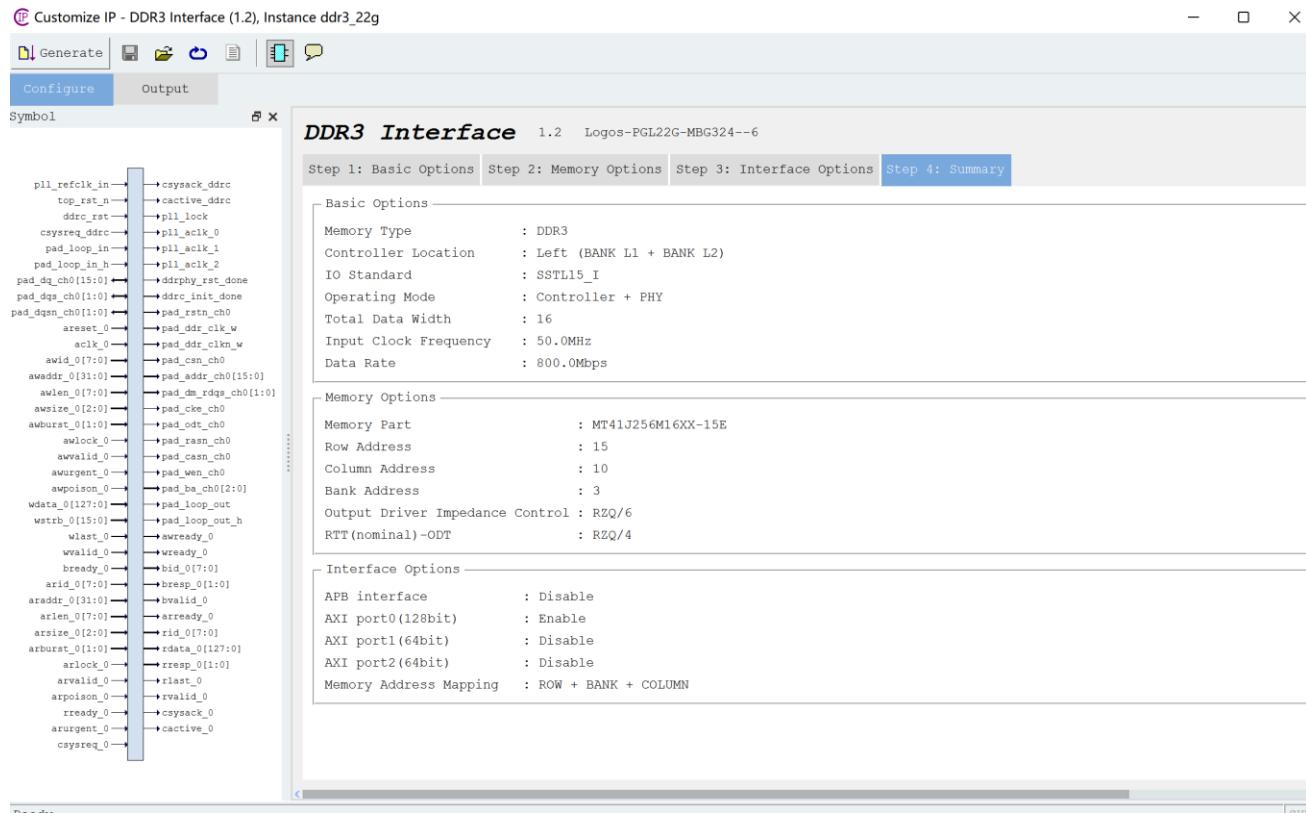

#### 10.3.2.5 Step 4: Summary

用于打印当前的配置信息, 不需要配置参数, 点击 Generate 可生成 DDR3 IP; 页面如下图所示:

关闭本工程，在本工程文件内按此路径打开 Example 工程（也可以打开示例工程）：

ddr\_test\ipcore\ddr\_test\pnr\tr1\_phy\_22\ddr\_test.pds

**注:**如果使用自己的工程，那么需要打开 example 工程中的引脚约束文件对以下信号修改其引脚配置，方能在烧录程序后看到正确的 LED 灯亮灭情况：

|    |                 |        |     |        |     |           |   |      |      |

|----|-----------------|--------|-----|--------|-----|-----------|---|------|------|

| 42 | clk_led         | OUTPUT | E8  | BANKL0 | 3.3 | LVC MOS33 | 4 | NONE | FAST |

| 43 | ddr_init_done   | OUTPUT | F7  | BANKL0 | 3.3 | LVC MOS33 | 4 | NONE | FAST |

| 44 | ddrphy_rst_done | OUTPUT | F8  | BANKL0 | 3.3 | LVC MOS33 | 4 | NONE | FAST |

| 45 | err_flag        | OUTPUT | E5  | BANKL0 | 3.3 | LVC MOS33 | 4 | NONE | FAST |

| 57 | pll_lock        | OUTPUT | E6  | BANKL0 | 3.3 | LVC MOS33 | 4 | NONE | FAST |

| 60 | pll_refclk_in   | INPUT  | H18 | BANKR1 | 3.3 | LVC MOS33 |   | NONE |      |

| 61 | top_rst_n       | INPUT  | H1  | BANKL1 | 1.5 | SSTL15_I  |   | NONE |      |

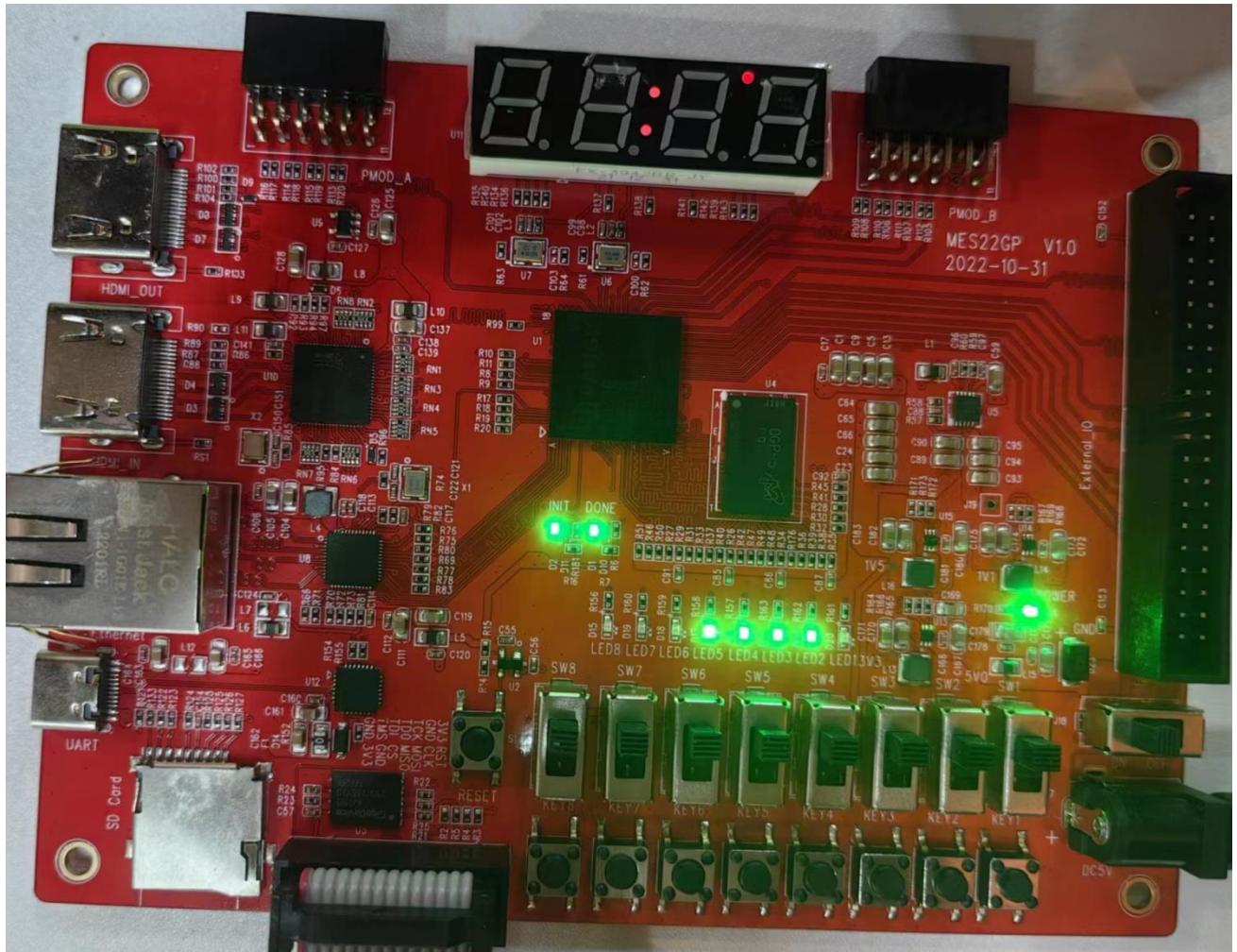

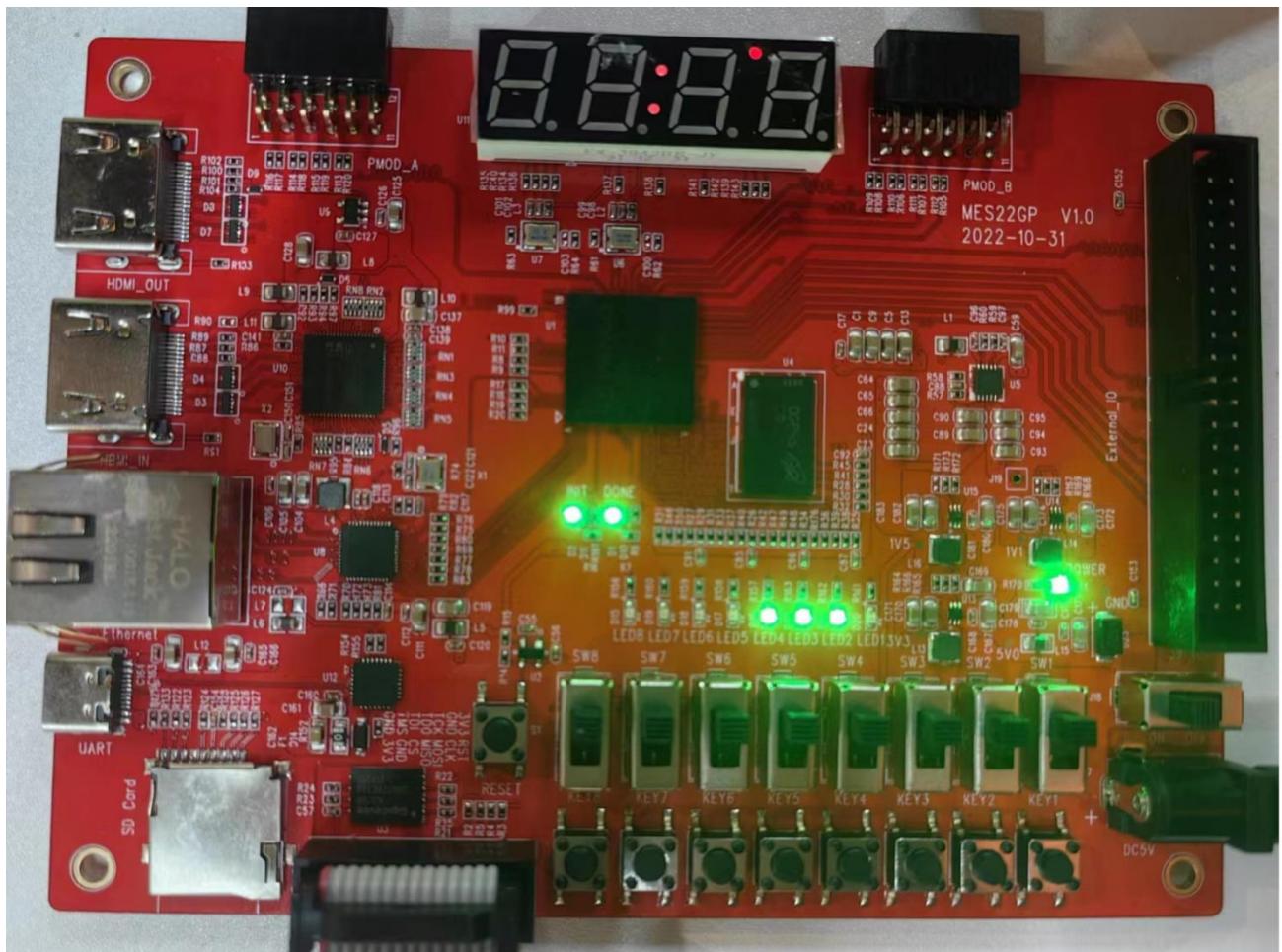

## 10.4 实验现象

下载程序，可以看到 LED1 常灭；LED2，LED3，LED4 常亮；LED5 闪烁。

| 信号名称            | 参考说明                | LED 编号 | 引脚 |

|-----------------|---------------------|--------|----|

| err_flag        | 数据检测错误信号，高电平表示数据错误  | 1      | E5 |

| pll_lock        | Pll 锁定指示，高电平有效      | 2      | E6 |

| ddr_init_done   | 初始化完成标志，高电平有效       | 3      | F7 |

| ddrphy_rst_done | DDRPHY 复位完成标志，高电平有效 | 4      | F8 |

| heart_beat_led  | 心跳信号，闪烁             | 5      | E8 |

上板效果：