### 3. 数码管静态显示实验例程

#### 3.1 MES22GP 开发板简介

MES22GP 扩展底板提供了一个四位八段的共阳极数码管。（详情请查看“MES22GP 开发板硬件使用手册”）。

#### 3.2 实验目的

四位八段数码管同时循环显示数字 0~9。

#### 3.3 实验原理

数码管是一种半导体发光器件，其基本单元是发光二极管。能显示 4 个数码管叫四位数码管。数码管按段数分为七段数码管和八段数码管，八段数码管比七段数码管多一个发光二极管单元（多一个小数点显示）；按发光二极管单元连接方式分为共阳极数码管和共阴极数码管。共阳数码管是指将所有发光二极管的阳极接到一起形成公共阳极 (COM) 的数码管。共阳数码管在应用时应将公共极 COM 接到+5V，当某一字段发光二极管的阴极为低电平时，相应字段就点亮。当某一字段的阴极为高电平时，相应字段就不亮。共阴数码管是指将所有发光二极管的阴极接到一起形成公共阴极 (COM) 的数码管。共阴数码管在应用时应将公共极 COM 接到地线 GND 上，当某一字段发光二极管的阳极为高电平时，相应字段就点亮。当某一字段的阳极为低电平时，相应字段就不亮。

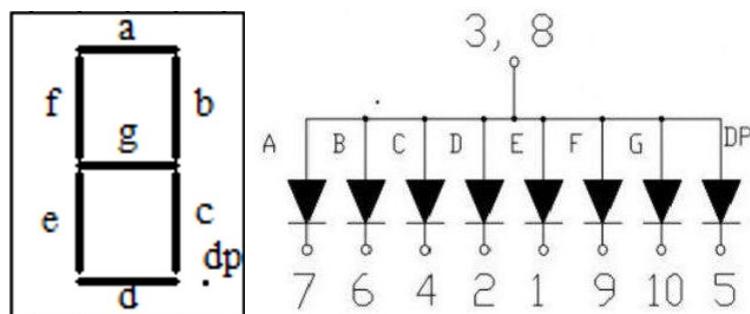

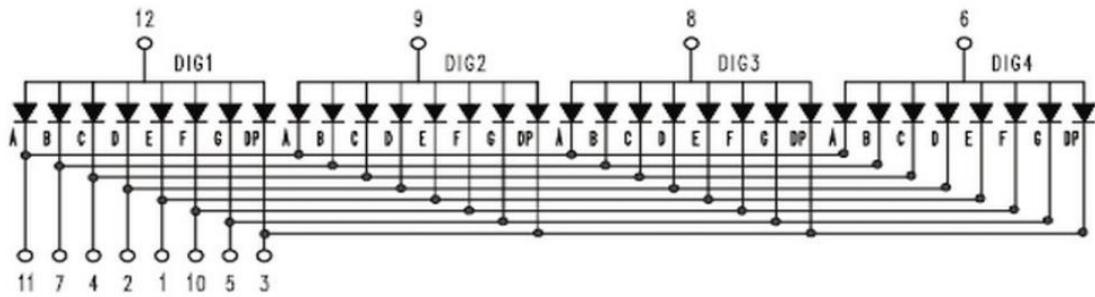

4 位共阴数码管内部管脚连接图如下：

段选：段选由 8 根 led 灯组成，分别为 a, b, c, d, e, f, g, dp;

由段选信号控制某段数码管点亮；

位选：位选由 4 组 8 个段选 LED 组成，分别为 seg1, seg2, seg3, seg4;

由选通信号控制第几块数码管点亮；

例：如果我们只点亮第一位的 A：需要将 11 脚配置高电平，其他段选（1-5, 7, 10, 11）配置低电平；将 12 脚配置低电平，其他位选脚配置（6, 8, 9）高电平；

点亮数码管原理：

输入相应的电平点亮一根根小火柴 a-b-c-d-e-f-g-dp。如果数码管是共阴极，给高电平 1 即可相应点亮，反之如果是共阳极，给低电平 0 即可相应点亮。MES22GP 板的数码管为共阳极数码管，所以才有如下配置显示出 0~9：

```

1      assign dig = 4'b1111;

2          // 0 1 2 3 4 5 6 7

3          // G F E D C B A P

4      case(counter)

5          4'd0:smg = 8'b1000_0001;//"0" 8'b1000_0001

6          4'd1:smg = 8'b1100_1111;//"1" 8'b1100_1111

7          4'd2:smg = 8'b0110_0010;//"2" 8'b1001_0010

8          4'd3:smg = 8'b1000_0110;//"3" 8'b1000_0110

9          4'd4:smg = 8'b1100_1100;//"4" 8'b1100_1100

10         4'd5:smg = 8'b1010_0100;//"5" 8'b1010_0100

11         4'd6:smg = 8'b1010_0000;//"6" 8'b1010_0000

12         4'd7:smg = 8'b1000_1111;//"7" 8'b1000_1111

13         4'd8:smg = 8'b1000_0000;//"8" 8'b1000_0000

14         4'd9:smg = 8'b1000_0100;//"9" 8'b1000_0100

15         default:smg = 8'b1000_0001;

16     endcase

```

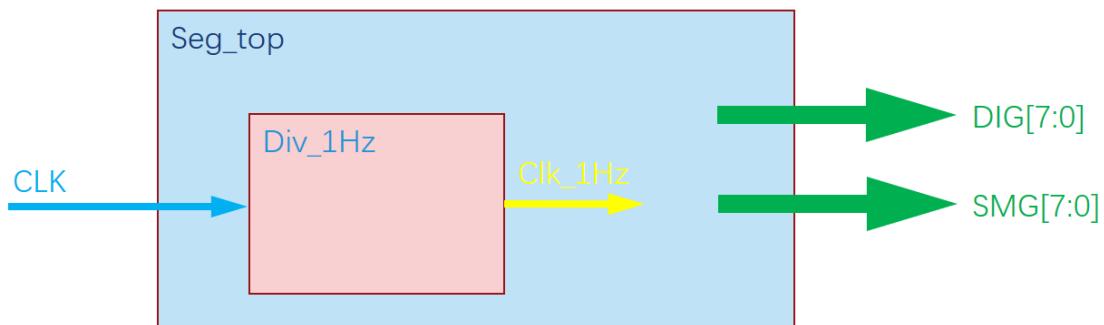

实现框架如下：

- 1、顶层实现数码管显示切换；

- 2、需要设计一个 1 秒钟的计时器；

### 3.1.1 产生 1Hz 的时钟

通过一个 1s 的计数器产生一个 1hz 的时钟：计数的前 0.5s 为低电平，后 0.5s 为高电平。

### 3.1.2 顶层模块实现数码管切换

由于是数码管静态显示，故只需要将四位八段数码管的四个位选信号全部置高，即可使得四个数码管全亮，然后在 1hz 的时钟下产生一个 0~9 的计数器，将这个计数器的值作为数码管显示的值，即可循环显示数字 0~9。

## 3.4 实验源码设计

### 3.4.1 顶层文件源码

```

1 `timescale 1ns / 1ps

2 ///////////////////////////////////////////////////////////////////

3 // Company: Myminieye

4 // Engineer: Mill

5 //

6 // Create Date: 2019-09-16 11:26

7 // Design Name:

8 // Module Name: blue

9 // Project Name:

10 // Target Devices:

11 // Tool Versions:

12 // Description:

13 //

14 // Dependencies: 4个数码管显示, 0~9, 每个1s变化一次

15 //

16 // Revision: v1.0

17 // Revision 0.01 - File Created

18 // Additional Comments:

19 //

20 ///////////////////////////////////////////////////////////////////

21 `define UD #1

22 module seq_test

23 (

24     input clk,//50MHZ

25     output [3:0]dig,

26     output reg [7:0]smg

27 );

28

29

30

31 wire clk_1hz;

32 div_clk u_div_clk

33 (

34     .clk(clk),

35     .clk_1hz(clk_1hz)

36 );

37

38 reg [3:0]counter=0;

39 always @ (posedge clk_1hz)

40 begin

41     if(counter==4'd9)

42         counter <= `UD 4'd0;

43     else

44         counter <= `UD counter + 1'b1;

45 end

46

47 assign dig = 4'b1111;

48

```

```

48 //IO_LOC "smg[0]" -> G;

49 //IO_LOC "smg[1]" -> F;

50 //IO_LOC "smg[2]" -> E;

51 //IO_LOC "smg[3]" -> D;

52 //IO_LOC "smg[4]" -> C;

53 //IO_LOC "smg[5]" -> B;

54 //IO_LOC "smg[6]" -> A;

55 //IO_LOC "smg[7]" -> P;

56 //=====

57 // 0 1 2 3 4 5 6 7

58 // G F E D C B A P

59 // 共阳极数码管, 为0有效, 即点亮

60 // Runber 共阴极数码管 , 为1有效

61 //=====

62 always @(*)

63 begin

64     case(counter)

65         4'd0:smg = 8'b1000_0001;//"0" 8'b0111_1110

66         4'd1:smg = 8'b1100_1111;//"1" 8'b0011_0000

67         4'd2:smg = 8'b1001_0010;//"2" 8'b0110_1101

68         4'd3:smg = 8'b1000_0110;//"3" 8'b0111_1001

69         4'd4:smg = 8'b1100_1100;//"4" 8'b0011_0011

70         4'd5:smg = 8'b1010_0100;//"5" 8'b0101_1011

71         4'd6:smg = 8'b1010_0000;//"6" 8'b0101_1111

72         4'd7:smg = 8'b1000_1111;//"7" 8'b0111_0000

73         4'd8:smg = 8'b1000_0000;//"8" 8'b0111_1111

74         4'd9:smg = 8'b1000_0100;//"9" 8'b0111_1011

75         default:smg = 8'b1000_0001;

76     endcase

77 end

78

79

80 endmodule

```

### 3.4.2 生成 1hz 时钟模块

```

1  `timescale 1ns / 1ps

2  ///////////////////////////////////////////////////////////////////

3  // Company: Myminieye

4  // Engineer: Mill

5  //

6  // Create Date: 2019-09-16 11:26

7  // Design Name:

8  // Module Name: blue

9  // Project Name:

10 // Target Devices:

11 // Tool Versions:

12 // Description:

13 //

14 // Dependencies: 数码管显示, 0~9, 每个1s变化一次

15 //

16 // Revision: v1.0

17 // Revision 0.01 - File Created

18 // Additional Comments:

19 //

20 ///////////////////////////////////////////////////////////////////

21 `define UD #1

22 |  module div_clk

23 (

24     input clk,

25     output clk_1hz

26 );

27

28 reg [25:0] times_cnt=0;

29

30 always @ (posedge clk)

31 begin

32     if(times_cnt== 26'd50000000-1'b1)

33         times_cnt <= `UD 26'd0;

34     else

35         times_cnt <= `UD times_cnt + 1'b1;

36 end

37

38 reg flag=0;

39 always @ (posedge clk)

40 begin

41     if(times_cnt== 26'd50000000/2 - 1'b1)

42         flag <= `UD 1'b1;

43     else if(times_cnt== 26'd50000000 - 1'b1)

44         flag <= `UD 1'b0;

45 end

46 assign clk_1hz = flag;

47

48 endmodule

```

### 3.5 实验现象

下载程序后，四位八段数码管同时循环显示数字 0~9。