## PDS与Modelsim联合仿真教程

### 1. 打开仿真库编译:

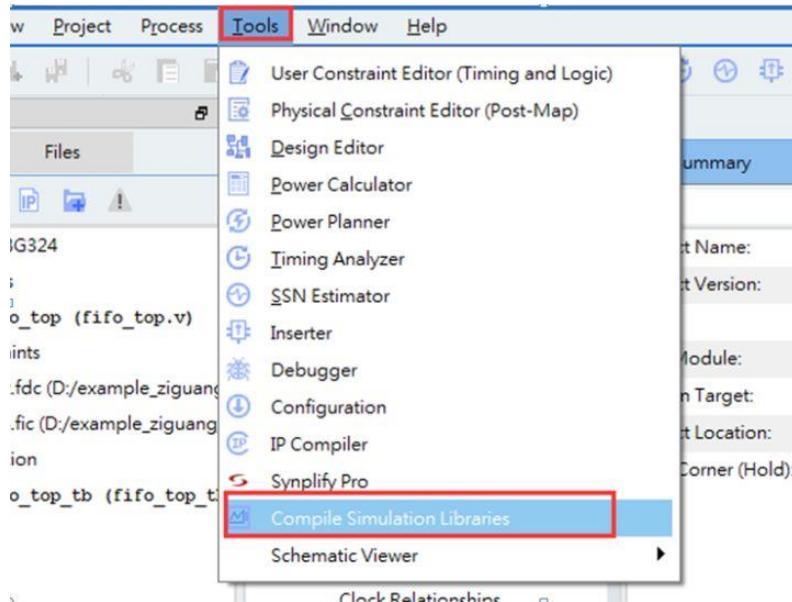

打开工程, 点击 PDS 的【tools】菜单下的【Compile Simulation Libraries】。

### 2. 设置:

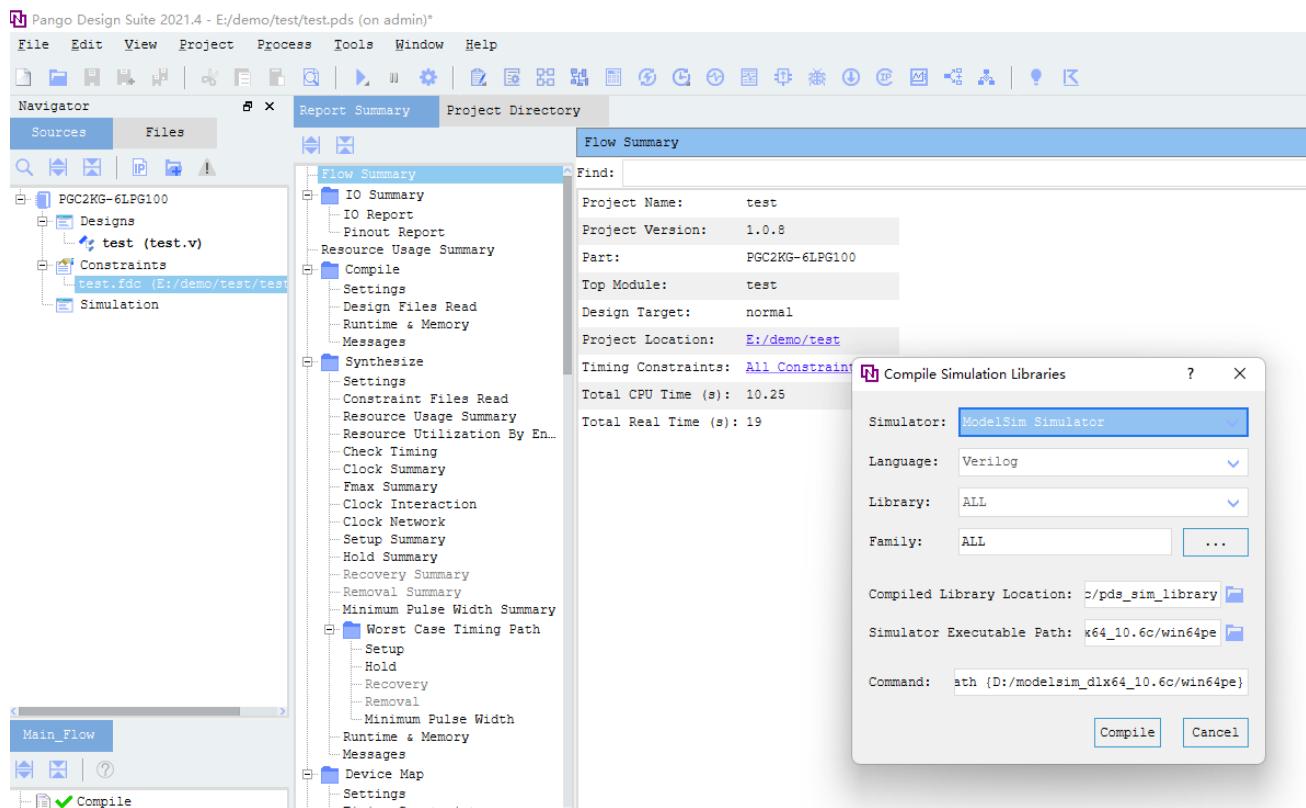

【Simulator】: 第三方仿真工具, 目前支持 ModelSim 和 QuestaSim, 本教程选择 ModelSim;

【Language】: 仿真库用的语言;

【Library】: 选择 usim 则是 GTP 前仿库, vsim 则是 VOP 后仿库, ALL 则包括这两种仿真库, 默认选择 ALL;

【Family】: 指定芯片系列对应的仿真库进行编译, 可支持一次编译多个系列, 默认选择 ALL。

【Compiled Library Location】: 编译出来的库的位置, 默认是在当前工程下面; 可以把编译库放在一个固定位置。

【Simulator Executable Path】: 选择 ModelSim 运行路径 (ModelSim 安装文件夹下.../.../win64pe)

设置完成后点击 compile, 运行编译库会有状态栏显示正在编译。

### 3. 编译仿真库

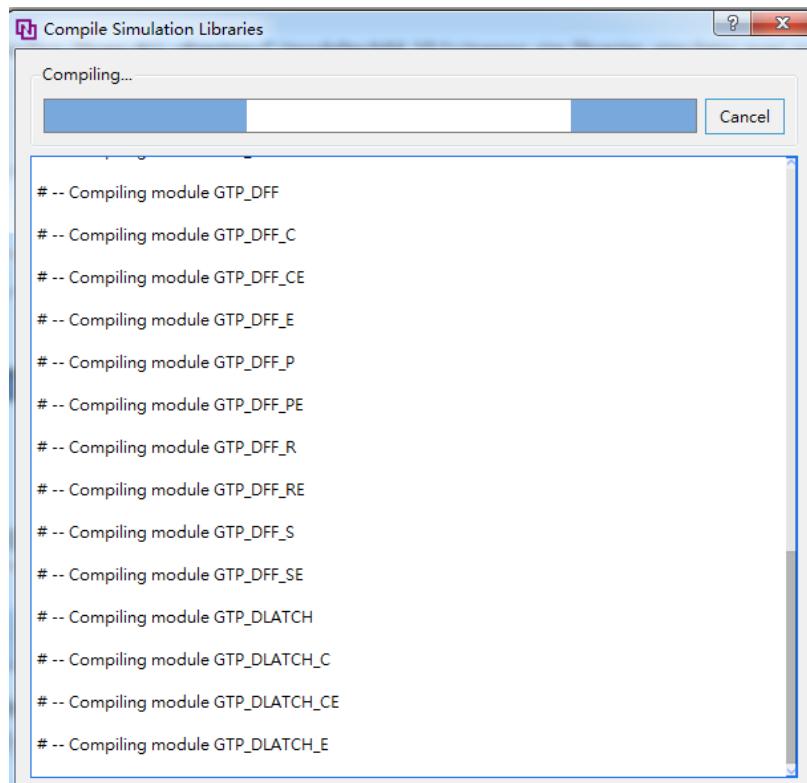

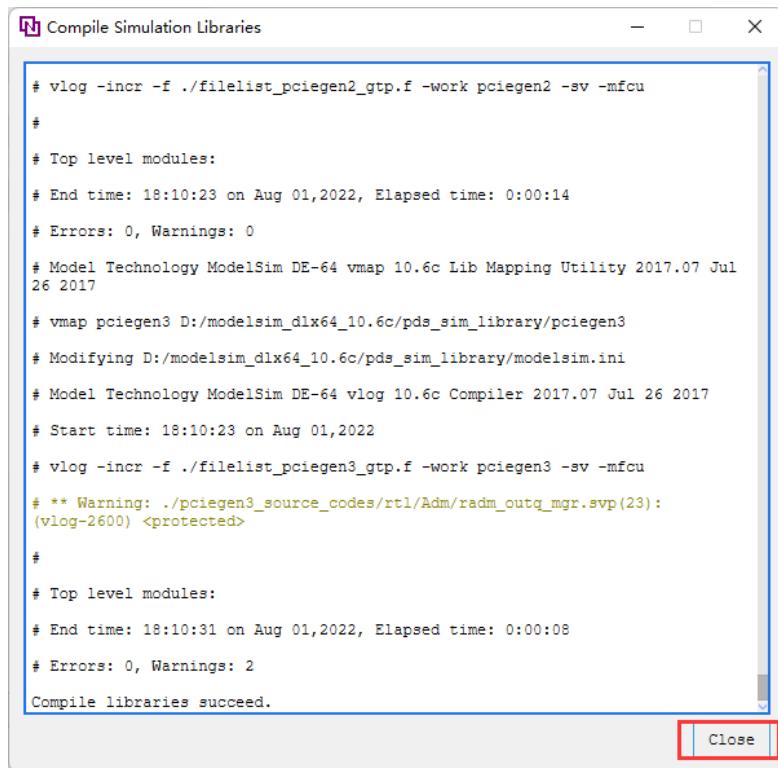

下面界面是开始进行编译, 编译成功后点击 Close 完成编译;

开始进行编译

```

# vlog -incr -f ./filelist_pciegen2_gtp.f -work pciegen2 -sv -mfcu

#

# Top level modules:

#

# End time: 18:10:23 on Aug 01,2022, Elapsed time: 0:00:14

#

# Errors: 0, Warnings: 0

#

# Model Technology ModelSim DE-64 vmap 10.6c Lib Mapping Utility 2017.07 Jul

# 26 2017

#

# vmap pciegen3 D:/modelsim_dlx64_10.6c/pds_sim_library/pciegen3

#

# Modifying D:/modelsim_dlx64_10.6c/pds_sim_library/modelsim.ini

#

# Model Technology ModelSim DE-64 vlog 10.6c Compiler 2017.07 Jul 26 2017

#

# Start time: 18:10:23 on Aug 01,2022

#

# vlog -incr -f ./filelist_pciegen3_gtp.f -work pciegen3 -sv -mfcu

#

# ** Warning: ./pciegen3_source_codes/rtl/Adm/radm_outq_mgr.svp(23):

# (vlog-2600) <protected>

#

# Top level modules:

#

# End time: 18:10:31 on Aug 01,2022, Elapsed time: 0:00:08

#

# Errors: 0, Warnings: 2

#

Compile libraries succeed.

```

编译完成

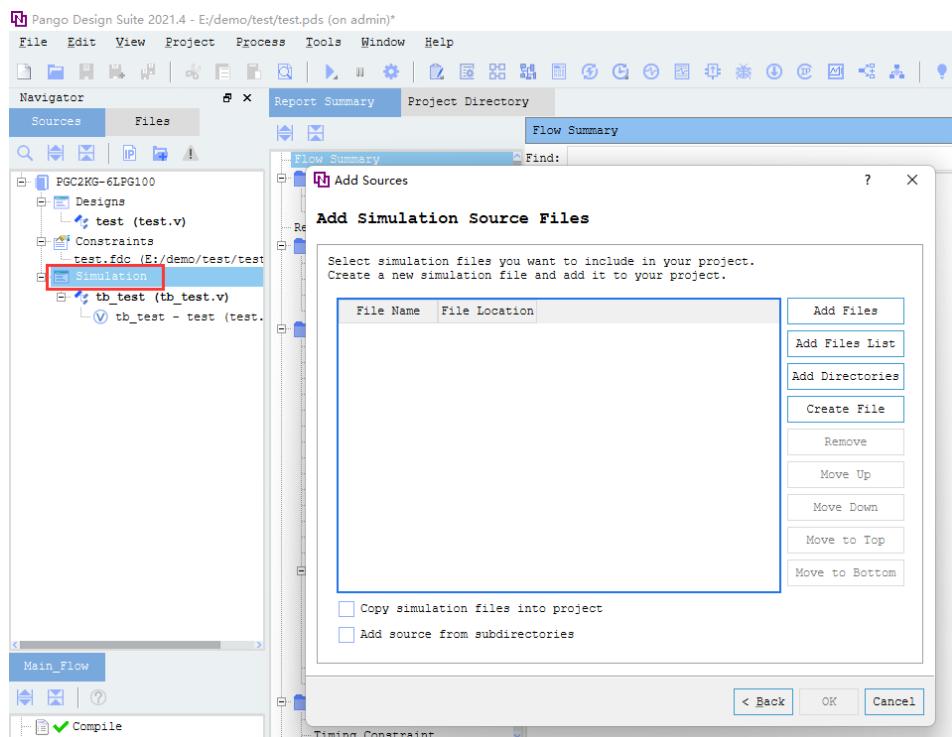

#### 4. 添加或新建 tb 文件

双击 Simulation，添加或新建 tb 文件。

添加或新建 tb 文件

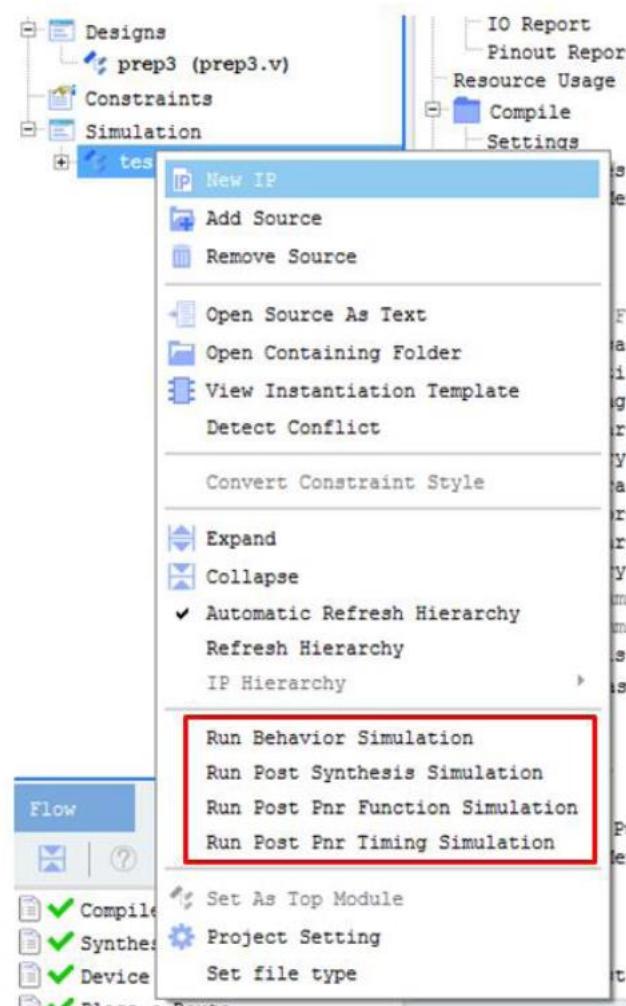

## 5. 联合仿真

在完成上述所有步骤后，右击 tb 文件，就可以进行联合仿真了。

右击 tb 文件进行联合仿真