# MES-LINEIN-MIC 硬件使用手册

版本日期：2024-02-18

Administrator: 深圳市小眼睛半导体科技有限公司

联系邮箱: [support@meyesemi.com](mailto:support@meyesemi.com)

QQ 群: 808770961

公司网址: [www.meyesemi.com](http://www.meyesemi.com)

微信公众号: 小眼睛 FPGA

购买渠道: [小眼睛半导体](#)

客服微信: 17665247134

## 产品简述

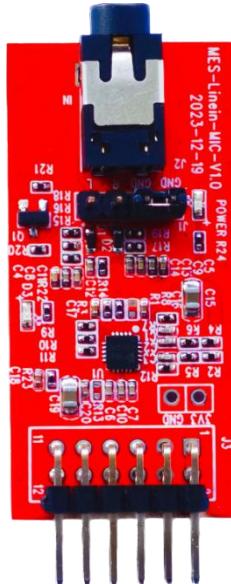

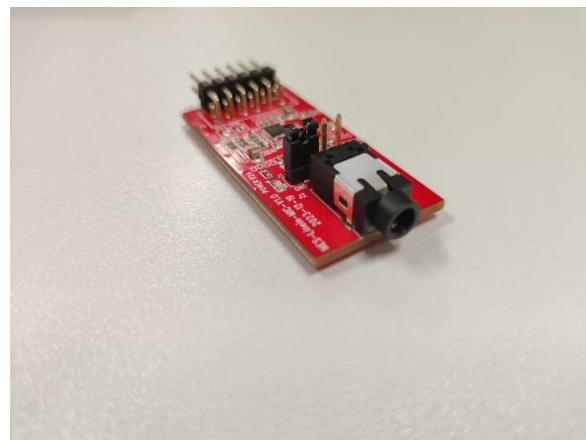

MES-Linein-MIC 是一款音频输入模块，接口为 3.5mm 的 3 环音频接口，该模块配备 ES7243E 音频芯片，可以接入音频源设备。

图 1 音频输入模块实物图

## 管脚说明

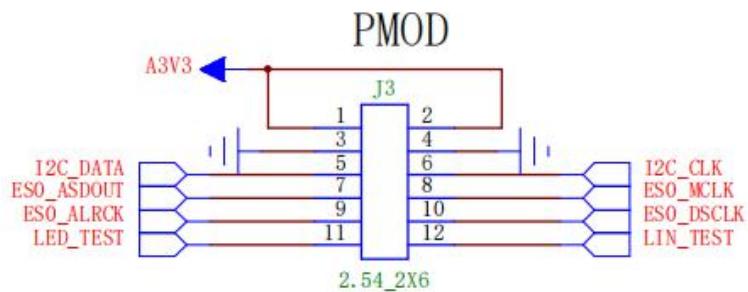

该模块可以通过 PMOD 扩展口连接到 FPGA 开发板上，接口电压 3.3V。

MES-Linein-MIC 原理图中 PMOD 扩展口对应管脚分布如图所示：

图 2 音频模块 PMOD 管脚分布图

在使用 FPGA 对管脚进行约束时，应注意电源和地的位置，根据它们的位置判断管脚的约束。

在配合“小眼睛科技”的 FPGA 开发板时，我们一般采用 PMOD 扩展板连接 FPGA 板卡与音频模块。PMOD 扩展板一共有四组 PMOD 接口，分别为 PMOD-A、

PMOD-B、PMOD-C、PMOD-D，使用这些接口连接音频输入模块时，信号与管脚的对应关系如下表所示：

（FPGA板卡以盘古50K板卡管脚为例）

| PMOD-A    |           |           |           |           |           |

|-----------|-----------|-----------|-----------|-----------|-----------|

| 信号名称      | 网络名称      | PGL50H 管脚 | 信号名称      | 网络名称      | PGL50H 管脚 |

| LED_TEST  | EX_IO_14N | U10       | LIN_TEST  | EX_IO_14P | T10       |

| ES0_ALRCK | EX_IO_13N | AB9       | ES0_DSCLK | EX_IO_13P | Y9        |

| ES0_ASOUT | EX_IO_17N | V9        | ES0_MCLK  | EX_IO_17P | U9        |

| I2C_DATA  | EX_IO_3N  | U8        | I2C_CLK   | EX_IO_3P  | T8        |

| PMOD-B    |           |           |           |           |           |

| 信号名称      | 网络名称      | PGL50H 管脚 | 信号名称      | 网络名称      | PGL50H 管脚 |

| LED_TEST  | EX_IO_15N | Y10       | LIN_TEST  | EX_IO_15P | W10       |

| ES0_ALRCK | EX_IO_16N | T11       | ES0_DSCLK | EX_IO_16P | R11       |

| ES0_ASOUT | EX_IO_7N  | Y12       | ES0_MCLK  | EX_IO_7P  | W12       |

| I2C_DATA  | EX_IO_8N  | U12       | I2C_CLK   | EX_IO_8P  | T12       |

| PMOD-C    |           |           |           |           |           |

| 信号名称      | 网络名称      | PGL50H 管脚 | 信号名称      | 网络名称      | PGL50H 管脚 |

| LED_TEST  | EX_IO_11N | AB13      | LIN_TEST  | EX_IO_11P | Y13       |

| ES0_ALRCK | EX_IO_9N  | AB11      | ES0_DSCLK | EX_IO_9P  | Y11       |

| ES0_ASOUT | EX_IO_10N | W11       | ES0_MCLK  | EX_IO_10P | V11       |

| I2C_DATA  | EX_IO_12N | AB10      | I2C_CLK   | EX_IO_12P | AA10      |

| PMOD-D    |           |           |           |           |           |

| 信号名称      | 网络名称      | PGL50H 管脚 | 信号名称      | 网络名称      | PGL50H 管脚 |

| LED_TEST  | EX_IO_4N  | W8        | LIN_TEST  | EX_IO_4P  | V7        |

| ES0_ALRCK | EX_IO_6N  | AB8       | ES0_DSCLK | EX_IO_6P  | AA8       |

| ES0_ASOUT | EX_IO_5N  | Y6        | ES0_MCLK  | EX_IO_5P  | W6        |

| I2C_DATA  | EX_IO_2N  | AB5       | I2C_CLK   | EX_IO_2P  | Y5        |

## 管脚描述

| 管脚名称      | 管脚描述                                           |

|-----------|------------------------------------------------|

| I2C_DATA  | I2C data                                       |

| I2C_CLK   | I2C clk                                        |

| ES0_ASOUT | Serial data output/I2C address AD2             |

| ES0_MCLK  | Master clock                                   |

| ES0_ALRCK | Serial data left and right channel frame clock |

| ES0_DSCLK | Serial data bit clock                          |

| LED_TEST  | 若此信号为高电平，插入后，MES-Linein-MIC 模块上的信号灯亮起          |

| LIN_TEST  | LIN_TEST 默认高电平，与 FPGA 连接后，为低电平状态               |

说明：

- 1、通过 I2C\_DATA、I2C\_CLK 对 ES7243E 音频芯片进行配置，配置详情请参考 ES7243E 音频芯片数据手册。

- 2、ES0\_ASOUT、ES0\_MCLK、ES0\_ALRCK、ES0\_DSCLK 为 I2S 信号，其中 ES0\_MCLK 是由 FPGA 提供，详情请参考 ES7243E 音频芯片数据手册。

- 3、ES0\_DSCLK 信号通过 PMOD 扩展口输入至 FPGA 中，属于普通 IO 作为时钟线使用的情况，所以需要对此管脚进行时钟约束。

## 功能描述

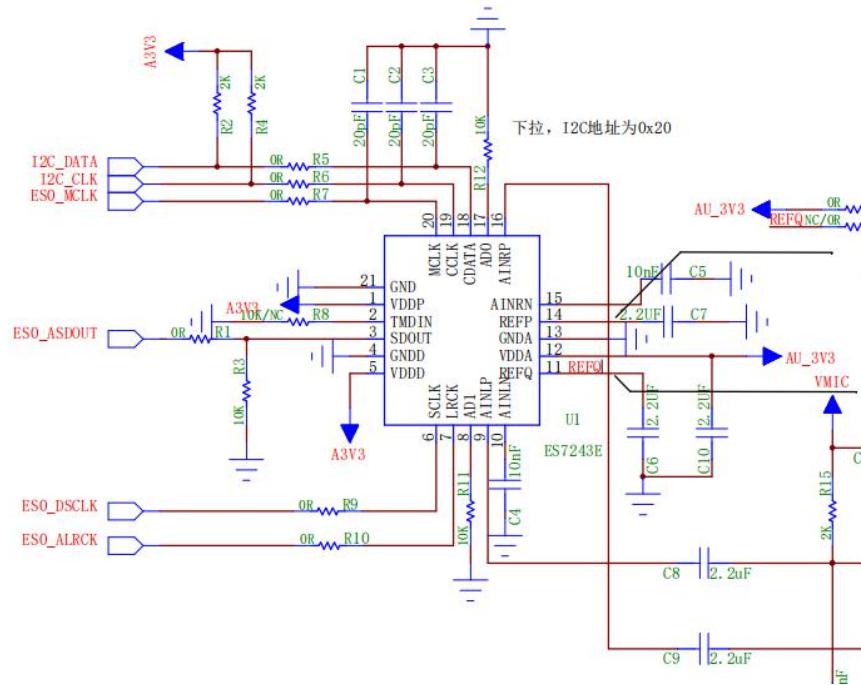

ES7243E 音频芯片的功能为：将音频模拟信号转换的音频数据。

AINLP 与 AINRP 分别时左右两声道的音频输入。

ES7243E 音频芯片在使用的时，需要先进行寄存器配置，寄存器配置可参考提供的 demo，demo 中配置的参数简述如下：

- 1、模式：master (LRCK 与 SCLK 由 ES7243E 输出)

- 2、音频采样率：48KHz

- 3、数据位宽：16bit

- 4、MCLK：12.288MHz (由 FPGA 提供)

提示：音频源的输出格式应与配置参数保持一致。

图 4 ES7243E 连接原理图

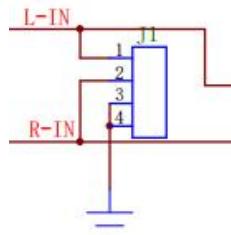

跳线帽座的功能为：连接左右声道。

此功能原因：常规的麦克风只有 1 个通道输入，通过跳帽将两个通道连接，可达到两个通道都输入的目的。

图 5 跳线帽座原理图

图 6 跳线帽实物图

说明：使用常规的麦克风时，一般只有 1 个通道音频信号输入至音频模块，如果不做处理，当 FPGA 输出音频时，也同样只有一个音道输出音频，如果想输出两个通道的音频信号，有两种方法：

- 1、通过跳线帽座，将 MIC 的左声道模拟输入与右声道模拟输入连接在一起。

- 2、信号输入至 FPGA 后，对数据进行处理，将音频信号复制一份，作为另一侧的音频输入数据。

提示：

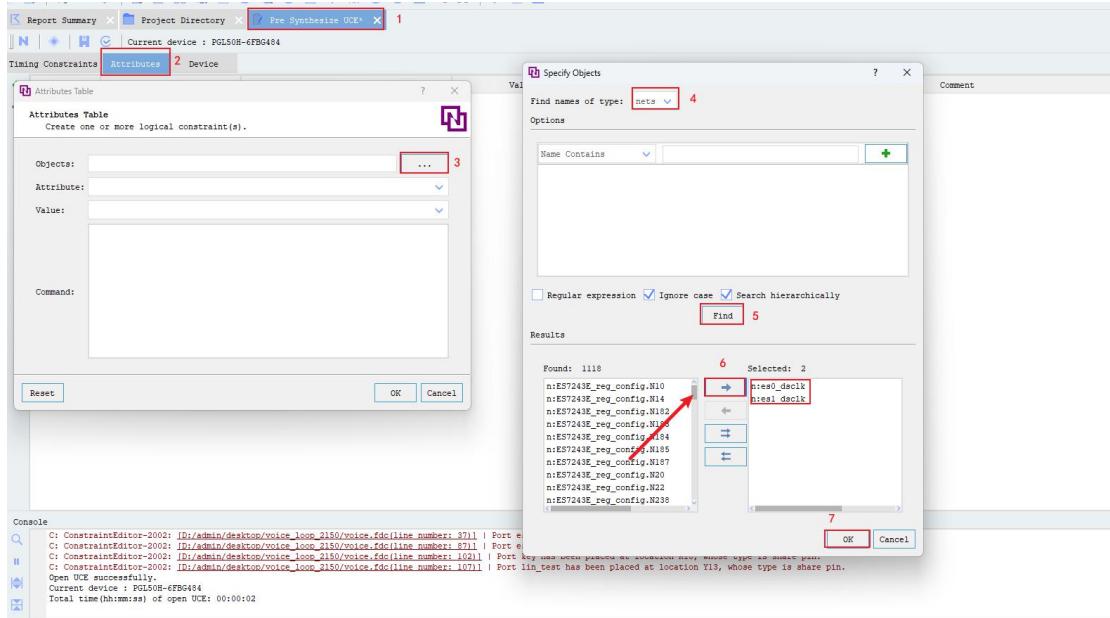

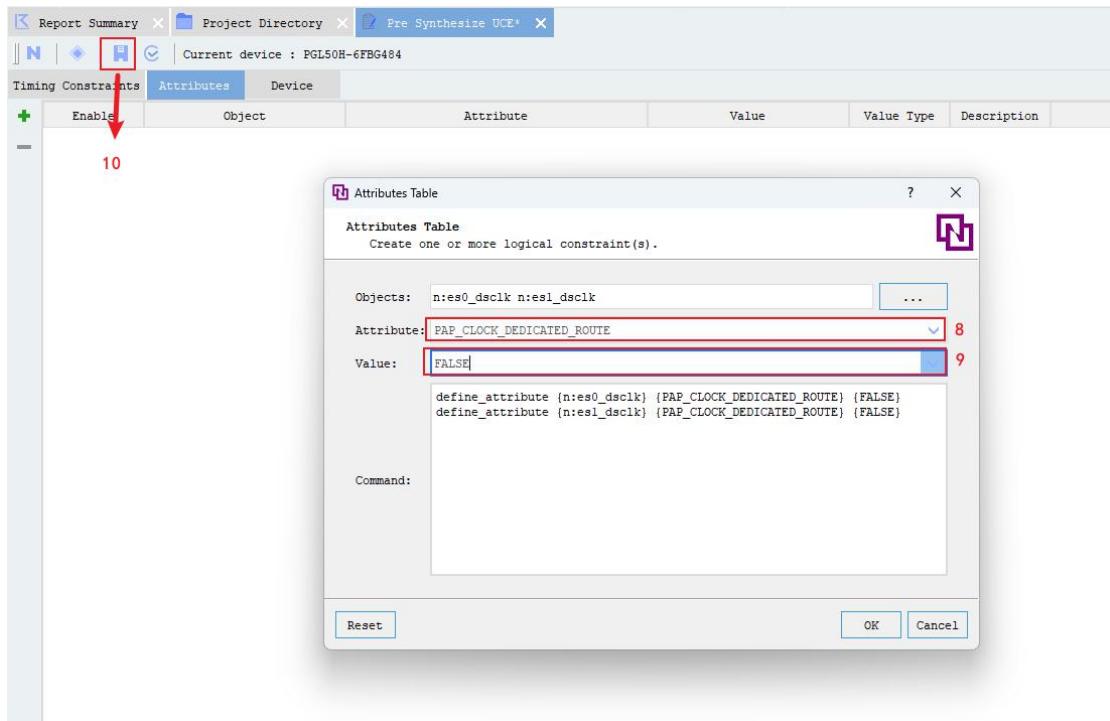

- 对 dsclk 信号进行时钟约束，可参考如下步骤：

图 7 时钟约束 1

图 8 时钟约束 2

- 音频源输出格式应与 ES7243E 芯片配置参数保持一致：

图 9 音频格式

- 音频输入模块连接三孔耳机线。

- 如遇噪声较大的情况，可将 FPGA 断电，重新插拔音频模块。