PG1K开发板使用问题

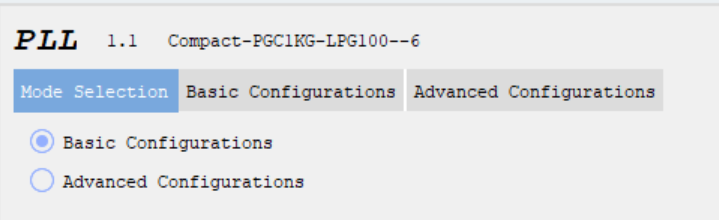

在测试PG1K的led_light例程时,输入时钟是40MHz,通过IP核工具添加PLL,相关参数设置如下:

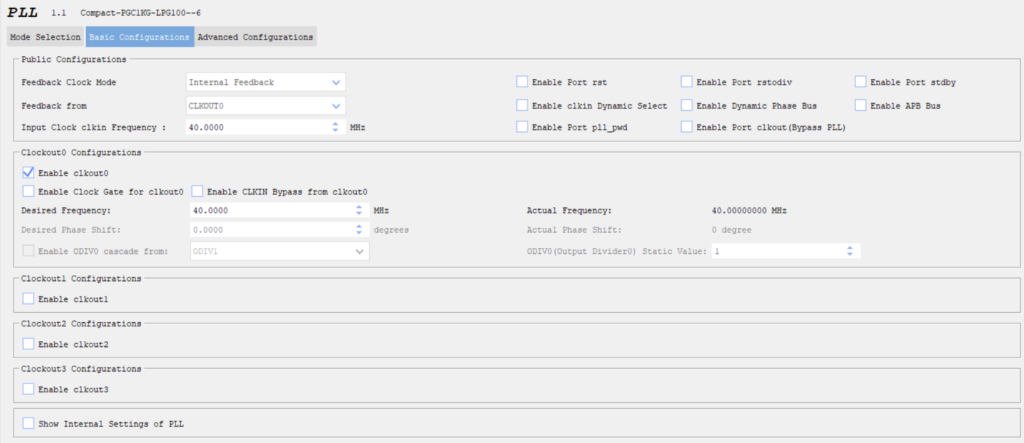

Generate编译成功如下

工程中例化PLL,代码如下

my_pll u_my_pll (

.clkout0(pllclk), // output

.lock(lock), // output

.clkin1(clk) // input

);

assign clk40 = pllclk; // clk

当使用原始clk,工程可以正常编译。

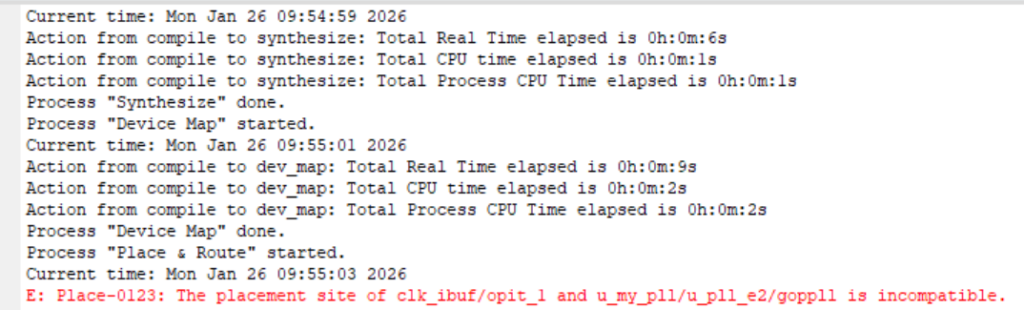

当使用pllclk时,会报如下错误

E: Place-0123: The placement site of clk_ibuf/opit_1 and u_my_pll/u_pll_e2/goppll is incompatible.

求问,这个问题如何解决?