在上一期中,我们已经把软件交叉编译环境(MounRiver Studio)和底层调试工具(OpenOCD)准备就绪了。但在 FPGA 的世界里,有句行话叫硬件搭台,软件唱戏。在我们用 C 语言给微控制器写程序之前,必须先把这颗微控制器的“肉体”——硬件逻辑底层,在紫光 FPGA 芯片中给“捏”出来。

今天,我们就手把手带你在 Pango Design Suite (PDS) 中从零搭建 SparrowRV 的硬件系统 。

一、从零开始:新建 PDS 硬件工程

首先,打开紫光同创的官方开发工具 Pango Design Suite。

1、新建工程: 点击 File -> New Project,输入工程名称(如 SparrowRV_SoC),确保路径全英文。

2、选择器件: 在器件选择界面,根据咱们的开发板(MES2L676-200HP-MINI)实际情况,精准选择芯片型号:PG2L200H-6FBB676。如果你使用的是其他型号的紫光板卡,请根据实际芯片丝印进行替换。

3、完成向导: 一路点击 Next 直到 Finish,一个空白的 FPGA 硬件工程就建好了。

二、 注入灵魂:导入 SparrowRV 源码

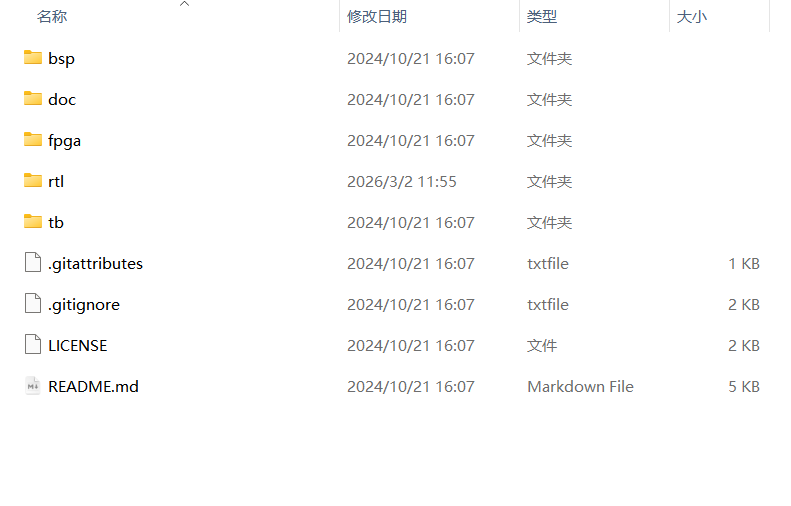

接下来,我们需要将开源软核的代码融入工程。打开你从 GitHub 或 Gitee 下载的 SparrowRV 源码包,你会看到一个名为 rtl 的文件夹,这里面存放的就是 RISC-V 软核的核心 Verilog 源码。

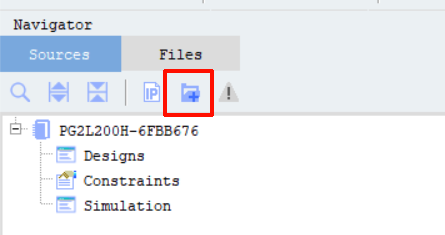

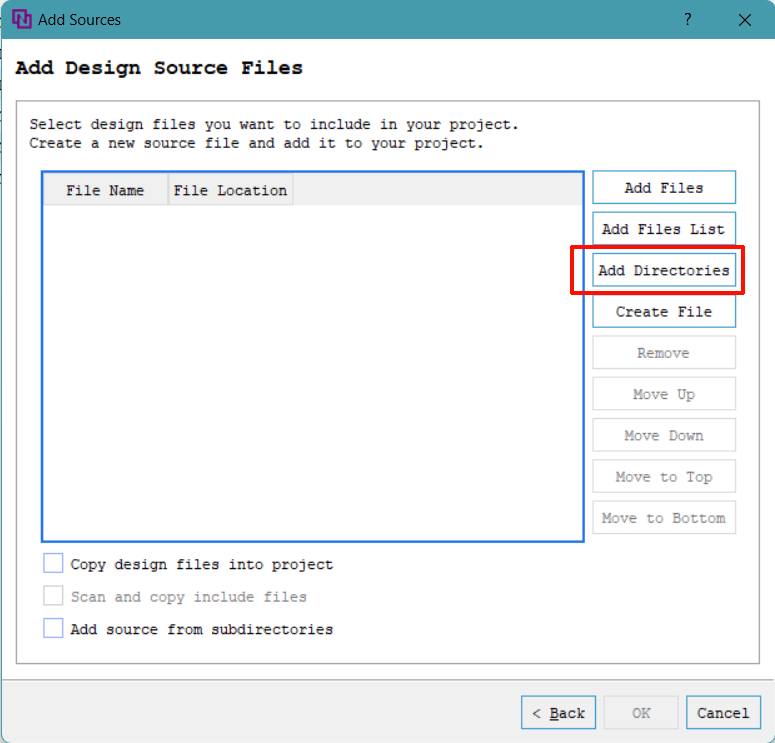

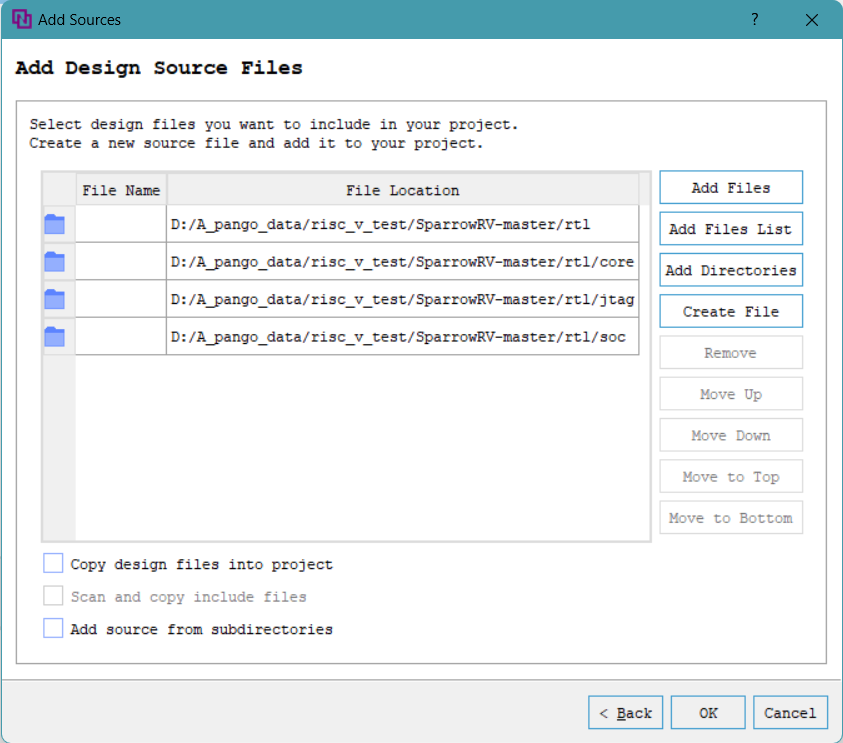

通过 PDS 的 Add Source 功能,将 rtl 文件夹下的所有 .v 文件添加到咱们的工程中。

1、打开GitHub/Gitee下载的文件,可以看到里面有很多文件

其中rtl为SparrowRV Verilog源码。

2、按照以下步骤把源码加入工程:

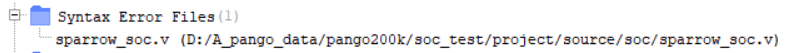

⚠️ 常见报错排查:头文件路径问题

在刚把代码加进工程时,可能会瞬间遇到一堆报错。不要慌张!这通常只是因为头文件(Include files)的相对路径不对导致的。

例如:下面这个文件,

解决方法: 以报错找不到 defines.v 为例。你需要先确认 defines.v 存放在工程的哪个物理目录下。 假设你的工程中,defines.v 放在了 rtl 文件夹里,而报错提示找不到该文件的源码在 soc 文件夹里,你只需要打开报错的那份源码,将文件头部的包含语句修改为相对路径即可:

// 修改前:工具在当前目录找不到该文件

`include "defines.v"

// 修改后:指引工具返回上一级并进入 rtl 目录寻找

`include "../rtl/defines.v"按照这个思路,耐心将几个报错的 include 路径修正,整个工程就能顺利解析了。

三、 核心定制:修改 config.v 配置文件

在硬件开发中,我们通常通过宏定义来开关特定的硬件电路。打开工程中的 config.v 文件,根据咱们的实际需求进行修改:

1、匹配系统时钟频率

咱们教程使用的板卡外部输入时钟是 27MHz,你需要将时钟参数修改为与硬件一致:

// 根据板载晶振实际情况修改,这里设为27MHz

`define CPU_CLOCK_HZ 270000002、设置端口数量

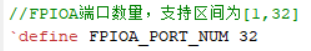

在 SparrowRV 中,软核的外设接口(如 UART、SPI、PWM 等)并不是在底层硬件中写死对应某个物理引脚的,而是通过 FPIOA(灵活可编程 IO 阵列) 动态映射的。这意味着,你可以等到了写 C 语言代码的时候,再决定哪个引脚做串口、哪个引脚点亮 LED。

根据咱们开发板上实际引出的 IO 资源,本教程在此规划了 32 个引脚作为 FPIOA 端口(这与我们在管脚约束文件里绑定的 fpioa[0] ~ fpioa[31] 是一一对应的)

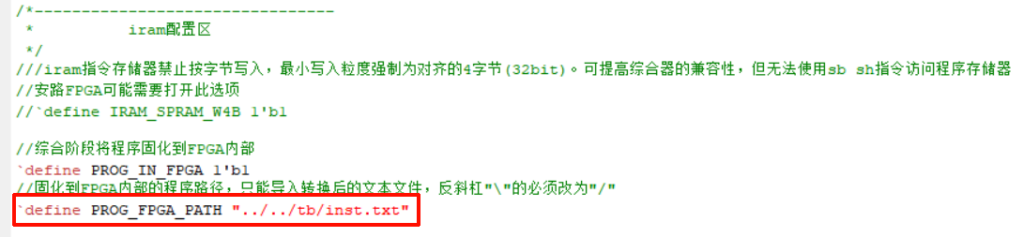

3、确定程序烧录模式

模式 A(BRAM 固化): SparrowRV 的程序可以转化为机器码文本(.txt),在 FPGA 综合阶段直接作为初始化数据写入 BRAM,跟着 .bit 比特流一起下载到板卡上。此时需要注意配置文件中初始化的文本路径是否正确(在下一章我会详细教大家如何生成这个 .txt 文件)。

SparrowRV的程序可以通过跟源码一起综合生成比特流下载到板卡上:

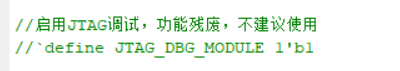

模式 B(J-Link ): 如果你打算使用 J-Link 调试器在线下载程序,则需要确保 JTAG 调试模块被开启(取消注释):(虽然JTAG不能调试,但是可以下载程序)

3、其他配置

四、 骨骼绑定:管脚与时序约束

写完了逻辑,还需要告诉 FPGA 内部逻辑对应外部的哪根物理引脚。 (注:紫光 PDS 使用的是 .fdc 格式的物理约束文件。下方为你梳理了标准的紫光 PDS 约束语法模板,大家可以直接将其保存为 soc.fdc 并添加到工程中)

#时序约束

create_clock -period {37.037} [get_ports {clk}] -name clk

# JTAG时钟约束 (10MHz, 100ns周期)

create_clock -period {100.000} [get_ports {JTAG_TCK}] -name JTAG_CLK

# 异步时钟域声明

set_clock_groups -asynchronous -group [get_clocks {clk}] -group [get_clocks {JTAG_CLK}]

#IO引脚约束

#----------------------系统时钟---------------------------

define_attribute {p:clk} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:clk} {PAP_IO_LOC} {D18}

define_attribute {p:clk} {PAP_IO_VCCIO} {3.3}

define_attribute {p:clk} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------系统复位---------------------------

define_attribute {p:hard_rst_n} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:hard_rst_n} {PAP_IO_LOC} {C22}

define_attribute {p:hard_rst_n} {PAP_IO_VCCIO} {3.3}

define_attribute {p:hard_rst_n} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------LED---------------------------

define_attribute {p:core_active} {PAP_IO_DIRECTION} {OUTPUT}

define_attribute {p:core_active} {PAP_IO_LOC} {A20}

define_attribute {p:core_active} {PAP_IO_VCCIO} {3.3}

define_attribute {p:core_active} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------JTAG---------------------------

# JTAG_TDI: 扩展口4 -> J10: R20

define_attribute {p:JTAG_TDI} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:JTAG_TDI} {PAP_IO_LOC} {R20}

define_attribute {p:JTAG_TDI} {PAP_IO_VCCIO} {3.3}

define_attribute {p:JTAG_TDI} {PAP_IO_STANDARD} {LVCMOS33}

# JTAG_TMS: 扩展口6 -> J10: P19

define_attribute {p:JTAG_TMS} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:JTAG_TMS} {PAP_IO_LOC} {P19}

define_attribute {p:JTAG_TMS} {PAP_IO_VCCIO} {3.3}

define_attribute {p:JTAG_TMS} {PAP_IO_STANDARD} {LVCMOS33}

# JTAG_TCK: 扩展口8 -> J10: M24

define_attribute {p:JTAG_TCK} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:JTAG_TCK} {PAP_IO_LOC} {M24}

define_attribute {p:JTAG_TCK} {PAP_IO_VCCIO} {3.3}

define_attribute {p:JTAG_TCK} {PAP_IO_STANDARD} {LVCMOS33}

# JTAG_TDO: 扩展口10 -> J10: T24

define_attribute {p:JTAG_TDO} {PAP_IO_DIRECTION} {OUTPUT}

define_attribute {p:JTAG_TDO} {PAP_IO_LOC} {T24}

define_attribute {p:JTAG_TDO} {PAP_IO_VCCIO} {3.3}

define_attribute {p:JTAG_TDO} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------SD---------------------------

# sd_dat[0]: 扩展口3 -> J10: R21

define_attribute {p:sd_dat[0]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:sd_dat[0]} {PAP_IO_LOC} {R21}

define_attribute {p:sd_dat[0]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_dat[0]} {PAP_IO_STANDARD} {LVCMOS33}

# sd_dat[1]: 扩展口5 -> J10: N19

define_attribute {p:sd_dat[1]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:sd_dat[1]} {PAP_IO_LOC} {N19}

define_attribute {p:sd_dat[1]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_dat[1]} {PAP_IO_STANDARD} {LVCMOS33}

# sd_dat[2]: 扩展口7 -> J10: M25

define_attribute {p:sd_dat[2]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:sd_dat[2]} {PAP_IO_LOC} {M25}

define_attribute {p:sd_dat[2]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_dat[2]} {PAP_IO_STANDARD} {LVCMOS33}

# sd_dat[3]: 扩展口9 -> J10: T25

define_attribute {p:sd_dat[3]} {PAP_IO_DIRECTION} {INPUT}

define_attribute {p:sd_dat[3]} {PAP_IO_LOC} {T25}

define_attribute {p:sd_dat[3]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_dat[3]} {PAP_IO_STANDARD} {LVCMOS33}

# sd_cmd: 扩展口11 -> J10: R22

define_attribute {p:sd_cmd} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:sd_cmd} {PAP_IO_LOC} {R22}

define_attribute {p:sd_cmd} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_cmd} {PAP_IO_STANDARD} {LVCMOS33}

# sd_clk: 扩展口13 -> J10: K26

define_attribute {p:sd_clk} {PAP_IO_DIRECTION} {OUTPUT}

define_attribute {p:sd_clk} {PAP_IO_LOC} {K26}

define_attribute {p:sd_clk} {PAP_IO_VCCIO} {3.3}

define_attribute {p:sd_clk} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------FPIOA---------------------------

#----------------------uart0---------------------------

#TX

define_attribute {p:fpioa[0]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[0]} {PAP_IO_LOC} {C24}

define_attribute {p:fpioa[0]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[0]} {PAP_IO_STANDARD} {LVCMOS33}

#RX

define_attribute {p:fpioa[1]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[1]} {PAP_IO_LOC} {B24}

define_attribute {p:fpioa[1]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[1]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------uart1---------------------------

# fpioa[2]: 扩展口12 -> J10: T22

define_attribute {p:fpioa[2]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[2]} {PAP_IO_LOC} {T22}

define_attribute {p:fpioa[2]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[2]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[3]: 扩展口14 -> J10: K25

define_attribute {p:fpioa[3]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[3]} {PAP_IO_LOC} {K25}

define_attribute {p:fpioa[3]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[3]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------spi0---------------------------

# fpioa[4]: 扩展口18 -> J10: L22

define_attribute {p:fpioa[4]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[4]} {PAP_IO_LOC} {L22}

define_attribute {p:fpioa[4]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[4]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[5]: 扩展口20 -> J10: Y25

define_attribute {p:fpioa[5]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[5]} {PAP_IO_LOC} {Y25}

define_attribute {p:fpioa[5]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[5]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[6]: 扩展口22 -> J10: AA24

define_attribute {p:fpioa[6]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[6]} {PAP_IO_LOC} {AA24}

define_attribute {p:fpioa[6]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[6]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[7]: 扩展口24 -> J10: AB24

define_attribute {p:fpioa[7]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[7]} {PAP_IO_LOC} {AB24}

define_attribute {p:fpioa[7]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[7]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------led---------------------------

define_attribute {p:fpioa[8]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[8]} {PAP_IO_LOC} {C19}

define_attribute {p:fpioa[8]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[8]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[9]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[9]} {PAP_IO_LOC} {C18}

define_attribute {p:fpioa[9]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[9]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[10]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[10]} {PAP_IO_LOC} {E18}

define_attribute {p:fpioa[10]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[10]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[11]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[11]} {PAP_IO_LOC} {A17}

define_attribute {p:fpioa[11]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[11]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------按键---------------------------

define_attribute {p:fpioa[12]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[12]} {PAP_IO_LOC} {C23}

define_attribute {p:fpioa[12]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[12]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[13]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[13]} {PAP_IO_LOC} {B22}

define_attribute {p:fpioa[13]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[13]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[14]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[14]} {PAP_IO_LOC} {A22}

define_attribute {p:fpioa[14]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[14]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:fpioa[15]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[15]} {PAP_IO_LOC} {B20}

define_attribute {p:fpioa[15]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[15]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------pwm---------------------------

# fpioa[16]: 扩展口17 -> J10: L23

define_attribute {p:fpioa[16]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[16]} {PAP_IO_LOC} {L23}

define_attribute {p:fpioa[16]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[16]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[17]: 扩展口19 -> J10: AA25

define_attribute {p:fpioa[17]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[17]} {PAP_IO_LOC} {AA25}

define_attribute {p:fpioa[17]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[17]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[18]: 扩展口21 -> J10: AB25

define_attribute {p:fpioa[18]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[18]} {PAP_IO_LOC} {AB25}

define_attribute {p:fpioa[18]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[18]} {PAP_IO_STANDARD} {LVCMOS33}

#----------------------gpio---------------------------

# fpioa[19]: 扩展口23 -> J10: AC24

define_attribute {p:fpioa[19]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[19]} {PAP_IO_LOC} {AC24}

define_attribute {p:fpioa[19]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[19]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[20]: 扩展口25 -> J10: R23

define_attribute {p:fpioa[20]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[20]} {PAP_IO_LOC} {R23}

define_attribute {p:fpioa[20]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[20]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[21]: 扩展口26 -> J10: T23

define_attribute {p:fpioa[21]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[21]} {PAP_IO_LOC} {T23}

define_attribute {p:fpioa[21]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[21]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[22]: 扩展口27 -> J10: P26

define_attribute {p:fpioa[22]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[22]} {PAP_IO_LOC} {P26}

define_attribute {p:fpioa[22]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[22]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[23]: 扩展口28 -> J10: R26

define_attribute {p:fpioa[23]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[23]} {PAP_IO_LOC} {R26}

define_attribute {p:fpioa[23]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[23]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[24]: 扩展口29 -> J10: M26

define_attribute {p:fpioa[24]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[24]} {PAP_IO_LOC} {M26}

define_attribute {p:fpioa[24]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[24]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[25]: 扩展口30 -> J10: N26

define_attribute {p:fpioa[25]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[25]} {PAP_IO_LOC} {N26}

define_attribute {p:fpioa[25]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[25]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[26]: 扩展口31 -> J10: M22

define_attribute {p:fpioa[26]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[26]} {PAP_IO_LOC} {M22}

define_attribute {p:fpioa[26]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[26]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[27]: 扩展口32 -> J10: M21

define_attribute {p:fpioa[27]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[27]} {PAP_IO_LOC} {M21}

define_attribute {p:fpioa[27]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[27]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[28]: 扩展口33 -> J10: U26

define_attribute {p:fpioa[28]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[28]} {PAP_IO_LOC} {U26}

define_attribute {p:fpioa[28]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[28]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[29]: 扩展口34 -> J10: U25

define_attribute {p:fpioa[29]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[29]} {PAP_IO_LOC} {U25}

define_attribute {p:fpioa[29]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[29]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[30]: 扩展口35 -> J10: AC26

define_attribute {p:fpioa[30]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[30]} {PAP_IO_LOC} {AC26}

define_attribute {p:fpioa[30]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[30]} {PAP_IO_STANDARD} {LVCMOS33}

# fpioa[31]: 扩展口36 -> J10: AB26

define_attribute {p:fpioa[31]} {PAP_IO_DIRECTION} {INOUT}

define_attribute {p:fpioa[31]} {PAP_IO_LOC} {AB26}

define_attribute {p:fpioa[31]} {PAP_IO_VCCIO} {3.3}

define_attribute {p:fpioa[31]} {PAP_IO_STANDARD} {LVCMOS33}

define_attribute {p:JTAG_TDO} {PAP_IO_SLEW} {FAST}

define_attribute {p:JTAG_TCK} {PAP_IO_NONE} {TRUE}

define_attribute {p:JTAG_TDI} {PAP_IO_NONE} {TRUE}

define_attribute {p:JTAG_TMS} {PAP_IO_NONE} {TRUE}

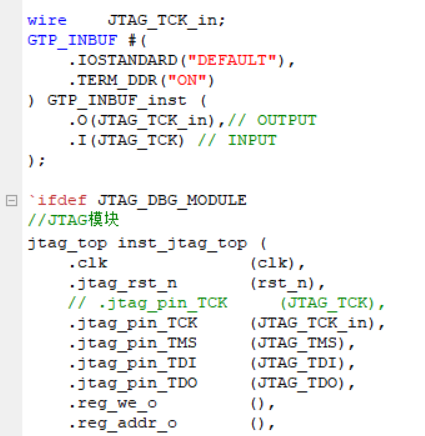

define_attribute {n:JTAG_TCK_in} {PAP_CLOCK_DEDICATED_ROUTE} {false}注意:全局时钟缓冲原语 (GTP_INBUF)

由于我把 JTAG 的 TCK 时钟引脚接到了开发板的普通 IO 口(而非专用的全局时钟管脚),如果直接将这个信号接入软核作为时钟使用,会导致布线延迟严重,极易产生时序违例甚至无法识别 target。

为此,我们在顶层 Verilog 中必须手动调用紫光同创的底层原语 GTP_INBUF,对这个普通的 IO 输入进行缓冲,将其强行拉入 FPGA 的全局时钟网络:

wire JTAG_TCK_in;

// 调用紫光原语,对普通的 JTAG_TCK 输入引脚进行缓冲

GTP_INBUF #(

.IOSTANDARD("DEFAULT"),

.TERM_DDR("ON")

) GTP_INBUF_inst (

.O(JTAG_TCK_in), // 输出:接入全局时钟网络的优质时钟信号

.I(JTAG_TCK) // 输入:来自普通物理 IO 的原始时钟

);

// 同时在约束文件中,需要放宽对该普通管脚上专用时钟路由的限制

//define_attribute {n:JTAG_TCK_in} {PAP_CLOCK_DEDICATED_ROUTE} {false}经过这样的处理,软核内部的 JTAG 逻辑就能获得极其稳定的时钟驱动了!

到这里,咱们 SparrowRV 的硬件躯壳就已经完美构建并约束好了。点击 PDS 的 Generate Bitstream,让工具开始综合布线吧!

在下一章中,我将手把手教大家如何利用 MRS 编写 C 语言程序,生成机器码 .txt 文件,并把它灌入我们今天搭好的硬件系统中去。敬请期待!