时钟信号从非时钟管脚输入出现报错

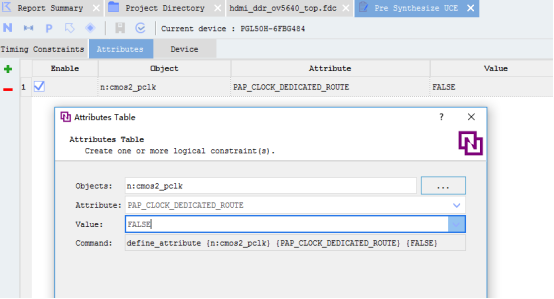

解决方法:物理约束增加PAP_CLOCK_DEDICATED_ROUTE属性约束

在用户在做 IO 约束的过程中,如 果将 clock 端口放置到了非专用时钟端口,则 place 阶段会给出报错提示从而停 止 flow,如果用户希望 flow 继续运行,则可以将该时钟相关的 net 或该 net 的驱 动 pin 脚设置该属性为 FALSE,流程就会将报错调整为警告,从而继续运行流程 而不会停止。

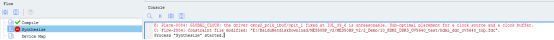

设置保存后,在 PNR 阶段就不会上报时钟端口没有从clock pad输入上时钟网络的Error,只会报Critical Warning(例如:C: Place-2028: GLOBAL_CLOCK: the driver clk_ibuf/opit_1 fixed at IOLHR_16_1008 is unreasonable. Sub-optimal placement for a clock source and a clock buffer.)

没有回复内容