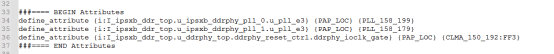

从demo移植DDR3模块,出现时钟规划失败,报错:

Place-0084: IO_CLOCK: the driver DDR3/u_ipsxb_ddrphy_pll_0/u_pll_e3/goppll fixed at PLL_158_179 is unreasonable. Sub-optimal placement for a clock source and a clock buffer.

移植DDR3模块时若复制demo中的PLL约束到新的工程中,应该注意约束语句中的路径,,将路径改成新工程中的路径

没有回复内容