大家好,

最近在项目中使用FPGA写DDR3,rgb屏读DDR3显示,从最初的一脸懵逼到后来成功跑通,中间踩了不少坑。论坛里虽然有很多零散的知识点,但缺乏一个比较系统的总结。因此,我把这段时间的学习和实践经验整理出来,希望能给正在做类似项目的朋友一些参考。

目前主流FPGA厂商都提供了成熟的DDR控制器IP核,这极大地降低了我们的开发难度。

| FPGA厂商 | IP核名称 | 说明 |

|---|---|---|

| AMD (Xilinx) | MIG MemoryInterfaceGenerator | 支持7系列及以上的UltraScale/UltraScale+器件,可配置为AXI4或Native接口 。 |

| Altera Intel | EMIF ExternalMemoryInterface | 对应器件手册中的External Memory Interfaces IP。 |

| 高云 Gowin | DDR3 / DDR4 IP | 在国产FPGA中,其时钟和复位逻辑与Xilinx略有不同,需特别注意 。 |

配置时的小Tips:

-

时钟至关重要:一定要确保提供给IP核的参考时钟(Reference Clock)和系统时钟(System Clock)频率准确、稳定。特别是对于高云FPGA,PLL的LOCK信号必须正确连接到IP核,否则初始化肯定失败 。

-

引脚分配:如果使用非官方开发板(自主画板),在MIG/EMIF配置界面中,一定要仔细核对引脚分配(Pinout)是否与PCB原理图一致。地址线、Bank、数据组的对应关系不能错 。

-

兼容第三方颗粒:如果使用的DDR颗粒不在IP核的默认列表中(例如使用ISSI或国产颗粒),通常可以通过导入自定义的

CSV参数文件来解决。需要对照颗粒的数据手册,填写tCK、tRCD、tWR等关键时序参数 。

在设计复杂系统时,直接操作DDR控制器IP核的接口往往过于复杂且容易出错。为此,我将DDR底层控制器封装成了一个用户友好的读写模块。

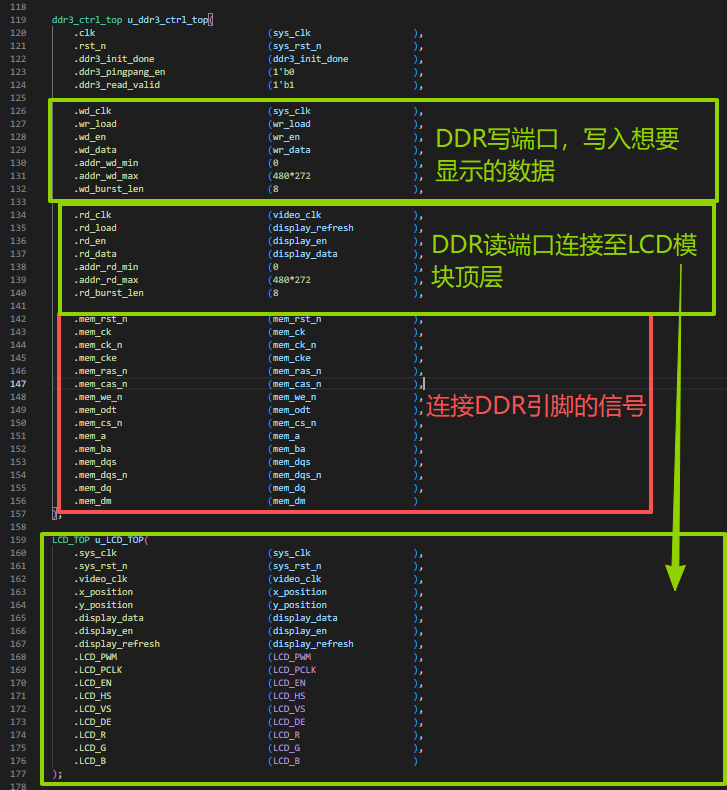

该模块的对外接口被简化,其操作逻辑与FIFO类似,用户无需关心DDR复杂的刷新、 bank管理及时序握手等细节。如图所示,封装后的模块主要分为三组信号:

-

写端口:连接数据写入的源端(如UI绘制模块)。

-

读端口:连接数据读取的输出端(如RGB显示驱动模块)。

-

DDR管教信号:直接连接至FPGA的Bank引脚,与外部DDR颗粒进行物理通信。

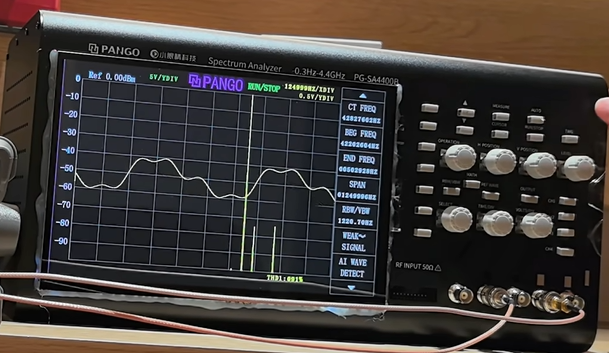

在实际应用中,只需将RGB显示模块挂载到DDR模块的读端口,同时将负责UI绘制的模块挂载到写端口,即可轻松实现屏幕驱动与UI显示。这种架构不仅降低了设计复杂度,也保证了显示数据流的流畅性。下图为该方案驱动RGB屏幕的实际显示效果。

(下图为rgb屏幕显示效果)

-

没有回复内容