集十年匠心之力,创芯辰大海之梦。2026第十届全国大学生集成电路创新创业大赛(简称:集创赛)战鼓擂动,新程再启!作为国内集成电路领域规模最大的高校赛事,也是中国高等教育学会全国高校竞赛排行榜中唯一入选的集成电路专业赛事,集创赛始终以产业需求为导向,以人才培养为根基,致力于构建产学研用融合的创新平台,为我国集成电路产业的自主创新与长远发展注入蓬勃的青春动力。

作为国产FPGA核心力量,紫光同创始终以赋能未来工程师为己任,深度构建从芯片到生态的创新循环。紫光同创赛道精心设计的实战项目,直指产业核心需求与前沿趋势,本届赛题聚焦智能交通感知系统,充分发挥国产FPGA在实时性与能效方面的优势,为智能交通边缘计算节点提供自主可控、高效可靠的感知解决方案。通过“芯片+场景”的深度融合,探索国产高端芯片在关键基础设施领域的创新应用路径,洞见更安全、更高效、更智能的未来交通图景!

作为紫光同创生态合作伙伴,小眼睛科技将继续为2026紫光同创杯赛提供全维度的技术护航,让每一份创意都能获得坚实支撑,从核心工具使用、设计优化到调试技巧,小眼睛科技资深技术团队将全程陪伴,精准赋能。这不仅是技术的比拼,更是视野的开阔、思维的锻造与产业的初探。加入我们,期待您以代码为刃,以逻辑为尺,在这片充满无限可能的芯版图上,刻下属于自己的创新坐标!

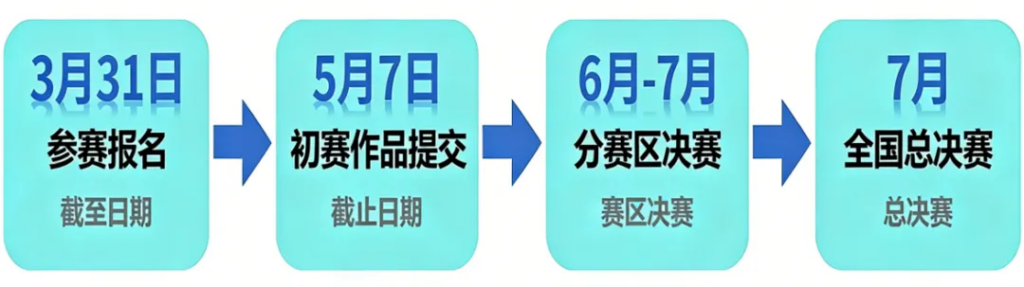

01 /2026集创赛日程安排

赛事关键节点

请登陆2026集创赛官网报名:http://univ.ciciec.com/

02 /2026紫光同创杯赛题

一、题目名称:基于紫光同创FPGA的智能交通感知系统

二、参赛组别:A组、B组

三、赛题内容

随着城市的迅速发展,城市交通环境也变得更加复杂,行人行为及车牌识别作为智能交通的核心感知技术,在车辆通行管理、交通违章抓拍、ETC闸机、停车场自动化运维等场景中具有不可替代的作用。传统基于CPU/GPU 的行人和车牌识别方案存在实时性不足、功耗较高、部署灵活性受限等问题,而FPGA+MCU凭借并行计算架构、低延迟、高性价比的优势,成为嵌入式场景下智能交通感知系统的理想硬件平台。

四、赛题要求

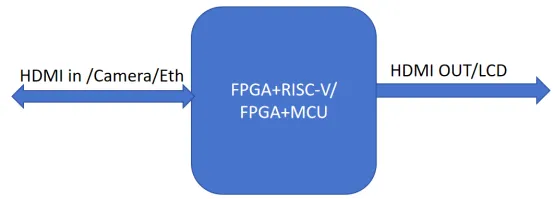

1、基于紫光同创FPGA芯片,采用纯逻辑方案或移植RISC-V的软核(提供RISC-V参考),或采用ARM+紫光同创FPGA方案(ARM的处理性能不应超过RK3568),完成包含图像采集接口(HDMI或者摄像头输入)、预处理模块、车牌识别、结果输出的硬件架构;

2、关键算法硬件实现:

(1)图像预处理:基于FPGA 实现图像灰度化、降噪(如中值滤波、高斯滤波)、二值化等算法,解决复杂光照(强光、阴影)、模糊等场景下的图像质量问题;

(2)车牌定位与识别:通过边缘检测、形态学操作、颜色分割等算法,在FPGA 中并行实现车牌区域快速提取,或者基于AI算法模型进行车牌的识别和定位,支持蓝牌、绿牌等常见车牌和特殊车牌;

(3)车牌定义:本文车牌特指机动车号牌,其相关标准参考《中华人民共和国机动车号牌》(GA 36-2018)标准。其蓝牌和绿牌分别为小型汽车号牌和绿牌指小型新能源车号牌,在本文中认定为常见车牌;大黄牌(大型汽车号牌)、小黄牌(摩托车号牌)、警用号牌、挂车号牌、领馆号牌、使馆号牌等类型认定为特殊车牌。

3、系统集成与验证

(1)搭建硬件实验平台:连接FPGA 开发板与图像采集模块(HDMI、摄像头、以太网的一种或几种)、显示模块(LCD/HDMI)、存储模块(SD卡),实现图像采集-处理-识别-结果输出的全流程闭环;

(2)软件辅助设计:使用Verilog/VHDL语言编写硬件逻辑代码,或搭配RISC-V嵌入式软核(或ARM)实现系统控制与数据交互;

(3)功能与性能测试

A.在不同场景(晴天、阴天、夜间、远距离、倾斜角度)下采集测试样本,验证系统识别准确率、识别延迟、实时帧率等指标;

B.支持特殊车牌识别;

C.低功耗优化设计,适配嵌入式移动场景。

五、作品提交要求

2、初赛评审:参赛团队应提前在远程训练平台完成FPGA开发基础能力测评考核后根据赛题要求提交相关材料,能力测评考核仅作为参赛团队成员技术水平的客观评价依据,考核结果不予计分,但未通过测评考核的团队不予参加初赛。该平台相关要求和使用规则将于本命题钉钉交流群发布。

远程平台链接(拟在3月左右开放):https://szlogicmatrix.com/

3、决赛现场评审:分赛区决赛及全国总决赛比赛现场由企业统一提供HDMI输入的图片或视频和SD卡输入的图片或视频,参赛者根据现场提供的交通视频进行识别与标记。

4、供现场实测的车牌照片可能形式包括:

(1)一张图片内呈现单个或多个车牌特写,即除车牌外图片内其余部分为单一底色。

(2)现场实拍照片,即图片出现单个或多个车牌,其角度、尺寸、数量等参数皆不做标准限定。

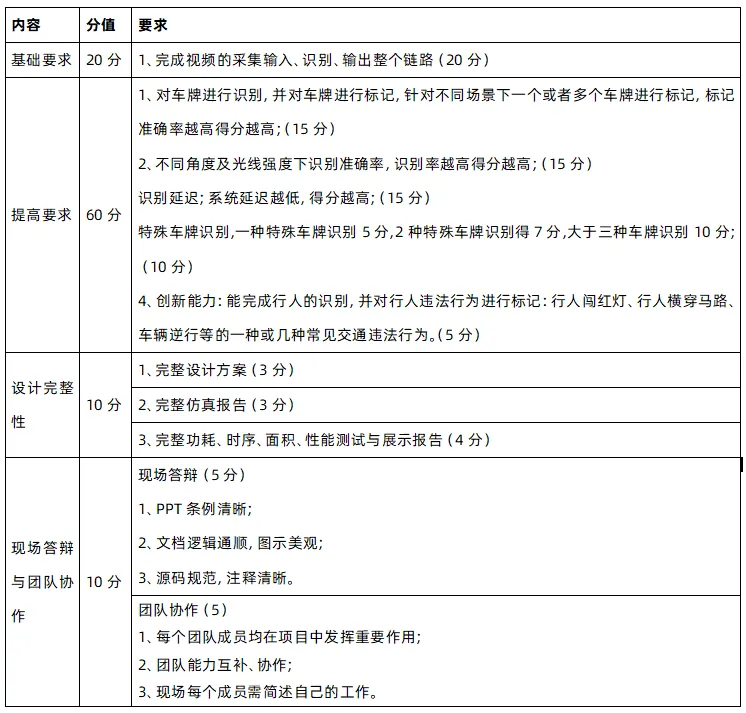

5、评分标准:

注:为保证赛事公平,初赛阶段命题方提供测试数据集仅用于调试,现场测评阶段提供新的测试数据集。

03/推荐板卡与外设

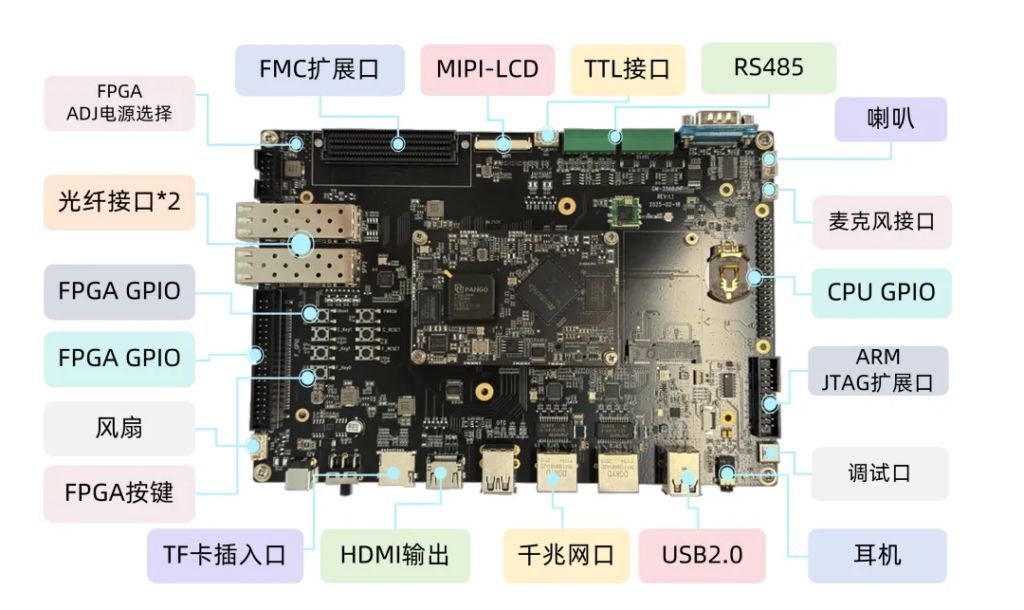

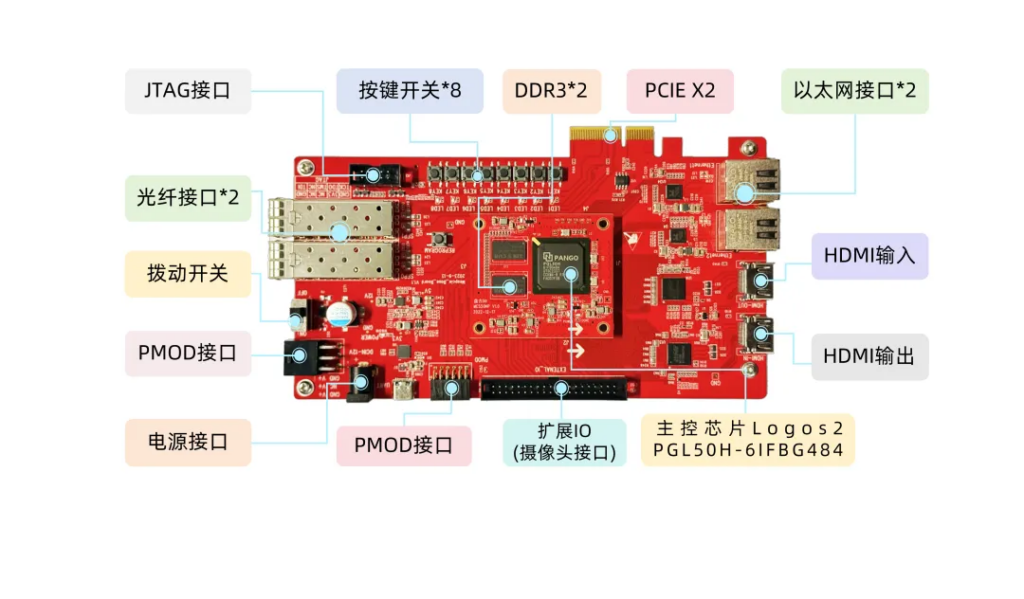

RK3568+PG2L50H/100H开发板

RK3568_MES2L50H核心板采用紫光创logos2系列FPGA,型号:PG2L50H-6IFBG484,ARM采用瑞芯微RK3568J。开发板采用核心板+扩展板结构,核心板与扩展板之间使用高速板对板连接器进行连接。核心板的FPGA部分主要由FPGA+1颗DDR3+2颗FLASH+电源及复位电路组成,承担了FPGA最小系统运行及高速数据处理及存储功能。

FPGA选用紫光同创28nm工艺FPGA(logos2:PG2L50H-6IFBG484/PG2L100H-6IFBG48);PG2L50H(PG2L100H)与DDR3数据交互时钟频率最高可达1066Mbps,DDR3数据位宽为16bit,因此数据带宽可达(1066Mbps*16),充分满足高速多路数据存储的需求;另外PG2L50H(PG2L100H)FPGA带有4路HSST高速收发器,每路速度高达6.6Gbps,非常适用于光纤通信与PCIe通信;核心板上的FLASH主要用于存储FPGA配置文件。

RK3568是一颗高性能、低功耗的四核应用处理器芯片,内置多种功能强大的嵌入式硬件引擎,为高端应用提供了优异的性能,工业级,工作温度范围为-40°C~85。底板为核心板扩展丰富的外围接口,其中包括两个光纤模块接口,FMC接口、40pin接口,并配置了按键、LED灯。

淘宝官方店铺购买链接:

https://item.taobao.com/item.htm?ft=t&id=921499086500

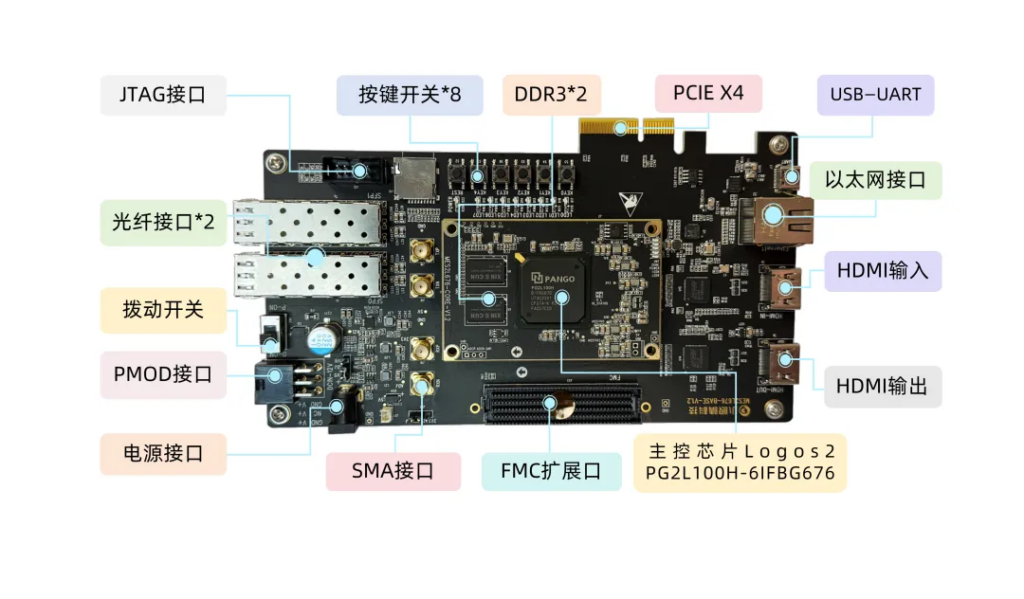

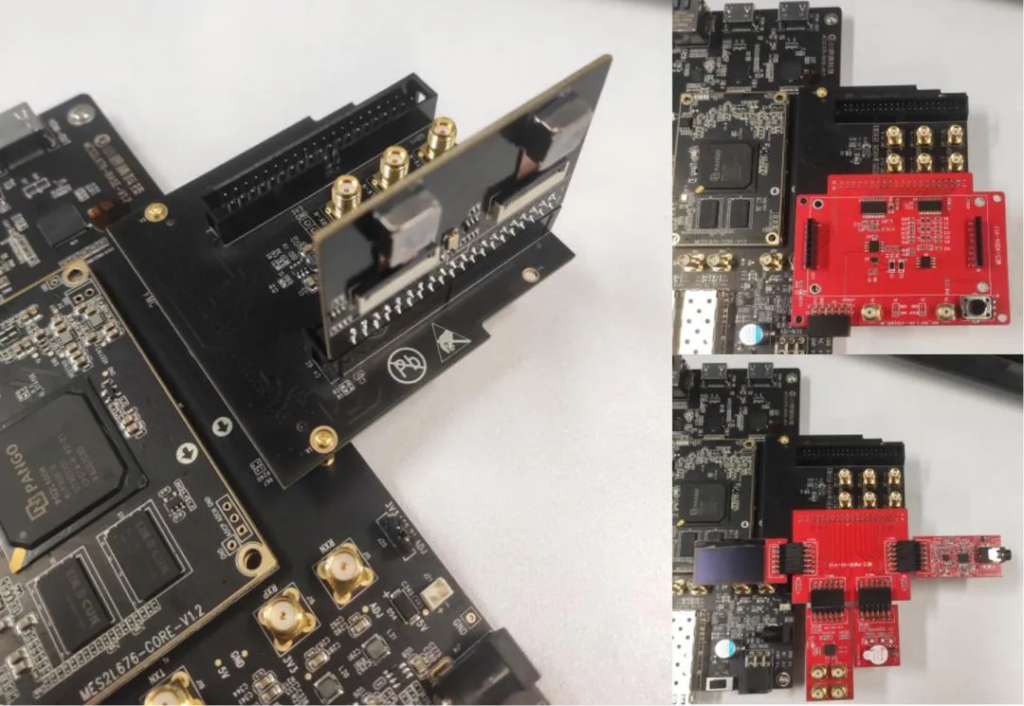

盘古676系列开发板

盘古676系列开发板(MES2L676,国产FPGA权威指南教材的配套板卡),共有2款板卡:支持100k和200k两种逻辑规模,主控分别为:Logos-2:PG2L100H-6IFBG676和PG2L200H-6IFBG676,底板兼容设计。板卡采用核心板+扩展底板的结构,核心板与扩展底板之间使用高速板间连接器进行连接。主控和DDR3之间的数据传输时钟频率最高为533 MHz,2颗DDR3的数据位宽为32 bit,总的数据带宽最高到34112 Mbps(1066×32=34112)。另外,MES2L676板卡带有8路HSSTLP高速串行收发器,每路的数据传输速率高达6.6 Gbps。MES2L676开发板预留了2路光纤接口、1路SMA高速收发接口、1路PCIe Gen2×4数据通信接口、1路HDMI发送接口、1路HDMI接收接口、1路10/100/1000 Mbps的以太网接口,以及1组FMC LPC扩展接口(符合FMC接口规范,可用于外接FMC模块)。

https://item.taobao.com/item.htm?ft=t&id=694482461265

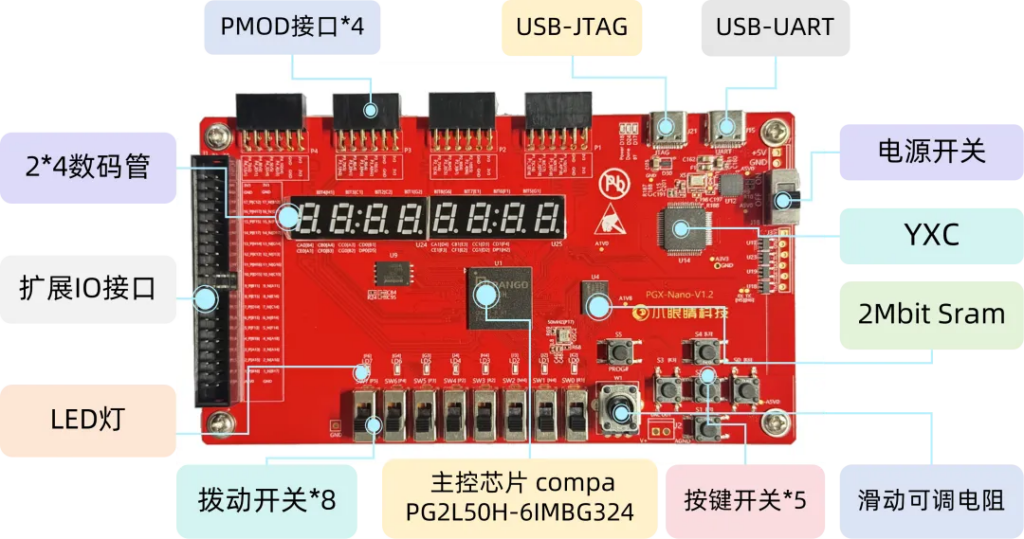

盘古50开发板(MES50HP)

https://item.taobao.com/item.htm?ft=t&id=775999245564

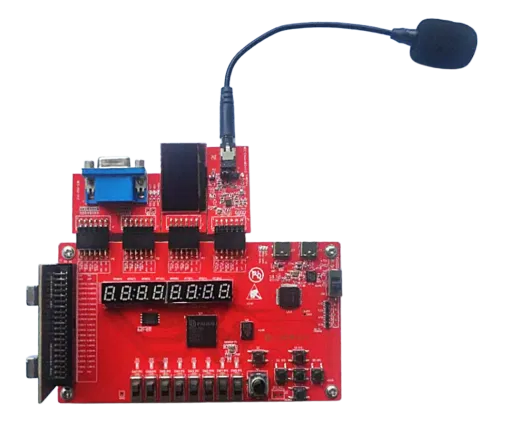

其他外设模块

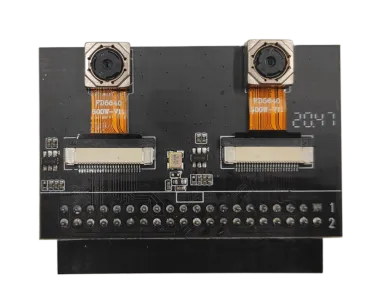

摄像头基于CMOS芯片图像传感器OV5640双目摄像头,通过DVP接口与FPGA实现图像的传输。

配套盘古676系列开发板,扩展40pin*2的IO,可接入双目摄像头及配套ADC模块。

淘宝官方店铺购买链接:

04/硬件支持与技术资源

2、企业将根据报名队伍的简介及对相应赛题的解题思路综合评判借用,未获得板卡借用资格的队伍不代表没有参赛资格,参赛者亦可自行到淘宝店铺购买:https://shop372525434.taobao.com/,提供报名成功凭证截图(完成提交盖章报名表及缴纳参赛押金),所有板卡及模组即可享受赛事折扣价格。

3、远程FPGA平台:没有获得板卡借用的队伍也可以远程登录线上开发平台进行开发和验证,参赛者根据远程平台实验结果提交作品进行初审,进入初赛现场或决赛现场,由赛方提供板卡或者实验箱平台进行作品验证。

远程平台链接(拟在3月左右开放):https://szlogicmatrix.com/

4、申请借用方案见本命题钉钉交流群。

5、Bilibili技术视频网址:https://space.bilibili.com/507416742

05/赛事福利-人才政策

2.全国二等奖和三等奖的同学可获得紫光同创FPGA开发岗位面试直通卡,免笔试直接进入技术及HR面试考核环节。

3.备注:享受大赛招聘政策成员,需获得各学校毕业证书和学位证书,本招聘政策自获得奖项之日起一年内有效,但受企业招聘需求情况约束。

没有回复内容